SBAS017A - NOVEMBER 1996 - REVISED MAY 2002

# **16-Bit 10μs Serial CMOS Sampling ANALOG-TO-DIGITAL CONVERTER**

### **FEATURES**

- 100kHz SAMPLING RATE

- 86dB SINAD WITH 20kHz INPUT

- ±2LSB INL

- DNL: 16 Bits "No Missing Codes"

- SIX SPECIFIED INPUT RANGES

- SERIAL OUTPUT

- SINGLE +5V SUPPLY OPERATION

- PIN-COMPATIBLE WITH 12-BIT ADS7808

- USES INTERNAL OR EXTERNAL REFERENCE

- 100mW MAX POWER DISSIPATION

- 20-PIN 0.3" PLASTIC DIP AND SO

- SIMPLE DSP INTERFACE

### DESCRIPTION

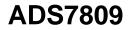

The ADS7809 is a complete 16-bit sampling Analog-to-Digital (A/D) converter using state-of-the-art CMOS structures. It contains a 16-bit capacitor-based Successive Approximation Register (SAR) A/D converter with sample-andhold, reference, clock, and a serial data interface. Data can be outputted using the internal clock, or can be synchronized to an external data clock. The ADS7809 also provides an output synchronization pulse for ease of use with standard DSP processors.

The ADS7809 is specified at a 100kHz sampling rate, and specified over the full temperature range. Laser-trimmed scaling resistors provide various input ranges including  $\pm$ 10V and 0V to 5V, while an innovative design operates from a single +5V supply, with power dissipation under 100mW.

The 20-pin ADS7809 is available in a plastic 0.3" DIP and in an SO, both fully specified for operation over the industrial  $-40^{\circ}$ C to  $+85^{\circ}$ C range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Analog Inputs: R1 <sub>IN</sub>         | ±25V                                |

|-----------------------------------------|-------------------------------------|

| R2 <sub>IN</sub>                        | ±25V                                |

| R3 <sub>IN</sub>                        | ±25V                                |

| CAP V <sub>AN</sub>                     | <sub>A</sub> + 0.3V to AGND2 - 0.3V |

| REF                                     | Indefinite Short to AGND2,          |

|                                         | Momentary Short to VANA             |

| Ground Voltage Differences: DGND, AGND2 | ±0.3V                               |

| V <sub>ANA</sub>                        | 7V                                  |

| V <sub>DIG</sub> to V <sub>ANA</sub>    |                                     |

| V <sub>DIG</sub>                        | 7V                                  |

| Digital Inputs                          |                                     |

| Maximum Junction Temperature            | +165°C                              |

| Internal Power Dissipation              |                                     |

| Lead Temperature (soldering, 10s)       | +300°C                              |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### PACKAGE/ORDERING INFORMATION

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT   | MAXIMUM<br>LINEARITY<br>ERROR (LSB) | NO MISSING<br>CODE LEVEL<br>(LSB) | MINIMUM<br>SIGNAL-TO-<br>(NOISE +<br>DISTORTION)<br>RATIO (dB) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|-----------|-------------------------------------|-----------------------------------|----------------------------------------------------------------|------------------|--------------------------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| ADS7809P  | ±3                                  | 15                                | 83                                                             | Plastic DIP-20   | N                                    | -40°C to +85°C                    | ADS7809P           | ADS7809P           | Rail, 19                     |

| ADS7809PB | ±2                                  | 16                                | 86                                                             | "                | "                                    | "                                 | ADS7809PB          | ADS7809PB          | "                            |

| ADS7809U  | ±3                                  | 15                                | 83                                                             | SO-20            | DW                                   | -40°C to +85°C                    | ADS7809U           | ADS7809U           | Rail, 38                     |

| ADS7809U  | "                                   | "                                 | "                                                              | "                | "                                    | "                                 | "                  | ADS7809U/1K        | Tape and Reel, 1000          |

| ADS7809UB | ±2                                  | 16                                | 86                                                             | "                | "                                    | "                                 | ADS7809UB          | ADS7809UB          | Rail, 38                     |

| ADS7809UB | "                                   | "                                 | "                                                              | n                | II                                   | н                                 | "                  | ADS7809UB/1K       | Tape and Reel, 1000          |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com.

## **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}C$  to +85°C,  $f_S = 100$ kHz,  $V_{DIG} = V_{ANA} = +5V$ , using internal reference and fixed resistors (see Figure 4), unless otherwise specified.

|                                     |                           | 4    | ADS7809P,  | U              | A      |        |       |                    |

|-------------------------------------|---------------------------|------|------------|----------------|--------|--------|-------|--------------------|

| PARAMETER                           | CONDITIONS                | MIN  | TYP        | MAX            | MIN    | ТҮР    | UNITS |                    |

| RESOLUTION                          |                           |      |            | 16             |        |        | *     | Bits               |

| ANALOG INPUT                        |                           |      |            |                |        |        |       |                    |

| Voltage Ranges                      |                           |      | ±10,       | 0V to 5V, e    |        | ble I) |       |                    |

| Impedance                           |                           |      |            | See T          | able I |        |       |                    |

| Capacitance                         |                           |      | 35         |                |        | *      |       | pF                 |

| THROUGHPUT SPEED                    |                           |      |            |                |        |        |       |                    |

| Complete Cycle                      | Acquire and Convert       |      |            | 10             |        |        | *     | μs                 |

| Throughput Rate                     |                           | 100  |            |                | *      |        |       | kHz                |

| DC ACCURACY                         |                           |      |            |                |        |        |       |                    |

| Integral Linearity Error            |                           |      |            | ±3             |        |        | ±2    | LSB <sup>(1)</sup> |

| Differential Linearity Error        |                           |      |            | +3, -2         |        |        | ±1    | LSB                |

| No Missing Codes                    |                           | 15   |            | , _            | 16     |        |       | Bits               |

| Transition Noise <sup>(2)</sup>     |                           |      | 1.3        |                |        | *      |       | LSB                |

| Full-Scale Error <sup>(3,4)</sup>   |                           |      |            | ±0.5           |        |        | *     | %                  |

| Full-Scale Error Drift              |                           |      | ±7         | 20.0           |        | *      |       | ppm/°C             |

| Full-Scale Error <sup>(3,4)</sup>   | Ext. 2.5000V Ref          |      |            | ±0.5           |        | ~      | *     | % ppm/             |

| Full-Scale Error Drift              | Ext. 2.5000V Ref          |      | ±2         | 10.0           |        | *      | , n   | ppm/°C             |

| Bipolar Zero Error <sup>(3)</sup>   | Bipolar Ranges            |      | <u> </u>   | ±10            |        | ~      | *     | mV                 |

| Bipolar Zero Error Drift            | Bipolar Ranges            |      | ±2         | 10             |        | *      |       | ppm/°C             |

| Unipolar Zero Error <sup>(3)</sup>  | 0V to 10V Ranges          |      | <u>±</u> 2 | ±5             |        | ~      | *     | mV                 |

| Unipolar Zero Error <sup>(3)</sup>  | 0V to 4V, 0V to 5V Ranges |      |            | ±3             |        |        | *     | mV                 |

|                                     |                           |      | +2         | ±3             |        | *      | *     |                    |

| Unipolar Zero Error Drift           | Unipolar Ranges           |      | ±2         |                |        | *      |       | ppm/°C             |

| Recovery to Rated Accuracy          | 1µF Capacitor to CAP      |      | 1          |                |        | *      |       | ms                 |

| after Power-Down                    |                           |      |            |                |        |        |       | 1.00               |

| Power-Supply Sensitivity            | $+4.75V < V_{D} < +5.25V$ |      |            | ±8             |        |        | *     | LSB                |

| $(V_{DIG} = V_{ANA} = V_D)$         |                           |      |            |                |        |        |       |                    |

| AC ACCURACY                         |                           |      |            |                |        |        |       |                    |

| Spurious-Free Dynamic Range         | $f_{IN} = 20 kHz$         | 90   | 100        |                | 96     | *      |       | dB <sup>(5)</sup>  |

| Total Harmonic Distortion           | $f_{IN} = 20 kHz$         |      | -100       | -90            |        | *      | -94   | dB                 |

| Signal-to-(Noise + Distortion)      | f <sub>IN</sub> = 20kHz   | 83   | 88         |                | 86     | *      |       | dB                 |

|                                     | -60dB Input               |      | 30         |                |        | 32     |       | dB                 |

| Signal-to-Noise                     | f <sub>IN</sub> = 20kHz   | 83   | 88         |                | 86     | *      |       | dB                 |

| Full-Power Bandwidth <sup>(6)</sup> |                           |      | 250        |                |        | *      |       | kHz                |

| SAMPLING DYNAMICS                   |                           |      |            |                |        |        |       |                    |

| Aperture Delay                      |                           |      | 40         |                |        | *      |       | ns                 |

| Transient Response                  | FS Step                   |      |            | 2              |        |        | *     | μs                 |

| Overvoltage Recovery <sup>(7)</sup> |                           |      | 150        |                |        | *      |       | ns                 |

| REFERENCE                           |                           |      |            |                |        |        |       |                    |

| Internal Reference Voltage          | No Load                   | 2.48 | 2.5        | 2.52           | *      | *      | *     | V                  |

| Internal Reference Source Current   |                           |      | 1          |                |        | *      |       | μΑ                 |

| (Must use external buffer)          |                           |      |            |                |        |        |       |                    |

| External Reference Voltage Range    |                           | 2.3  | 2.5        | 2.7            | *      | *      | *     | V                  |

| For Specified Linearity             |                           |      |            |                |        |        |       |                    |

| External Reference Current Drain    | Ext. 2.5000V Ref          |      |            | 100            |        |        | *     | μΑ                 |

| DIGITAL INPUTS                      |                           |      |            |                |        |        |       |                    |

| Logic Levels                        |                           |      |            |                |        |        |       |                    |

| V <sub>IL</sub>                     |                           | -0.3 |            | +0.8           | *      |        | *     | V                  |

| V <sub>IH</sub>                     |                           | +2.0 |            | $V_{D} + 0.3V$ | *      |        | *     | V                  |

| I <sub>IL</sub>                     | $V_{IL} = 0V$             |      |            | ±10            |        |        | *     | μΑ                 |

| I <sub>IH</sub>                     | $V_{IH} = 5V$             | 1    | 1          | ±10            |        |        | *     | μΑ                 |

### **ELECTRICAL CHARACTERISTICS (Cont.)**

At  $T_A = -40^{\circ}C$  to +85°C,  $f_S = 100$ kHz,  $V_{DIG} = V_{ANA} = +5V$ , using internal reference and fixed resistors as shown in Figure 4, unless otherwise specified.

|                                      |                                                  | ۵       | ADS7809P, U  |              |              | ADS7809PB, UB |           |       |  |

|--------------------------------------|--------------------------------------------------|---------|--------------|--------------|--------------|---------------|-----------|-------|--|

| PARAMETER                            | CONDITIONS                                       | MIN     | TYP          | MAX          | MIN          | ТҮР           | MAX       | UNITS |  |

| DIGITAL OUTPUTS                      |                                                  |         |              |              |              |               |           |       |  |

| Data Format                          |                                                  |         |              | Serial       | 16 bits      |               |           |       |  |

| Data Co                              |                                                  |         | Binary Two   | o's Complei  | ment or Stra | aight Binary  |           |       |  |

| Pipeline Delay                       |                                                  | Convers | sion results | only availa  | ble after co | mpleted cor   | nversion. |       |  |

| Data Clock                           |                                                  |         | Selectable   | for internal | or external  | data clock    |           |       |  |

| Internal                             | EXT/INT LOW                                      |         | 2.3          |              |              | *             |           | MHz   |  |

| (Output Only When                    |                                                  |         |              |              |              |               |           |       |  |

| Transmitting Data)                   |                                                  |         |              |              |              |               |           |       |  |

| External                             | EXT/INT HIGH                                     | 0.1     |              | 10           | *            |               | *         | MHz   |  |

| (Can Run Continually)                |                                                  |         |              |              |              |               |           |       |  |

| V <sub>OL</sub>                      | I <sub>SINK</sub> = 1.6mA                        |         |              | +0.4         |              |               | *         | V     |  |

| V <sub>OH</sub>                      | $I_{SOURCE} = 500 \mu A$                         | +4      |              |              | *            |               |           | V     |  |

| Leakage Current                      | High-Z State,                                    |         |              | ±5           |              |               | *         | μA    |  |

| _                                    | $V_{OUT} = 0V$ to $V_{DIG}$                      |         |              |              |              |               |           |       |  |

| Output Capacitance                   | High-Z State                                     |         |              | 15           |              |               | *         | pF    |  |

| POWER SUPPLIES                       |                                                  |         |              |              |              |               |           |       |  |

| Specified Performance                |                                                  |         |              |              |              |               |           |       |  |

| V <sub>DIG</sub>                     | Must be ≤ V <sub>ANA</sub>                       | +4.75   | +5           | +5.25        | *            | *             | *         | V     |  |

| V <sub>ANA</sub>                     |                                                  | +4.75   | +5           | +5.25        | *            | *             | *         | V     |  |

| I <sub>DIG</sub>                     |                                                  |         | 0.3          |              |              | *             |           | mA    |  |

| I <sub>ANA</sub>                     |                                                  |         | 16           |              |              | *             |           | mA    |  |

| Power Dissipation: PWRD LOW          | $V_{ANA} = V_{DIG} = 5V, f_{S} = 100 \text{kHz}$ |         |              | 100          |              |               | *         | mW    |  |

| PWRD HIGH                            |                                                  |         | 50           |              |              | *             |           | μW    |  |

| TEMPERATURE RANGE                    |                                                  |         |              |              |              |               |           |       |  |

| Specified Performance                |                                                  | -40     |              | +85          | *            |               | *         | °C    |  |

| Derated Performance                  |                                                  | -55     |              | +125         | *            |               | *         | °C    |  |

| Storage                              |                                                  | -65     |              | +150         | *            |               | *         | °C    |  |

| Thermal Resistance ( $\theta_{JA}$ ) |                                                  |         |              |              |              |               |           |       |  |

| DIP                                  |                                                  |         | 75           |              |              | *             |           | °C/W  |  |

| SO                                   |                                                  |         | 75           |              |              | *             |           | °C/W  |  |

\* Same as specification for ADS7809P, U.

NOTES: (1) LSB means Least Significant Bit. For the  $\pm 10V$  input range, one LSB is  $305\mu V$ . (2) Typical rms noise at worst case transitions and temperatures. (3) As measured with fixed resistors shown in Figure 4. Adjustable to zero with external potentiometer. (4) For bipolar input ranges, full-scale error is the worst case of –Full Scale or +Full Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error. For unipolar input ranges, full-scale error is the deviation of the last code transition divided by the transition voltage. It also includes the effect of offset error. (5) All specifications in dB are referred to a full-scale  $\pm 10V$  input. (6) Full-Power Bandwidth defined as Full-Scale input frequency at which Signal-to-(Noise + Distortion) degrades to 60dB. (7) Recovers to specified performance after 2 • FS input overvoltage.

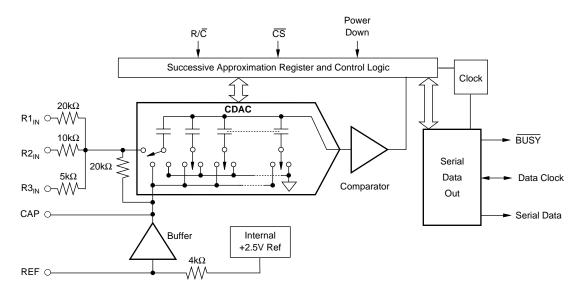

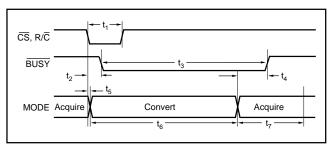

#### **PIN ASSIGNMENTS**

| PIN # | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | R1 <sub>IN</sub> | Analog Input. See Table I and Figure 4 for input range connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2     | AGND1            | Analog Ground. Used internally as ground reference point. Minimal current flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3     | R2 <sub>IN</sub> | Analog Input. See Table I and Figure 4 for input range connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4     | R3 <sub>IN</sub> | Analog Input. See Table I and Figure 4 for input range connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5     | CAP              | Reference Buffer Capacitor. 2.2µF Tantalum to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6     | REF              | Reference Input/Output. Outputs internal 2.5V reference. Can also be driven by external system reference. In both cases, bypass to ground with a 2.2μF Tantalum capacitor.                                                                                                                                                                                                                                                                                                                                                     |

| 7     | AGND2            | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8     | SB/BTC           | Select Straight Binary or Binary Two's Complement data output format. If HIGH, data will be output in a Straight Binary format. If LOW, data will be output in a Binary Two's Complement format.                                                                                                                                                                                                                                                                                                                               |

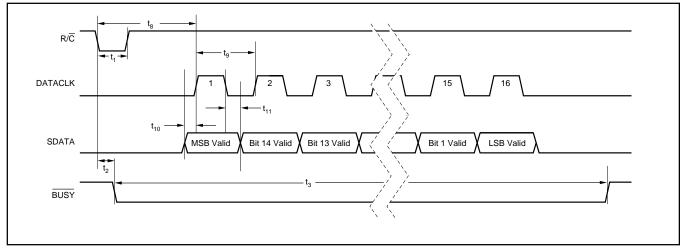

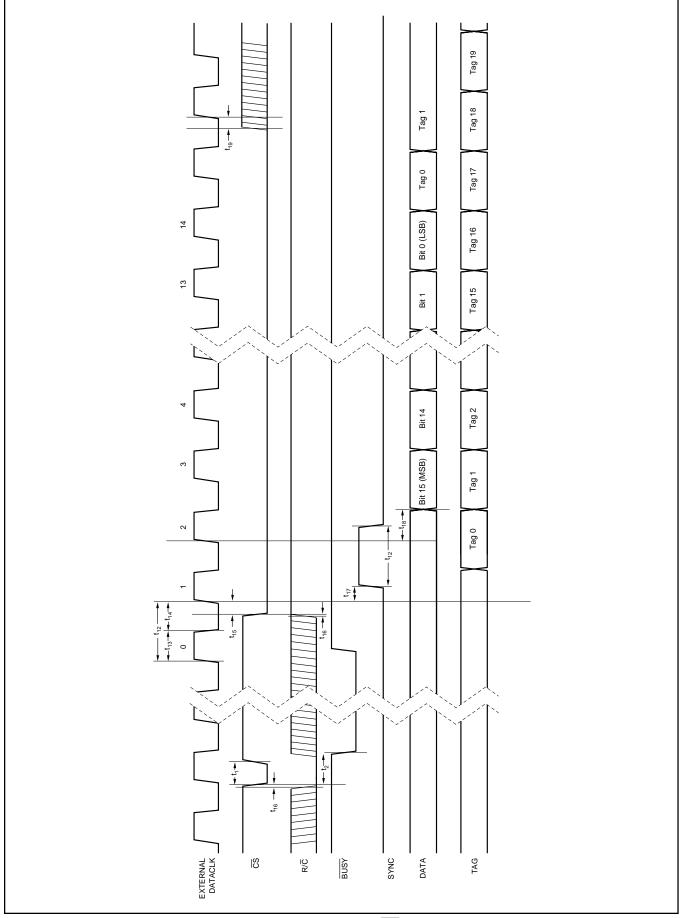

| 9     | EXT/INT          | Select External or Internal Clock for transmitting data. If HIGH, data will be output synchronized to the clock input on DATACLK. If LOW, a convert command will initiate the transmission of the data from the previous conversion, along with 16 clock pulses output on DATACLK.                                                                                                                                                                                                                                             |

| 10    | DGND             | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11    | SYNC             | Synch Output. If EXT/INT is HIGH, either a rising edge on R/C with CS LOW or a falling edge on CS with R/C HIGH will output a pulse on SYNC synchronized to the external DATACLK.                                                                                                                                                                                                                                                                                                                                              |

| 12    | DATACLK          | Either an input or an output depending on the EXT/INT level. Output data will be synchronized to this clock. If EXT/INT is LOW, DATACLK will transmit 16 pulses after each conversion, and then remain LOW between conversions.                                                                                                                                                                                                                                                                                                |

| 13    | DATA             | Serial Data Output. Data will be synchronized to DATACLK, with the format determined by the level of SB/ $\overline{BTC}$ . In the external clock mode, after 16 bits of data, the ADS7809 will output the level input on TAG as long as $\overline{CS}$ is LOW and R/ $\overline{C}$ is HIGH (see Figure 3). If EXT/INT is LOW, data will be valid on both the rising and falling edges of DATACLK, and between conversions DATA will stay at the level of the TAG input when the conversion was started.                     |

| 14    | TAG              | Tag Input for use in external clock mode. If EXT/INT is HIGH, digital data input on TAG will be output on DATA with a delay of 16 DATACLK pulses as long as CS is LOW and R/C is HIGH. See Figure 3.                                                                                                                                                                                                                                                                                                                           |

| 15    | R/Ċ              | Read/Convert Input. With $\overline{CS}$ LOW, a falling edge on R/ $\overline{C}$ puts the internal sample-and-hold into the hold state and starts a conversion. When EXT/INT is LOW, this also initiates the transmission of the data results from the previous conversion. If EXT/INT is HIGH, a rising edge on R/ $\overline{C}$ with $\overline{CS}$ LOW, or a falling edge on $\overline{CS}$ with R/ $\overline{C}$ HIGH, transmits a pulse on SYNC and initiates the transmission of data from the previous conversion. |

| 16    | CS               | Chip Select. Internally OR'ed with $R/\overline{C}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17    | BUSY             | Busy Output. Falls when a conversion is started, and remains LOW until the conversion is completed and the data is latched into the output shift register. $\overline{\text{CS}}$ or R/ $\overline{\text{C}}$ must be HIGH when $\overline{\text{BUSY}}$ rises, or another conversion will start without time for signal acquisition.                                                                                                                                                                                          |

| 18    | PWRD             | Power Down Input. If HIGH, conversions are inhibited and power consumption is significantly reduced. Results from the previous conversion are maintained in the output shift register.                                                                                                                                                                                                                                                                                                                                         |

| 19    | V <sub>ANA</sub> | Analog Supply Input. Nominally +5V. Connect directly to pin 20, and decouple to ground with 0.1µF ceramic and 10µF tantalum capacitors.                                                                                                                                                                                                                                                                                                                                                                                        |

| 20    | $V_{\text{DIG}}$ | Digital Supply Input. Nominally +5V. Connect directly to pin 19. Must be $\leq V_{ANA}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **PIN CONFIGURATION**

| ANALOG<br>INPUT<br>RANGE | $\begin{array}{c} \text{CONNECT R1}_{\text{IN}} \\ \text{VIA 200} \Omega \\ \text{TO} \end{array}$ | $\begin{array}{c} \text{CONNECT R2}_{\text{IN}} \\ \text{VIA } 100\Omega \\ \text{TO} \end{array}$ | CONNECT R3 <sub>IN</sub><br>TO | IMPEDANCE |

|--------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------|-----------|

| ±10V                     | V <sub>IN</sub>                                                                                    | AGND                                                                                               | CAP                            | 22.9kΩ    |

| ±5V                      | AGND                                                                                               | V <sub>IN</sub>                                                                                    | CAP                            | 13.3kΩ    |

| ±3.33V                   | V <sub>IN</sub>                                                                                    | V <sub>IN</sub>                                                                                    | CAP                            | 10.7kΩ    |

| 0V to 10V                | AGND                                                                                               | V <sub>IN</sub>                                                                                    | AGND                           | 13.3kΩ    |

| 0V to 5V                 | AGND                                                                                               | AGND                                                                                               | V <sub>IN</sub>                | 10.0kΩ    |

| 0V to 4V                 | V <sub>IN</sub>                                                                                    | AGND                                                                                               | V <sub>IN</sub>                | 10.7kΩ    |

TABLE I. Input Range Connections. See Figure 4 for complete information.

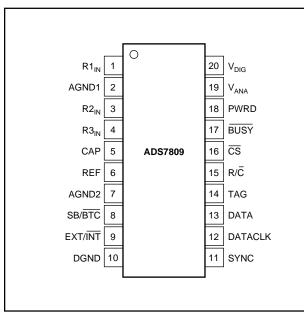

| SYMBOL          | DESCRIPTION                                    | MIN | ТҮР | МАХ                 | UNITS |

|-----------------|------------------------------------------------|-----|-----|---------------------|-------|

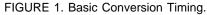

| t <sub>1</sub>  | Convert Pulse Width                            | 40  |     | 6000                | ns    |

| t <sub>2</sub>  | BUSY Delay                                     |     |     | 65                  | ns    |

| t <sub>3</sub>  | BUSY LOW                                       |     |     | 8                   | μs    |

| t <sub>4</sub>  | BUSY Delay After End of Conversion             |     | 220 |                     | ns    |

| t <sub>5</sub>  | Aperture Delay                                 |     | 40  |                     | ns    |

| t <sub>6</sub>  | Conversion Time                                |     | 7.6 | 8                   | μs    |

| t <sub>7</sub>  | Acquisition Time                               |     |     | 2                   | μs    |

| $t_{6} + t_{7}$ | Throughput Time                                |     | 9   | 10                  | μs    |

| t <sub>8</sub>  | R/C LOW to DATACLK Delay                       |     | 450 |                     | ns    |

| t <sub>9</sub>  | DATACLK Period                                 |     | 440 |                     | ns    |

| t <sub>10</sub> | Data Valid to DATACLK HIGH Delay               | 20  | 75  |                     | ns    |

| t <sub>11</sub> | Data Valid After DATACLK LOW Delay             | 100 | 125 |                     | ns    |

| t <sub>12</sub> | External DATACLK                               | 100 |     |                     | ns    |

| t <sub>13</sub> | External DATACLK HIGH                          | 20  |     |                     | ns    |

| t <sub>14</sub> | External DATACLK LOW                           | 30  |     |                     | ns    |

| t <sub>15</sub> | DATACLK HIGH Setup Time                        | 20  |     | t <sub>12</sub> + 5 | ns    |

| t <sub>16</sub> | $R/\overline{C}$ to $\overline{CS}$ Setup Time | 10  |     |                     | ns    |

| t <sub>17</sub> | SYNC Delay After DATACLK HIGH                  | 15  |     | 35                  | ns    |

| t <sub>18</sub> | Data Valid Delay                               | 25  |     | 55                  | ns    |

| t <sub>19</sub> | CS to Rising Edge Delay                        | 25  |     |                     | ns    |

| t <sub>20</sub> | Data Available after $\overline{CS}$ LOW       | 6   |     |                     | μs    |

TABLE II. Conversion and Data Timing.  $T_A = -40^{\circ}C$  to +85°C.

FIGURE 2. Serial Data Timing Using Internal Clock. (CS, EXT/INT and TAG Tied LOW.)

| SPECIFIC FUNCTION                                              | cs    | R/C   | BUSY  | EXT/INT | DATACLK | PWRD | SB/BTC | OPERATION                                                                                                                                                 |

|----------------------------------------------------------------|-------|-------|-------|---------|---------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initiate Conversion and<br>Output Data Using<br>Internal Clock | 1 > 0 | 0     | 1     | 0       | Output  | 0    | x      | Initiates conversion "n". Data from conversion "n – 1" clocked out on DATA synchronized to 16 clock pulses output on DATACLK.                             |

|                                                                | 0     | 1 > 0 | 1     | 0       | Output  | 0    | x      | Initiates conversion "n". Data from conversion "n $-$ 1" clocked out on DATA synchronized to 16 clock pulses output on DATACLK.                           |

| Initiate Conversion and                                        | 1 > 0 | 0     | 1     | 1       | Input   | 0    | x      | Initiates conversion "n".                                                                                                                                 |

| Output Data Using External                                     | 0     | 1 > 0 | 1     | 1       | Input   | 0    | x      | Initiates conversion "n".                                                                                                                                 |

| Clock                                                          | 1 > 0 | 1     | 1     | 1       | Input   | x    | x      | Outputs a pulse on SYNC followed by data from<br>conversion "n" clocked out synchronized to external<br>DATACLK.                                          |

|                                                                | 1 > 0 | 1     | 0     | 1       | Input   | 0    | x      | Outputs a pulse on SYNC followed by data from conversion "n – 1" clocked out synchronized to external DATACLK. <sup>(1)</sup> Conversion "n" in process.  |

|                                                                | 0     | 0 > 1 | 0     | 1       | Input   | 0    | x      | Outputs a pulse on SYNC followed by data from conversion "n – 1" clocked out synchronized to external DATACLK . <sup>(1)</sup> Conversion "n" in process. |

| Incorrect Conversions                                          | 0     | 0     | 0 > 1 | x       | x       | 0    | x      | $\overline{CS}$ or R/ $\overline{C}$ must be HIGH or a new conversion will be initiated without time for acquisition.                                     |

| Power-Down                                                     | х     | x     | х     | х       | х       | 0    | х      | Analog circuitry powered. Conversion can proceed.                                                                                                         |

|                                                                | x     | x     | x     | x       | x       | 1    | x      | Analog circuitry disabled. Data from previous<br>conversion maintained in output registers.                                                               |

| Selecting Output Format                                        | x     | x     | x     | x       | x       | х    | 0      | Serial data is output in Binary Two's Complement format.                                                                                                  |

|                                                                | x     | x     | x     | x       | x       | x    | 1      | Serial data is output in Straight Binary format.                                                                                                          |

TABLE III. Control Truth Table.

|                             |           |           |            |           |           | DIGITAL OUTPUT |                                   |             |                               |      |  |  |

|-----------------------------|-----------|-----------|------------|-----------|-----------|----------------|-----------------------------------|-------------|-------------------------------|------|--|--|

|                             |           |           |            |           |           |                | BINARY TWO'S COMP<br>(SB/BTC LOW) |             | STRAIGHT BINA<br>(SB/BTC HIGH |      |  |  |

| DESCRIPTION                 |           | AN        |            | JT        |           | BINARY CODE    | HEX<br>CODE                       | BINARY CODE | HEX<br>CODE                   |      |  |  |

| Full-Scale Range            | ±10       | ±5        | ±3.33V     | 0V to 10V | 0V to 5V  | 0V to 4V       |                                   |             |                               |      |  |  |

| Least Significant Bit (LSB) | 305µV     | 153µV     | 102µV      | 153µV     | 76µV      | 61µV           |                                   |             |                               |      |  |  |

| +Full Scale (FS – 1LSB)     | 9.999695V | 4.999847V | 3.333231V  | 9.999847V | 4.999924V | 3.999939V      | 0111 1111 1111 1111               | 7FFF        | 1111 1111 1111 1111           | FFFF |  |  |

| Midscale                    | 0V        | 0V        | 0V         | 5V        | 2.5V      | 2V             | 0000 0000 0000 0000               | 0000        | 1000 0000 0000 0000           | 8000 |  |  |

| One LSB Below Midscale      | –305μV    | –153μV    | -102μV     | 4.999847V | 2.499924V | 1.999939V      | 1111 1111 1111 1111               | FFFF        | 0111 1111 1111 1111           | 7FFF |  |  |

| -Full Scale                 | -10V      | –5V       | -3.333333V | 0V        | 0V        | 0V             | 1000 0000 0000 0000               | 8000        | 0000 0000 0000 0000           | 0000 |  |  |

TABLE IV. Output Codes and Ideal Input Voltages.

8

ADS7809

SBAS017A

9

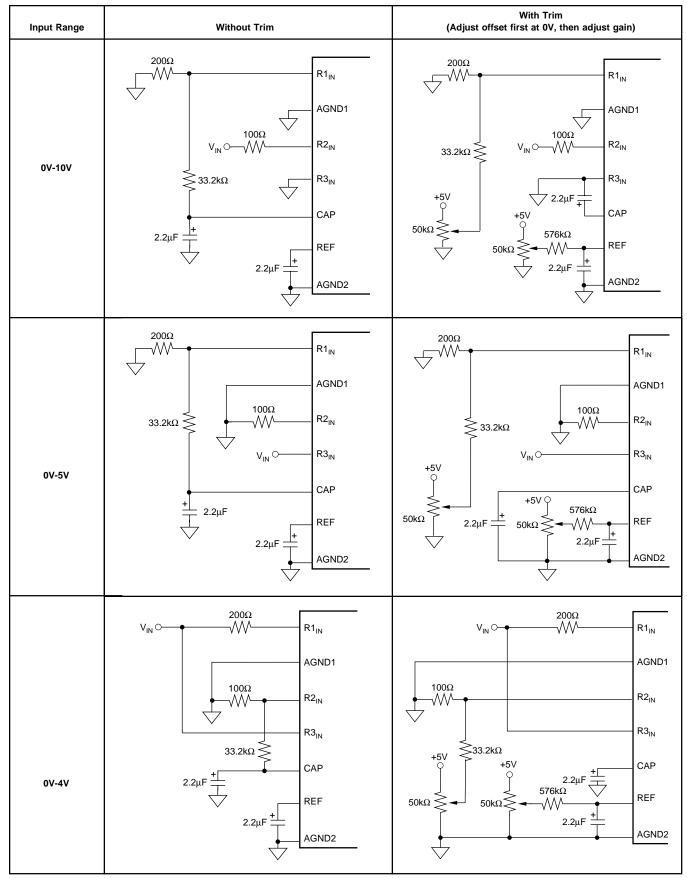

FIGURE 4a. Offset/Gain Circuits for Unipolar Input Ranges.

10

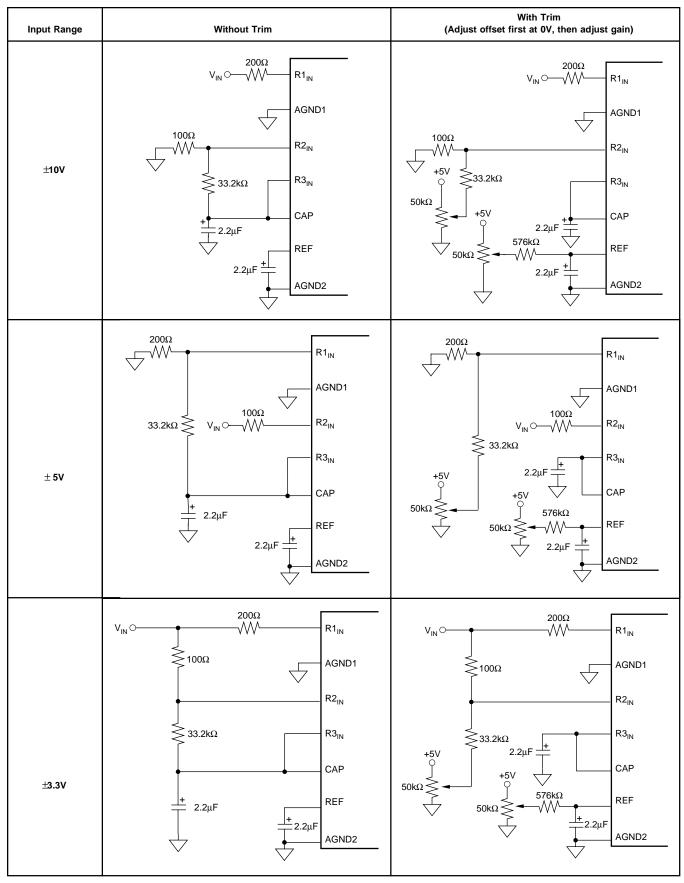

FIGURE 4b. Offset/Gain Circuits for Bipolar Input Ranges.

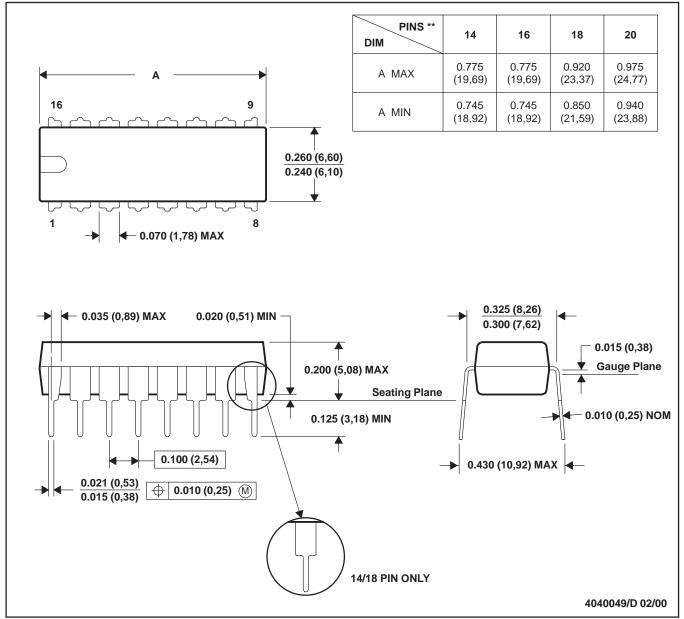

#### N (R-PDIP-T\*\*)

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20-pin package is shorter than MS-001).

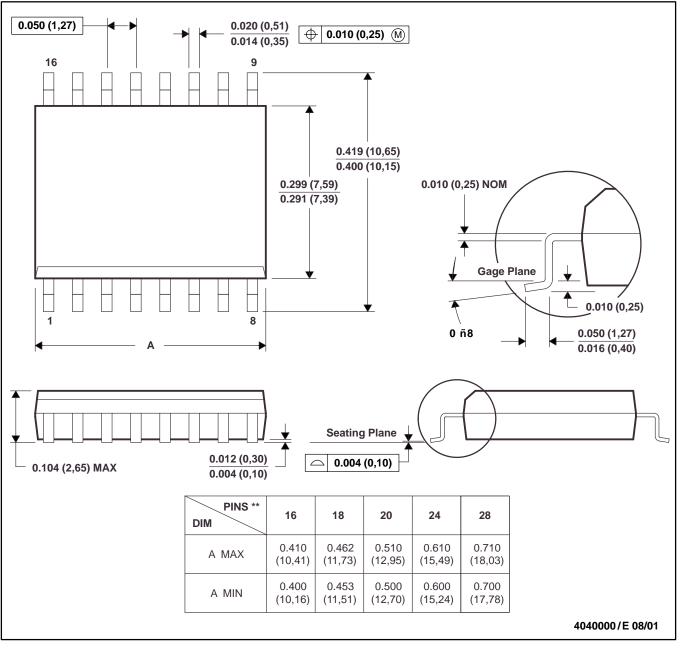

#### DW (R-PDSO-G\*\*) 16 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated