## NAND04G-B2D, NAND08G-BxC

4 Gbit, 8 Gbit, 2112 byte/1056 word page multiplane architecture, 1.8 V or 3 V, NAND Flash memories

Preliminary Data

#### **Features**

- High density NAND Flash Memory

- Up to 8 Gbit memory array

- Cost-effective solution for mass storage applications

- NAND interface

- x8 or 16x bus width

- Multiplexed address/data

- Supply voltage: 1.8 V or 3.0 V device

- Page size

- x8 device: (2048 + 64 spare) bytes

- x16 device: (1024 + 32 spare) words

- Block size

- x8 device: (128K + 4 K spare) bytes

- x16 device: (64K + 2 K spare) words

- Multiplane architecture

- Array split into two independent planes

- Program/erase operations can be performed on both planes at the same time

- Page read/program

- Random access: 25 µs (max)

- Sequential access: 25 ns (min)

- Page program time: 200 µs (typ)

- Multiplane page program time (2 pages): 200 µs (typ)

- Copy back program with automatic error detection code (EDC)

- Cache read mode

- Fast block erase

- Block erase time: 1.5 ms (typ)

- Multiblock erase time (2 blocks):

1.5 ms (typ)

- Status Register

- Electronic signature

- Chip Enable 'don't care'

- Serial number option

- Data protection:

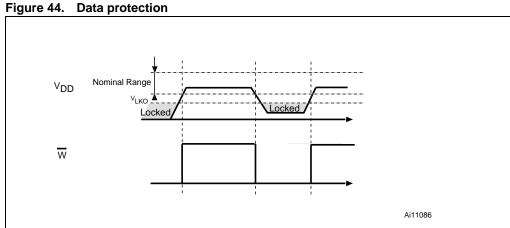

- Hardware program/erase disabled during power transitions

- Non-volatile protection option

- ONFI 1.0 compliant command set

- Data integrity

- 100 000 program/erase cycles (with ECC (error correction code))

- 10 years data retention

- ECOPACK<sup>®</sup> packages

Table 1. Device Summary

| Reference Part number |                             |  |  |  |  |

|-----------------------|-----------------------------|--|--|--|--|

|                       | NAND04GR3B2D                |  |  |  |  |

| NAND04G-B2D           | NAND04GW3B2D                |  |  |  |  |

| NANDU4G-B2D           | NAND04GR4B2D <sup>(1)</sup> |  |  |  |  |

|                       | NAND04GW4B2D <sup>(1)</sup> |  |  |  |  |

|                       | NAND08GR3B2C,               |  |  |  |  |

|                       | NAND08GW3B2C                |  |  |  |  |

| NAND08G-BxC           | NAND08GR4B2C <sup>(1)</sup> |  |  |  |  |

| NANDOOG-BAC           | NAND08GW4B2C <sup>(1)</sup> |  |  |  |  |

|                       | NAND08GR3B4C                |  |  |  |  |

|                       | NAND08GW3B4C                |  |  |  |  |

<sup>1.</sup> x16 organization only available for MCP products.

September 2007 Rev 2 1/69

# **Contents**

| 1 | Descr                     | escription                     |   |  |  |  |  |  |  |  |

|---|---------------------------|--------------------------------|---|--|--|--|--|--|--|--|

| 2 | Memory array organization |                                |   |  |  |  |  |  |  |  |

| 3 | Signal descriptions       |                                |   |  |  |  |  |  |  |  |

|   | 3.1                       | Inputs/outputs (I/O0-I/O7)     | 6 |  |  |  |  |  |  |  |

|   | 3.2                       | Inputs/Outputs (I/O8-I/O15)    | 6 |  |  |  |  |  |  |  |

|   | 3.3                       | Address Latch Enable (AL) 10   | 6 |  |  |  |  |  |  |  |

|   | 3.4                       | Command Latch Enable (CL)      | 6 |  |  |  |  |  |  |  |

|   | 3.5                       | Chip Enable (E)                | 6 |  |  |  |  |  |  |  |

|   | 3.6                       | Read Enable (R)                | 6 |  |  |  |  |  |  |  |

|   | 3.7                       | Write Enable (W)               | 7 |  |  |  |  |  |  |  |

|   | 3.8                       | Write Protect (WP)             | 7 |  |  |  |  |  |  |  |

|   | 3.9                       | Ready/Busy (RB)                | 7 |  |  |  |  |  |  |  |

|   | 3.10                      | V <sub>DD</sub> supply voltage | 7 |  |  |  |  |  |  |  |

|   | 3.11                      | V <sub>SS</sub> ground         | 7 |  |  |  |  |  |  |  |

| 4 | Bus operations            |                                |   |  |  |  |  |  |  |  |

|   | 4.1                       | Command input                  | 8 |  |  |  |  |  |  |  |

|   | 4.2                       | Address input                  | 8 |  |  |  |  |  |  |  |

|   | 4.3                       | Data input                     | 8 |  |  |  |  |  |  |  |

|   | 4.4                       | Data output                    | 8 |  |  |  |  |  |  |  |

|   | 4.5                       | Write protect                  | 9 |  |  |  |  |  |  |  |

|   | 4.6                       | Standby                        | 9 |  |  |  |  |  |  |  |

| 5 | Comn                      | nand set                       | 1 |  |  |  |  |  |  |  |

| 6 | Device operations         |                                |   |  |  |  |  |  |  |  |

|   | 6.1                       | Read memory array 22           | 2 |  |  |  |  |  |  |  |

|   |                           | 6.1.1 Random read              | 2 |  |  |  |  |  |  |  |

|   |                           | 6.1.2 Page read                | 2 |  |  |  |  |  |  |  |

|   | 6.2                       | Cache read                     | 4 |  |  |  |  |  |  |  |

|   |                           |                                |   |  |  |  |  |  |  |  |

**577**

|    | 6.3   | Page p   | orogram                                         | 26 |

|----|-------|----------|-------------------------------------------------|----|

|    |       | 6.3.1    | Sequential input                                | 26 |

|    |       | 6.3.2    | Random data input in page                       | 26 |

|    | 6.4   | Multipl  | ane page program                                | 28 |

|    | 6.5   | Copy b   | pack program                                    | 29 |

|    | 6.6   | Multipl  | ane copy back program                           | 30 |

|    | 6.7   | Block 6  | erase                                           | 31 |

|    | 6.8   | Multipl  | ane block erase                                 | 32 |

|    | 6.9   | Error d  | detection code (EDC)                            | 32 |

|    | 6.10  | Reset    |                                                 | 33 |

|    | 6.11  | Read S   | Status Register                                 | 34 |

|    |       | 6.11.1   | Write protection bit (SR7)                      |    |

|    |       | 6.11.2   | P/E/R Controller and cache ready/busy bit (SR6) | 34 |

|    |       | 6.11.3   | P/E/R Controller bit (SR5)                      | 34 |

|    |       | 6.11.4   | Error bit (SR0)                                 | 34 |

|    |       | 6.11.5   | SR4, SR3, SR2 and SR1 are reserved              | 35 |

|    | 6.12  | Reads    | status enhanced                                 | 35 |

|    | 6.13  | Read E   | EDC Status Register                             | 35 |

|    | 6.14  | Read 6   | electronic signature                            | 36 |

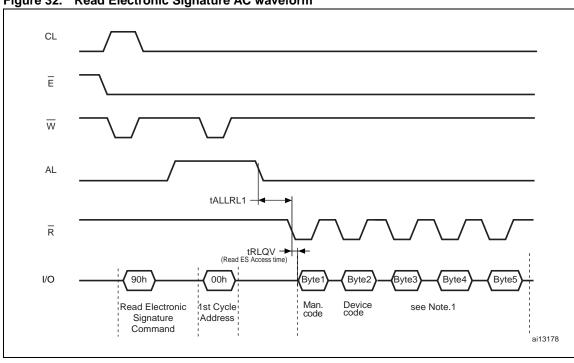

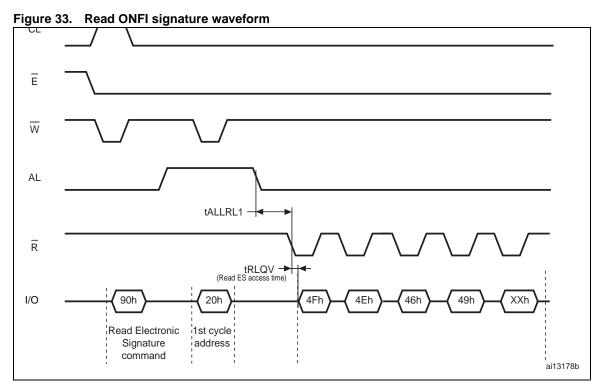

|    | 6.15  | Read (   | ONFI signature                                  | 39 |

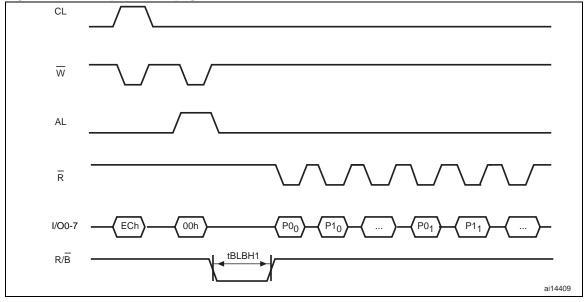

|    | 6.16  | Read p   | parameter page                                  | 39 |

| 7  | Cond  | current  | operations and extended read status             | 43 |

| 8  | Data  | protect  | tion                                            | 43 |

| 9  | Softv | ware alç | gorithms                                        | 44 |

|    | 9.1   | Bad blo  | ock management                                  | 44 |

|    | 9.2   | NAND     | Flash memory failure modes                      | 45 |

|    | 9.3   | Garba    | ge collection                                   | 46 |

|    | 9.4   | Wear-I   | eveling algorithm                               | 46 |

|    | 9.5   | Error c  | correction code                                 | 47 |

| 10 | Prog  | ram an   | d erase times and endurance cycles              | 48 |

**57**

7

| Contents |      |                                              | NAND04G-B2D, NAND08G-BxC |

|----------|------|----------------------------------------------|--------------------------|

| 11       | Maxi | mum ratings                                  | 49                       |

| 12       | DC a | nd AC parameters                             | 50                       |

|          | 12.1 | Ready/Busy signal electrical characteristics | s 63                     |

|          | 12.2 | Data protection                              | 64                       |

| 13       | Pack | age mechanical                               | 65                       |

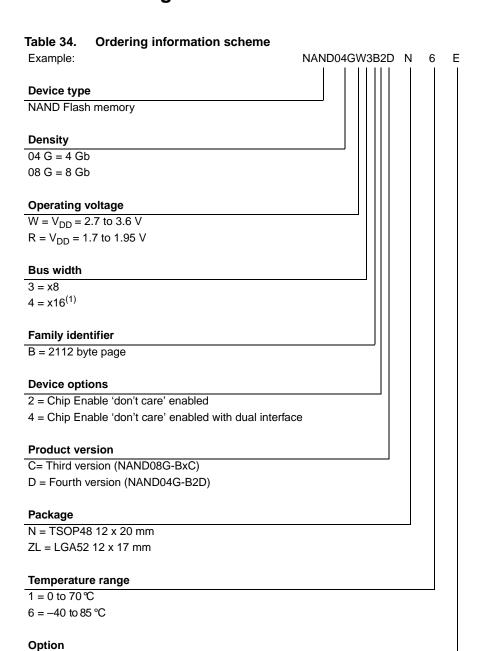

| 14       | Part | numbering                                    | 67                       |

| 15       | Revi | sion history                                 |                          |

# List of tables

| Table 1.  | Device Summary                                                                   | 1  |

|-----------|----------------------------------------------------------------------------------|----|

| Table 2.  | Product description                                                              | 8  |

| Table 3.  | Signal names                                                                     | 10 |

| Table 4.  | Valid Blocks                                                                     | 14 |

| Table 5.  | Bus operations                                                                   | 19 |

| Table 6.  | Address insertion (x8 devices)                                                   | 19 |

| Table 7.  | Address insertion (x16 devices)                                                  | 20 |

| Table 8.  | Address definition (x8 devices)                                                  | 20 |

| Table 9.  | Address definition (x16 devices)                                                 | 20 |

| Table 10. | Commands                                                                         |    |

| Table 11. | Copy back program addresses                                                      | 29 |

| Table 12. | Address definition for EDC units (x8 devices)                                    |    |

| Table 13. | Address definition for EDC units (x16 devices)                                   | 33 |

| Table 14. | Status Register bits                                                             | 35 |

| Table 15. | EDC Status Register bits                                                         | 36 |

| Table 16. | Electronic signature                                                             |    |

| Table 17. | Electronic signature byte 3                                                      | 37 |

| Table 18. | Electronic signature byte 4                                                      |    |

| Table 19. | Electronic signature byte 5                                                      | 38 |

| Table 20. | Read ONFI signature                                                              | 39 |

| Table 21. | Parameter page data structure                                                    |    |

| Table 22. | Extended Read Status Register commands                                           | 43 |

| Table 23. | Block failure                                                                    | 45 |

| Table 24. | Program erase times and program erase endurance cycles                           |    |

| Table 25. | Absolute maximum ratings                                                         |    |

| Table 26. | Operating and AC measurement conditions                                          | 50 |

| Table 27. | Capacitance                                                                      |    |

| Table 28. | DC characteristics (1.8 V devices)                                               |    |

| Table 29. | DC characteristics (3 V devices)                                                 |    |

| Table 30. | AC characteristics for command, address, data input                              |    |

| Table 31. | AC characteristics for operations                                                |    |

| Table 32. | TSOP48 - 48 lead plastic thin small outline, 12 x 20 mm, package mechanical data |    |

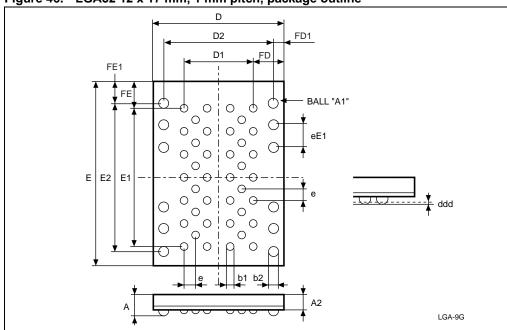

| Table 33. | LGA52 12 x 17 mm, 1 mm pitch, package mechanical data                            | 66 |

| Table 34. | Ordering information scheme                                                      | 67 |

| Table 35  | Document revision history                                                        | 68 |

# **List of figures**

| Figure 1.  | Logic block diagram                                                      | 9  |

|------------|--------------------------------------------------------------------------|----|

| Figure 2.  | Logic diagram                                                            |    |

| Figure 3.  | TSOP48 connections for NAND04G-B2D and NAND08G-BxC                       | 11 |

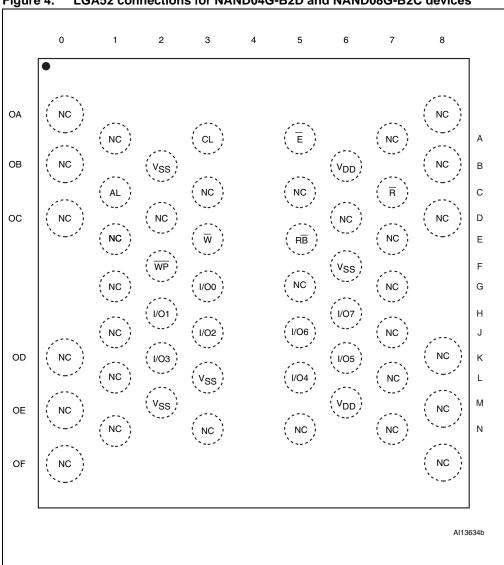

| Figure 4.  | LGA52 connections for NAND04G-B2D and NAND08G-B2C devices                | 12 |

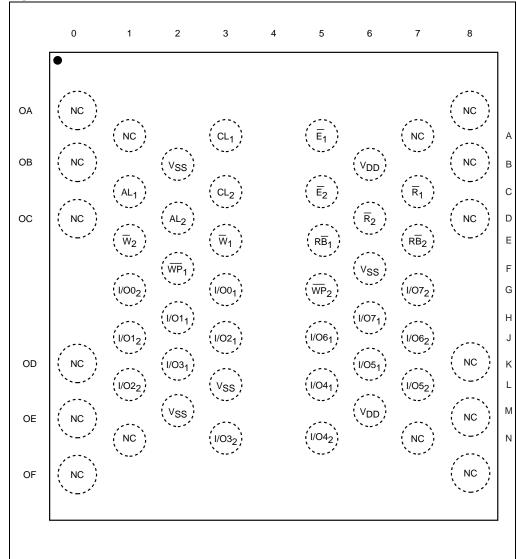

| Figure 5.  | LGA52 connections for the NAND08G-B4C devices                            | 13 |

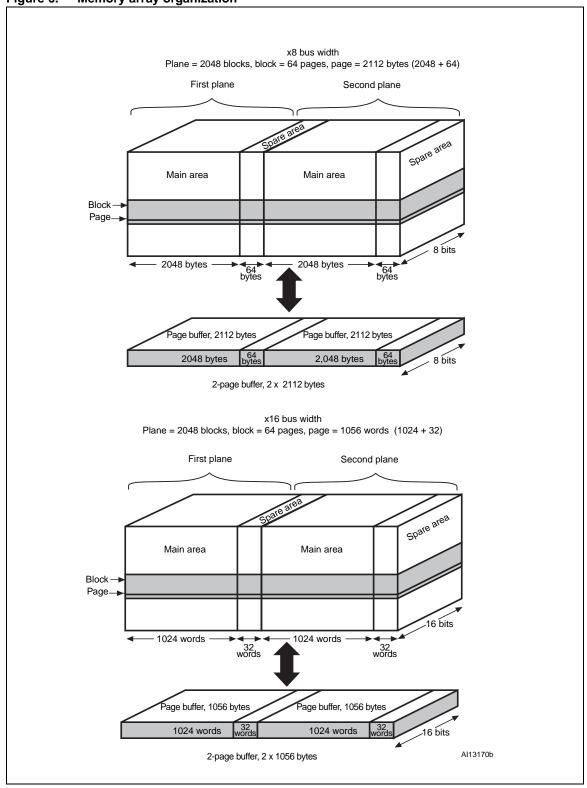

| Figure 6.  | Memory array organization                                                | 15 |

| Figure 7.  | Read operations                                                          |    |

| Figure 8.  | Random data output during sequential data output                         | 24 |

| Figure 9.  | Cache read (sequential) operation                                        | 25 |

| Figure 10. | Cache read (random) operation                                            |    |

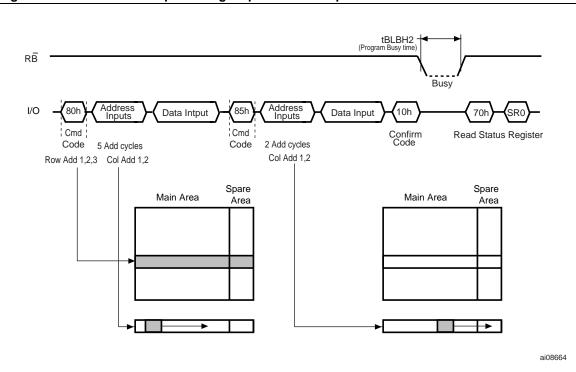

| Figure 11. | Page program operation                                                   | 27 |

| Figure 12. | Random data input during sequential data input                           | 27 |

| Figure 13. | Multiplane page program waveform                                         | 28 |

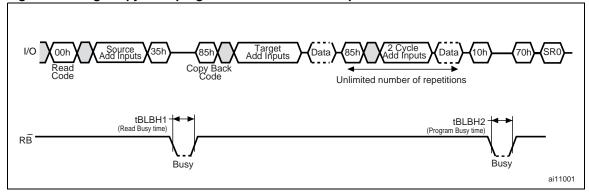

| Figure 14. | Copy back program (without readout of data)                              | 29 |

| Figure 15. | Copy back program (with readout of data)                                 | 30 |

| Figure 16. | Page copy back program with random data input                            | 30 |

| Figure 17. | Multiplane copy back program                                             |    |

| Figure 18. | Block erase                                                              | 31 |

| Figure 19. | Multiplane block erase                                                   | 32 |

| Figure 20. | Page organization                                                        | 33 |

| Figure 21. | Bad block management flowchart                                           | 45 |

| Figure 22. | Garbage collection                                                       |    |

| Figure 23. | Error detection                                                          |    |

| Figure 24. | Equivalent testing circuit for AC characteristics measurement            | 51 |

| Figure 25. | Command latch AC waveforms                                               | 54 |

| Figure 26. | Address latch AC waveforms                                               |    |

| Figure 27. | Data input latch AC waveforms                                            | 55 |

| Figure 28. | Sequential data output after read AC waveforms                           | 56 |

| Figure 29. | Sequential data output after read AC waveforms (EDO mode)                | 56 |

| Figure 30. | Read Status Register or read EDC Status Register AC waveform             |    |

| Figure 31. | Read status enhanced waveform                                            |    |

| Figure 32. | Read Electronic Signature AC waveform                                    | 58 |

| Figure 33. | Read ONFI signature waveform                                             | 58 |

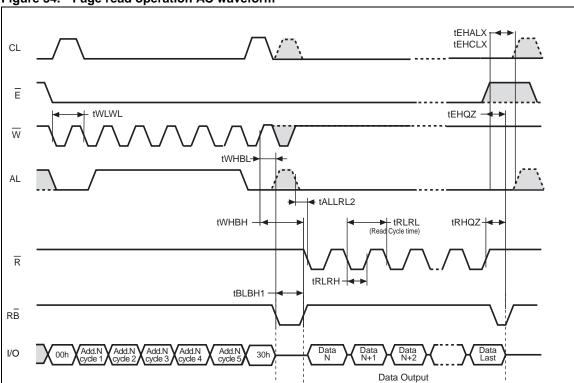

| Figure 34. | Page read operation AC waveform                                          | 59 |

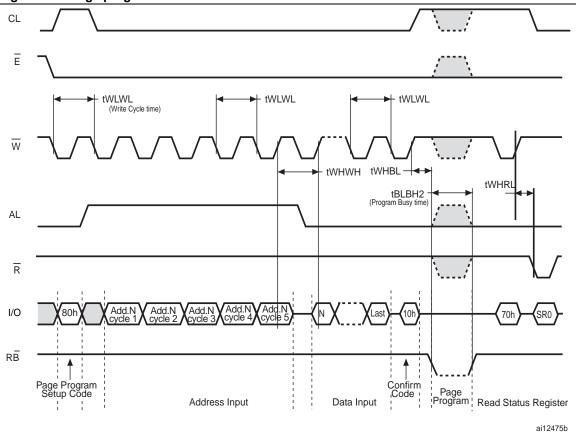

| Figure 35. | Page program AC waveform                                                 | 60 |

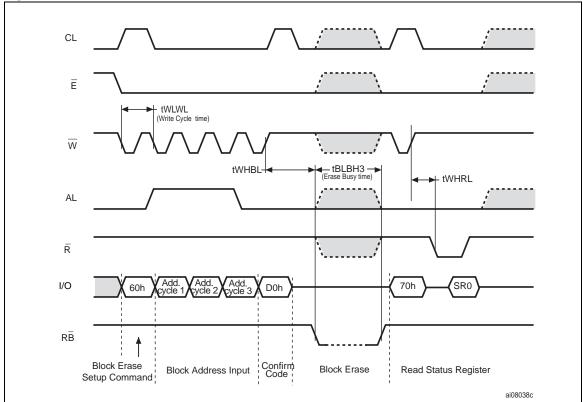

| Figure 36. | Block erase AC waveform                                                  | 61 |

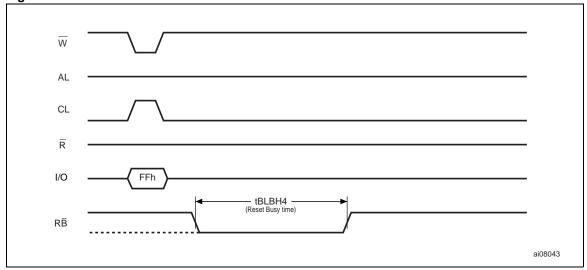

| Figure 37. | Reset AC waveform                                                        | 61 |

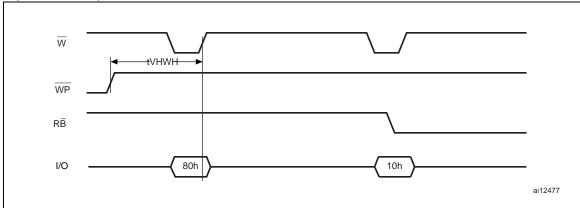

| Figure 38. | Program/erase enable waveform                                            | 62 |

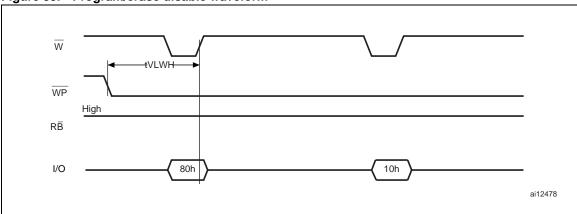

| Figure 39. | Program/erase disable waveform                                           | 62 |

| Figure 40. | Read parameter page waveform                                             | 62 |

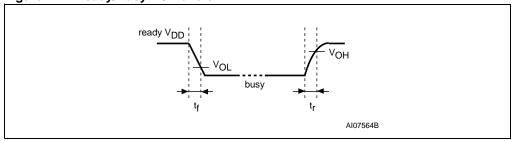

| Figure 41. | Ready/Busy AC waveform                                                   |    |

| Figure 42. | Ready/Busy load circuit                                                  |    |

| Figure 43. | Resistor value versus waveform timings for Ready/Busy signal             |    |

| Figure 44. | Data protection                                                          |    |

| Figure 45. | TSOP48 - 48 lead plastic thin small outline, 12 x 20 mm, package outline |    |

| Figure 46. | LGA52 12 x 17 mm, 1 mm pitch, package outline                            |    |

## 1 Description

The NAND04G-B2D and NAND08G-BxC are part of the NAND Flash 2112 byte/1056 word page family of non-volatile Flash memories. They use NAND cell technology have a density of 4 Gbits and 8 Gbits, respectively.

The NAND04G-B2D memory array is split into 2 planes of 2048 blocks each. This multiplane architecture makes it possible to program 2 pages at a time (one in each plane), or to erase 2 blocks at a time (one in each plane). This feature reduces the average program and erase times by 50%.

The NAND08G-BxC is a stacked device that combines two NAND04G-B2D dice, both of which feature a multiplane architecture.

In the NAND08G-B2C devices, only one of the memory components can be enabled at a time, therefore, operations can only be performed on one of the memory components at any one time.

In the NAND08G-B4C devices, each NAND04G-B2D die can be accessed independently using two sets of signals.

The devices operate from a 1.8 V or 3 V voltage supply. Depending on whether the device has a x8 or x16 bus width, the page size is 2112 bytes (2048 + 64 spare) or or 1056 words (1024 + 32 spare), respectively.

The address lines are multiplexed with the data input/output signals on a multiplexed x8 input/output bus. This interface reduces the pin count and makes it possible to migrate to other densities without changing the footprint.

Each block can be programmed and erased over 100 000 cycles with ECC (error correction code) on. To extend the lifetime of NAND Flash devices, the implementation of an ECC is strongly recommended.

A Write Protect pin is available to provide hardware protection against program and erase operations.

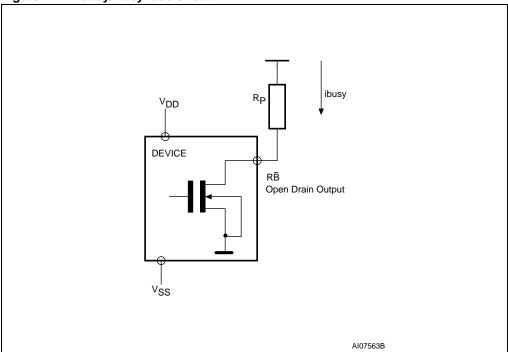

The devices feature an open-drain ready/busy output that identifies if the P/E/R (program/erase/read) Controller is currently active. The use of an open-drain output allows the ready/busy pins from several memories to connect to a single pull-up resistor.

A Copy Back Program command is available to optimize the management of defective blocks. When a page program operation fails, the data can be programmed in another page without having to resend the data to be programmed. An embedded error detection code is automatically executed after each copy back operation: 1 error bit can be detected for every 528 bits. With this feature it is no longer necessary, nor recommended, to use an external 2-bit ECC to detect copy back operation errors.

The devices have a cache read feature that improves the read throughput for large files. During cache reading, the device loads the data in a Cache Register while the previous data is transferred to the I/O buffers to be read.

The devices have the Chip Enable 'don't care' feature, which allows code to be directly downloaded by a microcontroller. This is possible because Chip Enable transitions during the latency time do not stop the read operation.

Both the NAND04G-B2D and NAND08G-BxC support the ONFI 1.0 specification.

Two further features are available as options:

- Extra non-volatile protection.

- An individual serial number that acts as an unique identifier.

More information is available, upon completion of an NDA (non-disclosure agreement), and therefore, the details are not described in this datasheet. For more information on these two options, contact your nearest ST Sales office.

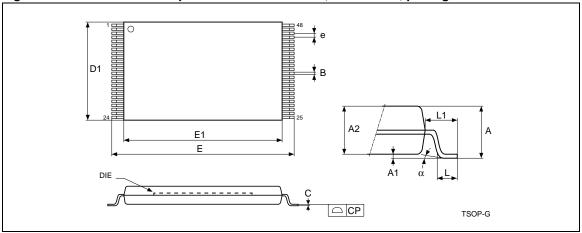

The devices are available in the TSOP48 (12 x 20 mm) and LGA52 (12 x 17 mm) packages. To meet environmental requirements, ST offers the NAND04G-B2D and NAND08G-BxC in  $ECOPACK^{\otimes}$  packages.

For information on how to order these options, refer to *Table 34: Ordering information scheme*. Devices are shipped from the factory with block 0 always valid and the memory content bits, in valid blocks, erased to '1'.

Table 2: Product description lists the part numbers and other information for all the devices able in the family.

Table 2. Product description

|              |         |              |              |                   |                    |                   | Timing                       | s                              |                          |                         |                                |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

|--------------|---------|--------------|--------------|-------------------|--------------------|-------------------|------------------------------|--------------------------------|--------------------------|-------------------------|--------------------------------|--|--|-----|-----|-----|-------|--------|--------|------------------|-------|-------|--------|--------|-----|

| Part Number  | Density | Bus<br>width | Page<br>size | Block<br>size     | Memory<br>array    | Operating voltage | Sequential access time (min) | Random<br>access<br>time (max) | Page<br>Program<br>(typ) | Block<br>Erase<br>(typ) | Package                        |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND04GR3B2D |         | x8           | 2048+64      | 128 K+            |                    | 1.7 to<br>1.95 V  | 45 ns                        |                                |                          |                         | LGA52                          |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND04GW3B2D | 4.Ch    | X8           | bytes        | 4 K bytes         | 64 pages<br>x 4096 | 2.7 to<br>3.6 V   | 25 ns                        | 25 µs                          | 200 µs                   | 1.5ms                   | TSOP48<br>LGA52                |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND04GR4B2D | 4 Gb    |              |              |                   |                    |                   |                              |                                |                          |                         |                                |  |  | v16 | v16 | x16 | 1024+ | 64 K + | blocks | 1.7 to<br>1.95 V | 45 ns | 25 μ5 | 200 μ3 | 1.0113 | (1) |

| NAND04GW4B2D |         | XIO          | 32 words     | 2 K words         |                    | 2.7 to<br>3.6 V   | 25 ns                        |                                |                          |                         |                                |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GR3B2C |         | x8           | 2048+64      | 128 K +           |                    | 1.7 to<br>1.95 V  | 45 ns                        |                                |                          |                         | LGA52 <sup>(2)</sup>           |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GW3B2C |         | ***          | bytes        | 4 K bytes         |                    | 2.7 to<br>3.6 V   | 25 ns                        |                                |                          |                         | TSOP48<br>LGA52 <sup>(2)</sup> |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GR4B2C |         | x16          | 1024+        | 64 K +            | 64 pages<br>x 8192 | 1.7 to<br>1.95 V  | 45 ns                        | 25 110                         | 200 us                   | 1.5mc                   | (1)(2)                         |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GW4B2C | 8 Gb    | Gb   x16     | 32 words     | 2 words 2 K words |                    | 2.7 to<br>3.6 V   | 25 ns                        | - 25 μs                        | 200 μs                   | 1.5ms                   | ,,,,                           |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GR3B4C |         | x8           | 2048+64      | 128 K +           |                    | 1.7 to<br>1.95 V  | 45 ns                        |                                |                          |                         | LGA52 <sup>(2)</sup>           |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

| NAND08GW3B4C |         | x8           | bytes        | 4 K bytes         |                    | 2.7 to<br>3.6 V   | 25 ns                        |                                |                          |                         | LUAUZ                          |  |  |     |     |     |       |        |        |                  |       |       |        |        |     |

- 1. x16 organization is only available for MCP products.

- 2. The NAND08G-BxC is composed of two 4-Gbit dice.

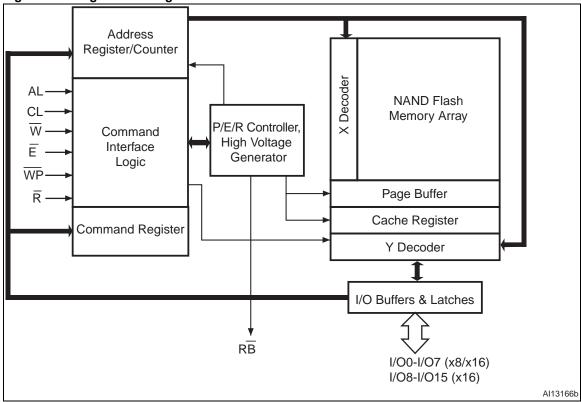

Figure 1. Logic block diagram

1. The NAND08G-B4C devices have two separate sets of signals for each 4 Gb die.

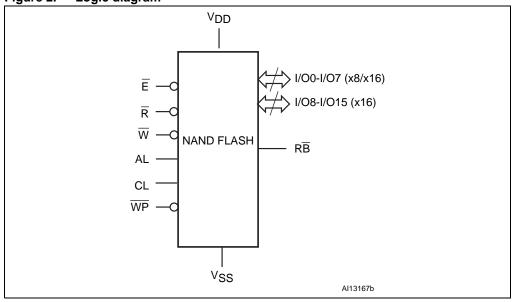

Figure 2. Logic diagram

1. The NAND08G-B4C devices have two separate sets of signals for each 4 Gb die.

Table 3. Signal names<sup>(1)</sup>

| Signal          | Function                                                               | Direction    |

|-----------------|------------------------------------------------------------------------|--------------|

| I/O0-7          | Data input/outputs, address inputs, or command inputs (x8/x16 devices) | Input/output |

| I/O8-15         | Data input/outputs (x16 devices)                                       | Input/output |

| AL              | Address Latch Enable                                                   | Input        |

| CL              | Command Latch Enable                                                   | Input        |

| Ē               | Chip Enable                                                            | Input        |

| R               | Read Enable                                                            | Input        |

| RB              | Ready/Busy (open-drain output)                                         | Output       |

| W               | Write Enable                                                           | Input        |

| WP              | Write Protect                                                          | Input        |

| V <sub>DD</sub> | Supply Voltage                                                         | Power supply |

| V <sub>SS</sub> | Ground                                                                 | Ground       |

| NC              | Not connected internally                                               | N/A          |

| DU              | Do not use                                                             | N/A          |

<sup>1.</sup> The NAND08G-B4C devices have two separate sets of signals for each 4 Gb die.

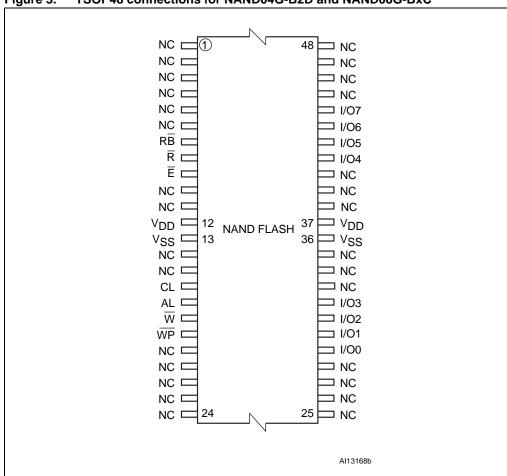

Figure 3. TSOP48 connections for NAND04G-B2D and NAND08G-BxC

Figure 4. LGA52 connections for NAND04G-B2D and NAND08G-B2C devices

Figure 5. LGA52 connections for the NAND08G-B4C devices

1. The NAND08G-B4C devices have two separate sets of signals for each 4 Gb die.

## 2 Memory array organization

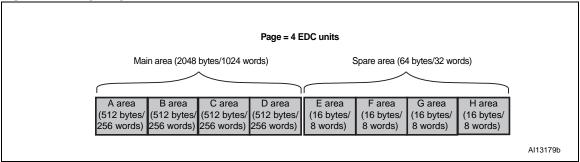

The memory array of the devices is made up of NAND structures where 32 cells are connected in series. It is organized into blocks where each block contains 64 pages. The array is split into two areas, the main area, and the spare area. The main area of the array is used to store data, and the spare area typically stores error correction codes, software flags, or bad block identification.

In x8 devices, the pages are split into a 2048-byte main area and a spare area of 64 bytes. In x16 devices, the pages are split into a 1024-word main area and a spare area of 32 words. Refer to *Figure 6: Memory array organization*.

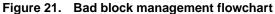

#### **Bad blocks**

In the x8 devices, the NAND Flash 2112 byte/1056 word page devices may contain bad blocks, which are blocks that contain one or more invalid bits whose reliability is not guaranteed. Additional bad blocks may develop during the lifetime of the device.

The bad block information is written prior to shipping (refer to Section 9.1: Bad block management for more details).

Table 4 shows the minimum number of valid blocks. The values shown include both the bad blocks that are present when the device is shipped and the bad blocks that could develop later on. Block 0 is guaranteed to be valid up to 1000 write/erase cycles with 1 bit ECC.

These blocks need to be managed using bad blocks management, block replacement, or error correction codes (refer to Section 9: Software algorithms).

Table 4. Valid Blocks

| Density of Device      | Min  | Max  |

|------------------------|------|------|

| 4 Gbits                | 4016 | 4096 |

| 8 Gbits <sup>(1)</sup> | 8032 | 8192 |

The NAND08G-BxC devices are composed of two 4-Gbit dice. The minimum number of valid blocks is 4016 for each die.

Figure 6. Memory array organization

## 3 Signal descriptions

See *Figure 2: Logic diagram* and *Table 3: Signal names* for a brief overview of the signals connected to this device. The NAND08G-B4C devices have two separate sets of signals for each 4 Gb die.

#### **3.1** Inputs/outputs (I/O0-I/O7)

Input/outputs 0 to 7 input the selected address, output the data during a read operation, or input a command or data during a write operation. The inputs are latched on the rising edge of Write Enable. I/O0-I/O7 are left floating when the device is deselected or the outputs are disabled.

### 3.2 Inputs/Outputs (I/O8-I/O15)

Input/Outputs 8 to 15 are only available in x16 devices. They output the data during a read operation or input data during a write operation. Command and address inputs only require I/O0 to I/O7.

The inputs are latched on the rising edge of Write Enable. I/O8-I/O15 are left floating when the device is deselected or the outputs are disabled.

### 3.3 Address Latch Enable (AL)

The Address Latch Enable activates the latching of the address inputs in the Command Interface. When AL is high, the inputs are latched on the rising edge of Write Enable.

## 3.4 Command Latch Enable (CL)

The Command Latch Enable activates the latching of the command inputs in the Command Interface. When CL is high, the inputs are latched on the rising edge of Write Enable.

## 3.5 Chip Enable $(\overline{E})$

The Chip Enable input,  $\overline{E}$ , activates the memory control logic, input buffers, decoders and sense amplifiers. When Chip Enable is low,  $V_{IL}$ , the device is selected. If Chip Enable goes high,  $V_{IH}$ , while the device is busy, the device remains selected and does not go into standby mode.

## 3.6 Read Enable $(\overline{R})$

The Read Enable pin,  $\overline{R}$ , controls the sequential data output during read operations. Data is valid  $t_{RLQV}$  after the falling edge of  $\overline{R}$ . The falling edge of  $\overline{R}$  also increments the internal column address counter by one.

## 3.7 Write Enable $(\overline{W})$

The Write Enable input,  $\overline{W}$ , controls writing to the Command Interface, input address and data latches. Both addresses and data are latched on the rising edge of Write Enable.

During power-up and power-down a recovery time of  $10 \mu s$  (min) is required before the command interface is ready to accept a command. It is recommended to keep Write Enable high during the recovery time.

## 3.8 Write Protect (WP)

The Write Protect pin is an input that gives a hardware protection against unwanted program or erase operations. When Write Protect is Low,  $V_{\rm IL}$ , the device does not accept any program or erase operations.

It is recommended to keep the Write Protect pin Low, V<sub>IL</sub>, during power-up and power-down.

## 3.9 Ready/Busy (RB)

The Ready/Busy output,  $R\overline{B}$ , is an open-drain output that identifies if the P/E/R Controller is currently active.

When Ready/Busy is Low,  $V_{OL}$ , a read, program or erase operation is in progress. When the operation completes, Ready/Busy goes High,  $V_{OH}$ .

The use of an open-drain output allows the ready/busy pins from several memories to be connected to a single pull-up resistor. A Low then indicates that one or more of the memories is busy.

During power-up and power-down a minimum recovery time of 10  $\mu$ s is required before the command interface is ready to accept a command. During this period the RB signal is Low,  $V_{OL}$ .

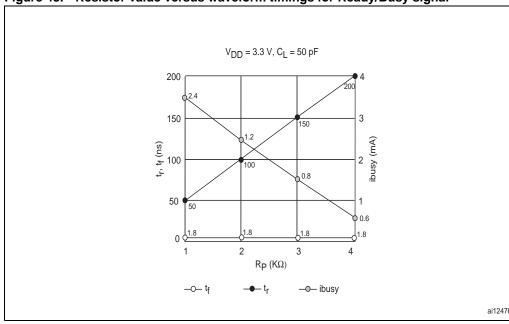

Refer to Section 12.1: Ready/Busy signal electrical characteristics for details on how to calculate the value of the pull-up resistor.

## 3.10 V<sub>DD</sub> supply voltage

V<sub>DD</sub> provides the power supply to the internal core of the memory device. It is the main power supply for all operations (read, program and erase).

An internal voltage detector disables all functions whenever  $V_{DD}$  is below  $V_{LKO}$  (see *Table 29*) to protect the device from any involuntary program/erase during power-transitions.

Each device in a system should have  $V_{DD}$  decoupled with a 0.1  $\mu$ F capacitor. The PCB track widths should be sufficient to carry the required program and erase currents.

## 3.11 V<sub>SS</sub> ground

Ground,  $V_{SS,}$  is the reference for the power supply. It must be connected to the system ground.

## 4 Bus operations

There are six standard bus operations that control the memory, as described in this section. See *Table 5: Bus operations* for a summary of these operations.

Typically, glitches of less than 5 ns on Chip Enable, Write Enable, and Read Enable are ignored by the memory and do not affect bus operations.

## 4.1 Command input

Command input bus operations give commands to the memory.

Commands are accepted when Chip Enable is Low, Command Latch Enable is High, Address Latch Enable is Low, and Read Enable is High. They are latched on the rising edge of the Write Enable signal.

Only I/O0 to I/O7 are used to input commands.

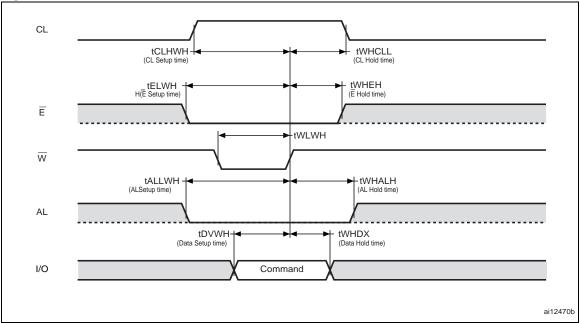

See Figure 25 and Table 30 for details of the timings requirements.

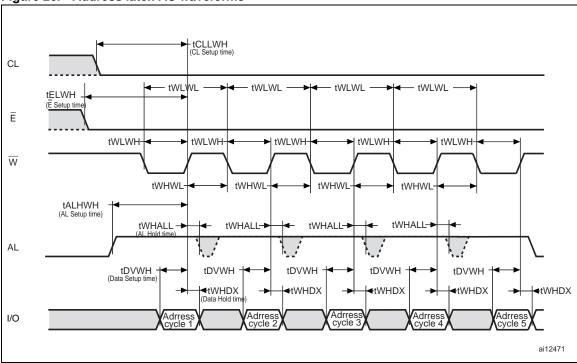

### 4.2 Address input

Address input bus operations input the memory addresses. Five bus cycles are required to input the addresses (refer to *Table 6: Address insertion (x8 devices)* and *Table 7: Address insertion (x16 devices)*).

The addresses are accepted when Chip Enable is Low, Address Latch Enable is High, Command Latch Enable is Low, and Read Enable is High. They are latched on the rising edge of the Write Enable signal.

Only I/O0 to I/O7 are used to input addresses.

See Figure 26 and Table 30 for details of the timings requirements.

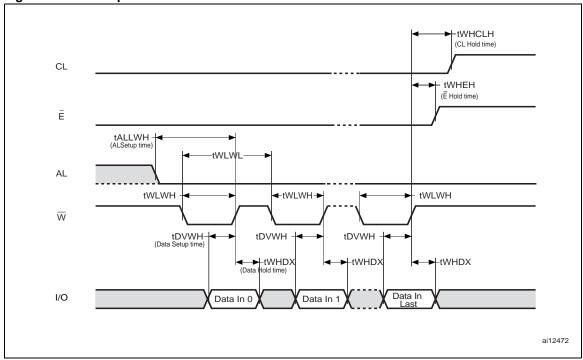

### 4.3 Data input

Data input bus operations input the data to be programmed.

Data is accepted only when Chip Enable is Low, Address Latch Enable is Low, Command Latch Enable is Low, and Read Enable is High. The data is latched on the rising edge of the Write Enable signal. The data is input sequentially using the Write Enable signal.

See Figure 27 and Table 30 and Table 31 for details of the timings requirements.

## 4.4 Data output

Data output bus operations read the data in the memory array, the Status Register, the electronic signature, and the unique identifier.

Data is output when Chip Enable is Low, Write Enable is High, Address Latch Enable is Low, and Command Latch Enable is Low.

The data is output sequentially using the Read Enable signal.

If the Read Enable pulse frequency is lower then 33 MHz (t<sub>RLRL</sub> higher than 30 ns), the output data is latched on the rising edge of Read Enable signal (see *Figure 28*).

For higher frequencies ( $t_{RLRL}$  lower than 30 ns), the EDO (extended data out) mode must be used. In this mode, data output bus operations are valid on the input/output bus for a time of  $t_{RLOX}$  after the falling edge of Read Enable signal (see *Figure 29*).

See *Table 31* for details on the timings requirements.

### 4.5 Write protect

Write protect bus operations protect the memory against program or erase operations. When the Write Protect signal is Low the device does not accept program or erase operations, and, therefore, the contents of the memory array cannot be altered. The Write Protect signal is not latched by Write Enable to ensure protection, even during power-up.

### 4.6 Standby

When Chip Enable is High the memory enters Standby mode, the device is deselected, outputs are disabled, and power consumption is reduced.

Table 5. Bus operations

| Bus operation | Ē               | AL              | CL              | R               | W               | WP               | 1/00 - 1/07 | I/O8 - I/O15 <sup>(1)</sup> |  |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-------------|-----------------------------|--|

| Command input | V <sub>IL</sub> | $V_{IL}$        | V <sub>IH</sub> | V <sub>IH</sub> | Rising          | X <sup>(2)</sup> | Command     | Х                           |  |

| Address input | $V_{IL}$        | V <sub>IH</sub> | $V_{IL}$        | V <sub>IH</sub> | Rising          | Х                | Address     | Х                           |  |

| Data input    | $V_{IL}$        | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | Rising          | $V_{IH}$         | Data input  | Data input                  |  |

| Data output   | $V_{IL}$        | $V_{IL}$        | $V_{IL}$        | Falling         | V <sub>IH</sub> | X                | Data output | Data output                 |  |

| Write protect | Х               | Х               | Х               | Х               | X               | $V_{IL}$         | Χ           | Х                           |  |

| Standby       | $V_{IH}$        | Х               | Х               | Х               | Х               | $V_{IL}/V_{DD}$  | Х           | Х                           |  |

<sup>1.</sup> Only for x16 devices.

Table 6. Address insertion (x8 devices)

|                             |                 | riam coo moormon (no acricoo) |                 |                 |                 |                    |      |      |  |  |  |  |

|-----------------------------|-----------------|-------------------------------|-----------------|-----------------|-----------------|--------------------|------|------|--|--|--|--|

| Bus<br>Cycle <sup>(1)</sup> | 1/07            | I/O6                          | I/O5            | I/O4            | I/O3            | I/O2               | I/O1 | 1/00 |  |  |  |  |

| 1 <sup>st</sup>             | A7              | A6                            | A5              | A4              | А3              | A2                 | A1   | A0   |  |  |  |  |

| 2 <sup>nd</sup>             | V <sub>IL</sub> | V <sub>IL</sub>               | V <sub>IL</sub> | V <sub>IL</sub> | A11             | A10                | A9   | A8   |  |  |  |  |

| 3 <sup>rd</sup>             | A19             | A18                           | A17             | A16             | A15             | A14                | A13  | A12  |  |  |  |  |

| 4 <sup>th</sup>             | A27             | A26                           | A25             | A24             | A23             | A22                | A21  | A20  |  |  |  |  |

| 5 <sup>th</sup>             | V <sub>IL</sub> | V <sub>IL</sub>               | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IL</sub> | A30 <sup>(2)</sup> | A29  | A28  |  |  |  |  |

<sup>1.</sup> Any additional address input cycles are ignored.

<sup>2.</sup>  $\overline{\text{WP}}$  must be  $V_{\text{IH}}$  when issuing a program or erase command.

<sup>2.</sup> A30 is only valid for the NAND08G-BxC devices.

| Table 7. | Address | insertion | (x16 | devices) |

|----------|---------|-----------|------|----------|

|          |         |           |      |          |

| Bus<br>Cycle <sup>(1)</sup> | 1/07     | 1/06     | I/O5     | I/O4     | I/O3     | I/O2               | I/O1 | 1/00 |

|-----------------------------|----------|----------|----------|----------|----------|--------------------|------|------|

| 1 <sup>st</sup>             | A7       | A6       | A5       | A4       | А3       | A2                 | A1   | A0   |

| 2 <sup>nd</sup>             | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | A10                | A9   | A8   |

| 3 <sup>rd</sup>             | A18      | A17      | A16      | A15      | A14      | A13                | A12  | A11  |

| 4 <sup>th</sup>             | A26      | A25      | A24      | A23      | A22      | A21                | A20  | A19  |

| 5 <sup>th</sup>             | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | $V_{IL}$ | A29 <sup>(2)</sup> | A28  | A27  |

<sup>1.</sup> Any additional address input cycles are ignored.

Table 8. Address definition (x8 devices)

| Address   | Definition                  |

|-----------|-----------------------------|

| A0 - A11  | Column address              |

| A12 - A17 | Page address                |

| A18 - A29 | Block address(NAND04G-B2D)  |

| A18 - A30 | Block address (NAND08G-BxC) |

| A18 = 0   | First plane                 |

| A18 = 1   | Second plane                |

Table 9. Address definition (x16 devices)

| Address   | Definition                  |

|-----------|-----------------------------|

| A0 - A10  | Column address              |

| A11 - A16 | Page address                |

| A17 - A28 | Block address (NAND04G-B2D) |

| A17 - A29 | Block address (NAND08G-BxC) |

| A18 = 0   | First plane                 |

| A18 = 1   | Second plane                |

<sup>2.</sup> A29 is only valid for the NAND08G-BxC devices.

### 5 Command set

All bus write operations to the device are interpreted by the command interface. The commands are input on I/O0-I/O7 and are latched on the rising edge of Write Enable when the command Latch Enable signal is high. Device operations are selected by writing specific commands to the Command Register. The two-step command sequences for program and erase operations are imposed to maximize data security.

Table 10 summarizes the commands.

Table 10. Commands

| Command <sup>(1)</sup>                      |                       | Commands              |                       |                       |                      |

|---------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------|

| Command                                     | 1 <sup>st</sup> cycle | 2 <sup>nd</sup> cycle | 3 <sup>rd</sup> cycle | 4 <sup>th</sup> cycle | accepted during busy |

| Read                                        | 00h                   | 30h                   | -                     | -                     |                      |

| Random Data Output                          | 05h                   | E0h                   | -                     | -                     |                      |

| Cache Read (sequential)                     | 31h                   | _                     | -                     | _                     |                      |

| Enhanced Cache Read (random)                | 00h                   | 31h                   | -                     | -                     |                      |

| Exit Cache Read                             | 3Fh                   | -                     | -                     | -                     | Yes <sup>(2)</sup>   |

| Page Program (sequential input default)     | 80h                   | 10h                   | _                     | -                     |                      |

| Random Data Input                           | 85h                   | _                     | _                     | _                     |                      |

| Multiplane Page Program <sup>(3)</sup>      | 80h                   | 11h                   | 81h                   | 10h                   |                      |

| Multiplane Page Program                     | 80h                   | 11h                   | 80h                   | 10h                   |                      |

| Copy Back Read                              | 00h                   | 35h                   | _                     | _                     |                      |

| Copy Back Program                           | 85h                   | 10h                   | _                     | _                     |                      |

| Multiplane Copy Back Program <sup>(3)</sup> | 85h                   | 11h                   | 81h                   | 10h                   |                      |

| Multiplane Copy Back Program                | 85h                   | 11h                   | 85h                   | 10h                   |                      |

| Block Erase                                 | 60h                   | D0h                   | -                     | -                     |                      |

| Multiplane Block Erase <sup>(3)</sup>       | 60h                   | 60h                   | D0h                   | -                     |                      |

| Multiplane Block Erase                      | 60h                   | D1h                   | 60h                   | D0h                   |                      |

| Reset                                       | FFh                   | -                     | _                     | -                     | Yes                  |

| Read Electronic Signature                   | 90h                   | -                     | -                     | -                     |                      |

| Read Status Register                        | 70h                   | -                     | -                     | -                     | Yes                  |

| Read Status Enhanced                        | 78h                   | -                     | -                     | -                     | Yes                  |

| Read Parameter Page                         | ECh                   | _                     | -                     | -                     |                      |

| Read EDC Status Register                    | 7Bh                   | _                     | _                     | _                     |                      |

<sup>1.</sup> Commands in bold are referring to ONFI 1.0 specifications.

<sup>2.</sup> Only during cache read busy.

<sup>3.</sup> Command maintained for backward compatibility.

## 6 Device operations

This section provides details of the device operations.

### 6.1 Read memory array

At power-up the device defaults to read mode. To enter read mode from another mode, the Read command must be issued (see *Table 10: Commands*).

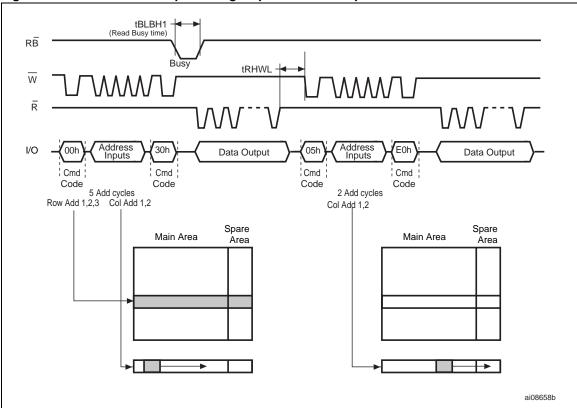

#### 6.1.1 Random read

Each time the Read command is issued, the first read is random read.

#### 6.1.2 Page read

After the first random read access, the page data (2112 bytes or 1056 words) are transferred to the page buffer in a time of t<sub>WHBH</sub> (see *Table 31*). Once the transfer is complete, the Ready/Busy signal goes High. The data can then be read sequentially (from selected column address to last column address) by pulsing the Read Enable signal.

The device can output random data in a page, instead of consecutive sequential data, by issuing a Random Data Output command. The Random Data Output command can be used to skip some data during a sequential data output.

The sequential operation can be resumed by changing the column address of the next data to be output, to the address which follows the Random Data Output command. The Random Data Output command can be issued as many times as required within a page.

The Random Data Output command is not accepted during cache read operations.

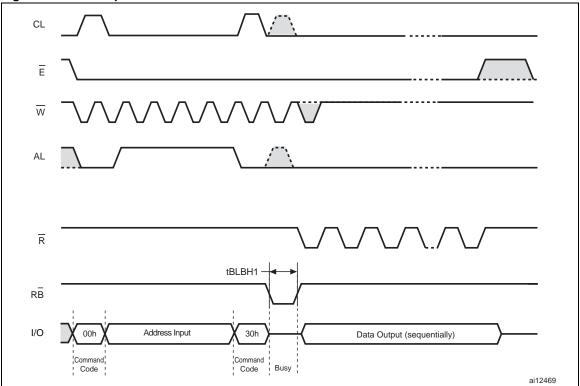

Figure 7. Read operations

Figure 8. Random data output during sequential data output

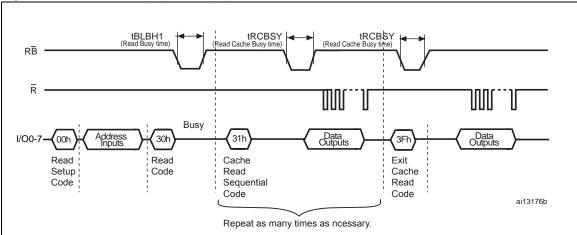

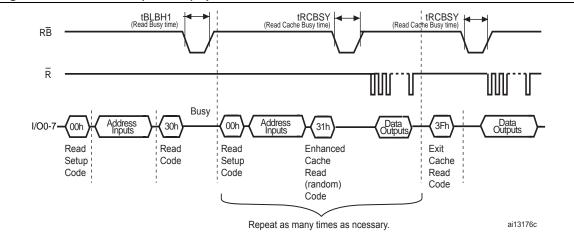

#### 6.2 Cache read

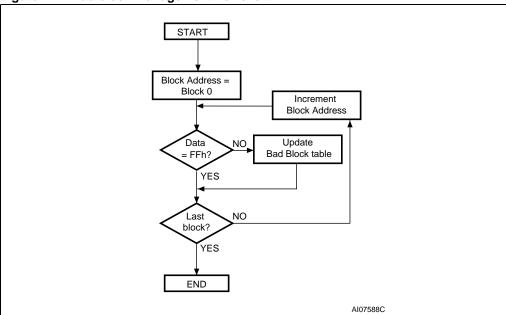

The cache read operation improves the read throughput by reading data using the Cache Register. As soon as the user starts to read one page, the device automatically loads the next page into the Cache Register.

A Read Page command, as defined in *Section 6.1.1: Random read*, is issued prior to the first Read Cache command in a read cache sequence. Once the data output of the Page Read command terminates, the Cache Read command can be issued as follows:

- Issue a Sequential Cache Read command to copy the next page in sequential order to the Cache Register.

- 2. Issue a Random Cache Read command to copy the page addressed in this command to the Cache Register.

The two commands can be used interchangeably, in any order. When there are no more pages are to be read, the final page is copied into the Cache Register by issuing the Exit Cache Read command. A Read Cache Command must not be issued after the last page of the device is read.

See Figure 9: Cache read (sequential) operation and Figure 10: Cache read (random) operation for examples of the two sequences.

After the Sequential Cache Read or Random Cache Read command has been issued, the Ready/Busy signal goes Low and the Status Register bits are set to SR5 =' 0' and SR6 ='0' for a period of Cache Read busy time,  $t_{RCBSY}$ , while the device copies the next page into the Cache Register.

After the cache read busy time has passed, the Ready/Busy signal goes High and the Status Register bits are set to SR5 = '0' and SR6 = '1', signifying that the Cache Register is ready to download new data. Data of the previously read page can be output from the page buffer by toggling the Read Enable signal. Data output always begins at column address 00h, but the Random Data Output command is also supported.

Figure 9. Cache read (sequential) operation

Figure 10. Cache read (random) operation

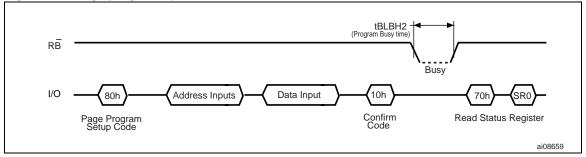

### 6.3 Page program

The page program operation is the standard operation to program data to the memory array. Generally, the page is programmed sequentially, however, the device does support random input within a page.

It is recommended to address pages sequentially within a given block.

The memory array is programmed by page, however, partial page programming is allowed where any number of bytes (1 to 2112) or words (1 to 1056) can be programmed.

The maximum number of consecutive, partial-page program operations allowed in the same page is four. After exceeding four operations a Block Erase command must be issued before any further program operations can take place in that page.

#### 6.3.1 Sequential input

To input data sequentially the addresses must be sequential and remain in one block.

For sequential input each page program operation consists of the following five steps:

- One bus cycle is required to set up the Page Program (sequential input) command (see Table 10: Commands).

- Five bus cycles are then required to input the program address (refer to Table 6: Address insertion (x8 devices) and Table 7: Address insertion (x16 devices)).

- 3. The data is then loaded into the Data Registers.

- 4. One bus cycle is required to issue the Page Program Confirm command to start the P/E/R Controller. The P/E/R only starts if the data has been loaded in step 3.

- 5. the P/E/R Controller then programs the data into the array.

See Figure 11: Page program operation for more information.

#### 6.3.2 Random data input in page

During a sequential input operation, the next sequential address to be programmed can be replaced by a random address by issuing a Random Data Input command. The following two steps are required to issue the command:

- One bus cycle is required to set up the Random Data Input command (see Table 10: Commands).

- Two bus cycles are then required to input the new column address (refer to Table 6: Address insertion (x8 devices)).

Random data input can be repeated as often as required in any given page.

Once the program operation has started, the Status Register can be read using the Read Status Register command. During program operations the Status Register only flags errors for bits set to '1' that have not been successfully programmed to '0'.

During the program operation, only the Read Status Register and Reset commands are accepted; all other commands are ignored.

Once the program operation has completed, the P/E/R Controller bit SR6 is set to '1' and the Ready/Busy signal goes High.

The device remains in Read Status Register mode until another valid command is written to the command interface.

Figure 11. Page program operation

Figure 12. Random data input during sequential data input

#### 6.4 Multiplane page program

The devices support multiplane page program, which enables the programming of two pages in parallel, one in each plane.

A multiplane page program operation requires the following two steps:

- The first step serially loads up to two pages of data (4224 bytes) into the data buffer. It

- One clock cycle to set up the Page Program command (see Section 6.3.1: Sequential input).

- 5 bus write cycles to input the first page address and data. The address of the first page must be within the first plane (A18 = 0).

- One bus write cycle to issue the Page Program Confirm code. After this, the device is busy for a time of t<sub>IPBSY</sub>.

- When the device returns to the ready state (Ready/Busy High), a multiplane page program setup code must be issued, followed by the 2nd page address (5 write cycles) and data. The address of the 2nd page must be within the second plane (A18 = 1).

- The 2nd step programs in parallel the two pages of data loaded into the data buffer into the appropriate memory pages. It is started by issuing a the Program Confirm command.

As for standard page program operation, the device supports random data input during both data loading phases.

Once the multiplane page program operation has started, that is during a delay of tipessy, the Status Register can be read using the Read Status Register command.

Once the multiplane page program operation has completed, the P/E/R Controller bit SR6 is set to '1' and the Ready/Busy signal goes High.

If the multiplane page program fails, an error is signaled on bit SR0 of the Status Register. To know which page of the two planes failed, the Read Status Enhanced command must be issued twice, once for each plane (see Section 6.12).

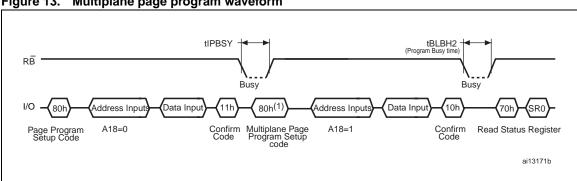

Figure 13 provides a description of multiplane page program waveforms.

Figure 13. Multiplane page program waveform

1. The 81h setup code is also accepted for backward compatibility.

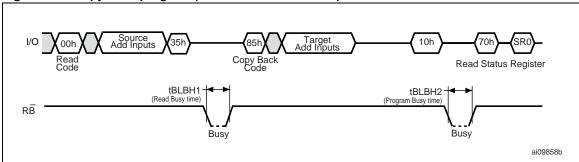

### 6.5 Copy back program

The copy back program operation copies the data stored in one page and reprograms it in another page.

The copy back program operation does not require external memory and so the operation is faster and more efficient because the reading and loading cycles are not required. The operation is particularly useful when a portion of a block is updated and the rest of the block needs to be copied to the newly assigned block.

The NAND04G-B2D and NAND08G-BxC devices feature automatic EDC during a copy back operation. Consequently, external ECC is no longer required. The errors detected during copy back operations can be read by performing a read EDC Status Register operation (see Section 6.13: Read EDC Status Register). See also Section 6.9 for details of EDC operations.

The copy back program operation requires the following four steps:

- The first step reads the source page. The operation copies all 2112 bytes from the page into the data buffer. It requires:

- One bus write cycle to set up the command

- 5 bus write cycles to input the source page address

- One bus write cycle to issue the confirm command code

- 2. When the device returns to the ready state (Ready/Busy High), optional data readout is allowed by pulsing  $\overline{R}$ ; the next bus write cycle of the command is given with the 5 bus cycles to input the target page address. See *Table 11* for the addresses that must be the same for the source and target page.

- Issue the confirm command to start the P/E/R Controller.

To see the data input cycle for modifying the source page and an example of the copy back program operation, refer to *Figure 14: Copy back program (without readout of data)*.

Figure 16: Page copy back program with random data input shows a data input cycle to modify a portion or a multiple distant portion of the source page.

Table 11. Copy back program addresses

| Density | Source and target page addresses |

|---------|----------------------------------|

| 4 Gbits | Same A18                         |

| 8 Gbits | Same A18 and A30                 |

Figure 14. Copy back program (without readout of data)

1. Copy back program is only permitted between odd address pages or even address pages.

4

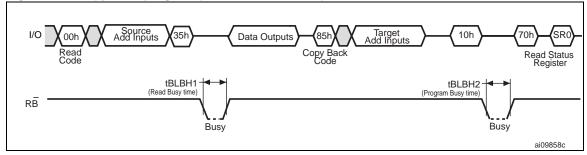

Figure 15. Copy back program (with readout of data)

Figure 16. Page copy back program with random data input

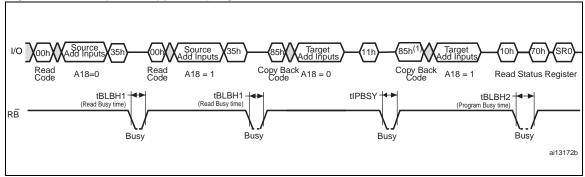

### 6.6 Multiplane copy back program

In addition to multiplane page program, the NAND04G-B2D and NAND08G-BxC devices support multiplane copy back program.

A Multiplane Copy Back Program command requires exactly the same steps as a Multiplane Page Program command, and must satisfy the same time constraints (see Section 6.4: Multiplane page program).

Prior to executing the multiplane copy back program operation, two single-page read operations must be executed to copy back the first page from the first plane and the second page from the second plane.

The EDC check is also performed during the multiplane copy back program. Errors during multiplane copy back operations can be detected by performing a Read EDC Status Register operation (see Section 6.13: Read EDC Status Register).

If the multiplane copy back program fails, an error is signaled on bit SR0 of the Status Register. To know which page of the two planes failed, the Read Status Enhanced command must be executed twice, once for each plane (see Section 6.12).

Figure 17 provides a description of multiplane copy back program waveform.

Figure 17. Multiplane copy back program

1. The 81h setup code is also accepted for backward compatibility.

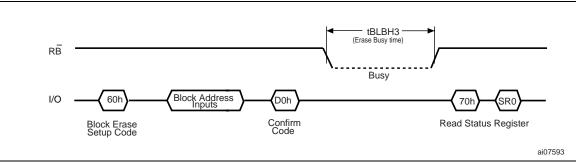

#### 6.7 Block erase

Erase operations are done one block at a time. An erase operation sets all of the bits in the addressed block to '1'. All previous data in the block is lost.

An erase operation consists of the following three steps (refer to Figure 18: Block erase):

- 1. One bus cycle is required to set up the Block Erase command. Only addresses A18-A29 are used; all other address inputs are ignored.

- 2. Three bus cycles are then required to load the address of the block to be erased. Refer to *Table 8: Address definition (x8 devices)* for the block addresses of each device.

- One bus cycle is required to issue the Block Erase Confirm command to start the P/E/R Controller.

The operation is initiated on the rising edge of Write Enable,  $\overline{W}$ , after the Confirm command is issued. The P/E/R Controller handles block erase and implements the verify process.

During the block erase operation, only the Read Status Register and Reset commands are accepted; all other commands are ignored.

Once the program operation has completed, the P/E/R Controller bit SR6 is set to '1' and the Ready/Busy signal goes High. If the operation completed successfully, the Write Status bit SR0 is '0', otherwise it is set to '1'.

Figure 18. Block erase

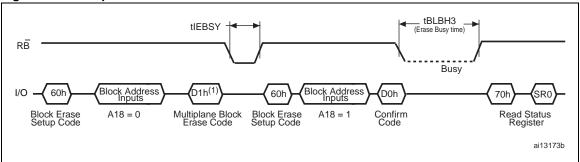

### 6.8 Multiplane block erase

The multiplane block erase operation allows the erasure of two blocks in parallel, one in each plane.

This operation consists of the following three steps (refer to *Figure 19: Multiplane block erase*):

- 8 bus cycles are required to set up the Block Erase command and load the addresses of the blocks to be erased. The setup command followed by the address of the block to be erased must be issued for each block. t<sub>IEBSY</sub> busy time is required between the insertion of first and the second block addresses. As for multiplane page program operations, the address of the first and second page must be within the first plane (A18 = 0) and second plane (A8 = 1), respectively.

- 2. One bus cycle is then required to issue the Multiplane Block Erase Confirm command and start the P/E/R Controller.

If the multiplane block erase fails, an error is signaled on bit SR0 of the Status Register. To know which page of the two planes failed, the Read Status Enhanced command must be issued twice, once for each plane (see *Section 6.12*).

Figure 19. Multiplane block erase

The D1h Confirm code is required by the ONFI 1.0 command set. To maintain backward compatibility, the D1h Confirm code can optionally be ignored, and then the tIEBSY Busy Time does not occur.

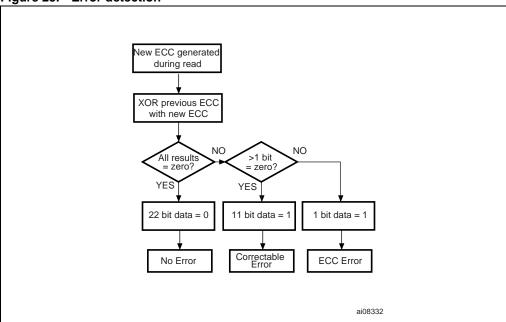

## 6.9 Error detection code (EDC)

The EDC (error detection code) is performed automatically during all program operations. It starts immediately after the device becomes busy.

The EDC detects 1 single bit error per EDC unit. Each EDC unit has a density of 528 bytes (or 264 words), split into 512 bytes of main area and 16 bytes of spare area (or 256 + 8 words). Refer to *Table 12* and *Figure 20* for EDC unit addresses definition.

To properly use the EDC, the following conditions apply:

- Page program operations must be performed on a whole page, or on whole EDC unit(s).

- The modification of the content of an EDC unit using a random data input before the copy back program, must be performed on the whole EDC unit. It can only be done once per EDC unit. Any partial modification of the EDC unit results in the corruption of the on-chip EDCs.

EDC results can be retrieved only during copy back program and multiplane copy back using the Read EDC Status Register command (see Section 6.13).

Figure 20. Page organization

Table 12. Address definition for EDC units (x8 devices)

| EDC unit              | Main      | area           | Spare area |                |  |

|-----------------------|-----------|----------------|------------|----------------|--|

| EDC unit              | Area name | Column address | Area name  | Column address |  |

| 1st 528-byte EDC unit | А         | 0 to 511       | E          | 2048 to 2063   |  |

| 2nd 528-byte EDC unit | В         | 512 to 1023    | F          | 2064 to 2079   |  |

| 3rd 528-byte EDC unit | С         | 1024 to1535    | G          | 2080 to 2095   |  |

| 4th 528-byte EDC unit | D         | 1536 to 2047   | Н          | 2096 to 2111   |  |

Table 13. Address definition for EDC units (x16 devices)

| EDC unit              | Main                     | area        | Spare area |                |  |

|-----------------------|--------------------------|-------------|------------|----------------|--|

| EDC unit              | Area name Column address |             | Area name  | Column address |  |

| 1st 264-word EDC unit | А                        | 0 to 255    | E          | 1024 to 1031   |  |

| 2nd 264-word EDC unit | В                        | 256 to 511  | F          | 1032 to 1039   |  |

| 3rd 264-word EDC unit | С                        | 512 to 767  | G          | 1040 to 1047   |  |

| 4th 264-word EDC unit | D                        | 768 to 1023 | Н          | 1048 to 1055   |  |

#### 6.10 Reset

The Reset command is used to reset the command interface and Status Register. If the Reset command is issued during any operation, the operation is aborted. If the aborted operation is a program or erase, the contents of the memory locations being modified are no longer valid as the data is partially programmed or erased.

If the device has already been reset, then the new Reset command is not accepted.

The Ready/Busy signal goes Low for  $t_{BLBH4}$  after the Reset command is issued. The value of  $t_{BLBH4}$  depends on the operation that the device was performing when the command was issued. Refer to *Table 31* for the values.

### 6.11 Read Status Register

The devices contain a Status Register that provides information on the current or previous program or erase operation. The various bits in the Status Register convey information and errors on the operation.

The Status Register is read by issuing the Read Status Register command. The Status Register information is present on the output data bus (I/O0-I/O7) on the falling edge of Chip Enable or Read Enable, whichever occurs last. When several memories are connected in a system, the use of Chip Enable and Read Enable signals allows the system to poll each device separately, even when the Ready/Busy pins are common-wired. It is not necessary to toggle the Chip Enable or Read Enable signals to update the contents of the Status Register.

After the Read Status Register command has been issued, the device remains in Read Status Register mode until another command is issued. Therefore, if a Read Status Register command is issued during a Random Read cycle, a new Read command must be issued to continue with a page read operation.

The Status Register bits are summarized in *Table 14: Status Register bits*. Refer to *Table 14* in conjunction with the following sections.

#### 6.11.1 Write protection bit (SR7)

The write protection bit identifies if the device is protected or not. If the write protection bit is set to '1', the device is not protected and program or erase operations are allowed. If the write protection bit is set to '0' the device is protected and program or erase operations are not allowed.

#### 6.11.2 P/E/R Controller and cache ready/busy bit (SR6)

Status Register bit SR6 has two different functions depending on the current operation.

During cache operations, SR6 acts as a cache ready/busy bit, which indicates whether the Cache Register is ready to accept new data. When SR6 is set to '0', the Cache Register is busy, and when SR6 is set to '1', the Cache Register is ready to accept new data.

During all other operations, SR6 acts as a P/E/R Controller bit, which indicates whether the P/E/R Controller is active or inactive. When the P/E/R Controller bit is set to '0', the P/E/R Controller is active (device is busy); when the bit is set to '1', the P/E/R Controller is inactive (device is ready).

#### 6.11.3 P/E/R Controller bit (SR5)

The Program/Erase/Read Controller bit indicates whether the P/E/R Controller is active or inactive during cache operations. When the P/E/R Controller bit is set to '0', the P/E/R Controller is active (device is busy); when the bit is set to '1', the P/E/R Controller is inactive (device is ready).

Note: This bit is only valid for cache operations.

#### 6.11.4 Error bit (SR0)

The error bit identifies if any errors have been detected by the P/E/R Controller. The error bit is set to '1' when a program or erase operation has failed to write the correct data to the memory. If the error bit is set to '0' the operation has completed successfully.

577

#### 6.11.5 SR4, SR3, SR2 and SR1 are reserved

Table 14. Status Register bits

| Bit                   | Name                                            | Logic level  | Definition                              |

|-----------------------|-------------------------------------------------|--------------|-----------------------------------------|

| SR7                   | Write protection                                | '1'          | Not protected                           |

| SK7                   | Write protection                                | '0'          | Protected                               |

| SR6                   | Program/Erase/Read                              | '1'          | P/E/R Controller inactive, device ready |

|                       | Controller                                      | '0'          | P/E/R Controller active, device busy    |

| SR5                   | Program/Erase/Read<br>Controller <sup>(1)</sup> | '1'          | P/E/R Controller inactive, device ready |

|                       |                                                 | '0'          | P/E/R Controller active, device busy    |

| SR4, SR3,<br>SR2, SR1 | Reserved                                        | 'don't care' |                                         |

| SR0                   | Generic error                                   | '1'          | Error – operation failed                |

| SKU                   | Generic error                                   | '0'          | No error – operation successful         |

<sup>1.</sup> Only valid for cache operations.

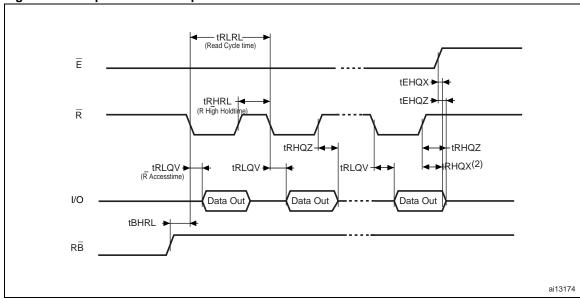

#### 6.12 Read status enhanced

In NAND Flash devices with multiplane architecture, it is possible to independently read the Status Register of a single plane using the Read Status Enhanced command. If the Error bit of the Status Register, SR0, reports an error during or after a multiplane operation, the Read Status Enhanced command is used to know which of the two planes contains the page that failed the operation. Three address cycles are required to address the selected block and page (A18-0).

The output of the Read Status Enhanced command has the same coding as the Read Status command. See *Table 14* for a full description and *Figure 31* for the read status enhanced waveform.

## 6.13 Read EDC Status Register

The devices contain an EDC Status Register, which provides information on the errors that occurred during the read cycles of the copy back and multiplane copy back operations. In the case of multiplane copy back program, it is not possible to distinguish which of the two read operations caused the error.

The EDCS Status Register is read by issuing the Read EDC Status Register command.

After issuing the Read EDC Status Register command, a read cycle outputs the content of the EDC Status Register to the I/O pins on the falling edge of Chip Enable or Read Enable signals, whichever occurs last. The operation is similar to Read Status Register command.

*Table 15: EDC Status Register bits* summarizes the EDC Status Register bits. See *Figure 30* for a description of Read EDC Status Register waveforms.

Table 15. EDC Status Register bits

| Bit | Name                      | Logic level  | Definition                                            |

|-----|---------------------------|--------------|-------------------------------------------------------|

|     | Pass/fail                 | '1'          | Copy back or multiplane copy back operation failed    |

| 0   |                           | '0'          | Copy back or multiplane copy back operation succeeded |

| 1   | EDC status                | '1'          | Error                                                 |

| '   |                           | '0'          | No error                                              |

| 2   | EDC validity              | '1'          | Valid                                                 |

| 2   |                           | '0'          | Invalid                                               |

| 3   | Reserved                  | 'don't care' | -                                                     |

| 4   | Reserved                  | 'don't care' | -                                                     |

| 5   | Ready/busy <sup>(1)</sup> | '1'          | Ready                                                 |

| 5   |                           | '0'          | Busy                                                  |

| 6   | Ready/busy <sup>(1)</sup> | '1'          | Ready                                                 |

| O   |                           | '0'          | Busy                                                  |

| 7   | Write protect             | '1'          | Not protected                                         |

| 1   |                           | '0'          | Protected                                             |

<sup>1.</sup> See Table 14: Status Register bits for a description of SR5 and SR6 bits.

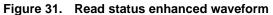

## 6.14 Read electronic signature

The devices contain a manufacturer code and device code. The following three steps are required to read these codes:

- 1. One bus write cycle to issue the Read Electronic Signature command (90h)

- 2. One bus write cycle to input the address (00h)

- 3. Five bus read cycles to sequentially output the data (as shown in *Table 16: Electronic signature*).

Table 16. Electronic signature

| Root part number                            | Byte 1 | Byte 2 | Byte 3 (see Table 17) | Byte 4 (see Table 18) | Byte 5 (see Table 19) |

|---------------------------------------------|--------|--------|-----------------------|-----------------------|-----------------------|

| NAND04GR3B2D<br>NAND08GR3B4C <sup>(1)</sup> | 20h    | ACh    | 10h                   | 15h                   | 54h                   |

| NAND04GW3B2D<br>NAND08GW3B4C <sup>(1)</sup> | 20h    | DCh    | 10h                   | 95h                   | 54h                   |

| NAND04GR4B2D                                | 0020h  | BCh    | 10h                   | 55h                   | 54h                   |

| NAND04GW4B2D                                | 0020h  | CCh    | 10h                   | D5h                   | 54h                   |

| NAND08GR3B2C                                | 20h    | A3h    | 51h                   | 15h                   | 58h                   |

| NAND08GW3B2C                                | 20h    | D3h    | 51h                   | 95h                   | 58h                   |

| NAND08GR4B2C                                | 0020h  | B3h    | 51h                   | 55h                   | 58h                   |

| NAND08GW4B2C                                | 0020h  | C3h    | 51h                   | D5h                   | 58h                   |

<sup>1.</sup> For NAND08G-B4C devices, each 4 Gb die returns its own electronic signature.

Table 17. Electronic signature byte 3

| 1/0       | Definition                                | Value | Description   |

|-----------|-------------------------------------------|-------|---------------|

|           |                                           | 0 0   | 1             |

| 1/04 1/00 | lataraal ahin numahar                     | 0 1   | 2             |

| I/O1-I/O0 | Internal chip number                      | 1 0   | 4             |

|           |                                           | 1 1   | 8             |

|           |                                           | 0 0   | 2-level cell  |

| I/O3-I/O2 | Call turns                                | 0 1   | 4-level cell  |

| 1/03-1/02 | Cell type                                 | 1 0   | 8-level cell  |

|           |                                           | 1 1   | 16-level cell |

|           |                                           | 0 0   | 1             |

| 1/05-1/04 | Number of simultaneously programmed pages | 0 1   | 2             |

| 1/05-1/04 |                                           | 1 0   | 4             |

|           |                                           | 1 1   | 8             |

| 1/00      | Interleaved programming                   | 0     | Not supported |

| I/O6      | between multiple devices                  | 1     | Supported     |

| 1/07      | Cacho program                             | 0     | Not supported |

| 1/07      | Cache program                             | 1     | Supported     |

Table 18. Electronic signature byte 4

| 1/0        | Definition                     | Value | Description |

|------------|--------------------------------|-------|-------------|

|            |                                | 0 0   | 1 Kbytes    |

| I/O1-I/O0  | Page size                      | 0 1   | 2 Kbytes    |

| 1/01-1/00  | (without spare area)           | 1 0   | 4 Kbytes    |

|            |                                | 1 1   | 8 Kbytes    |

| 1/02       | Spare area size                | 0     | 8           |

| 1/02       | (byte/512 byte)                | 1     | 16          |

|            |                                | 0 0   | 30/50 ns    |

| 1/07 1/02  | Minimum sequential access time | 1 0   | 25 ns       |

| I/O7, I/O3 |                                | 0 1   | Reserved    |