# **ULTRA LOW POWER SIX-CHANNEL DIGITAL ISOLATOR**

#### Features

- High-speed operation: DC - 150 Mbps

- Low propagation delay: <10 ns typical

- Wide Operating Supply Voltage: 2.75-5.5 V

- Ultra low power

- 5 V Operation:

- <1.25 mA per channel at 1 Mbps ∎</li>

- <2 mA per channel at 10 Mbps

- <6 mA per channel at 100 Mbps

- 2.75 V Operation:

- <1.25 mA per channel at 1 Mbps RoHS-compliant

- <2 mA per channel at 10 Mbps

- <4 mA per channel at 100 Mbps

#### Applications

- Isolated switch mode supplies

- Isolated ADC, DAC

- Safety Regulatory Approvals\*

- UL recognition: 2500 V<sub>RMS</sub> for 1 Minute per UL1577

- CSA component acceptance notice

- VDE certification conformity • IEC 60747-5-2

- (VDE0884 Part 2)

#### Description

Silicon Lab's family of ultra low power digital isolators are CMOS devices that employ an RF coupler to transmit digital information across an isolation barrier. Very high speed operation at low power levels is achieved. These devices are available in a 16-pin narrow body SOIC package. Two speed grade options (1 and 150 Mbps) are available and achieve typical propagation delays of less than 10 ns.

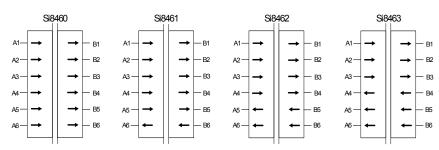

#### Block Diagram

\*Note: Pending.

Rev. 0.1 2/09 Copyright © 2009 by Silicon Laboratories Si8460/61/62/63 This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

- Precise timing: 2 ns pulse width distortion 1 ns channel-channel matching 2 ns pulse width skew

- Up to 2500 V<sub>RMS</sub> isolation Transient Immunity: 25 kV/µs

- DC correct -

- No start-up initialization required

- <30 µs startup time

- High temperature operation: 125 °C at 150 Mbps

- Narrow body SOIC-16 package

Power factor correction systems

Motor control

# TABLE OF CONTENTS

# Section

# <u>Page</u>

| 1. Electrical Specifications                        |

|-----------------------------------------------------|

| 3. Application Information                          |

| ••                                                  |

| 3.1. Theory of Operation                            |

| 3.2. Eye Diagram                                    |

| 4. Layout Recommendations                           |

| 4.1. Supply Bypass                                  |

| 4.2. Input and Output Characteristics               |

| 4.3. RF Radiated Emissions                          |

| 4.4. RF Immunity and Common Mode Transient Immunity |

| 5. Pin Descriptions                                 |

| 6. Ordering Guide                                   |

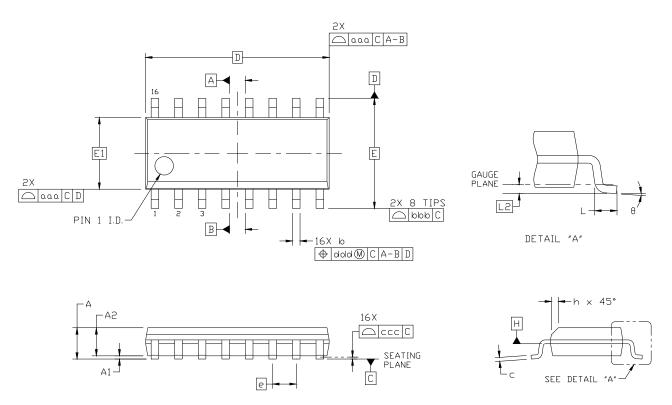

| 7. Package Outline: 16-Pin Narrow Body SOIC         |

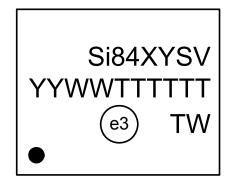

| 8. Top Marking                                      |

| Contact Information                                 |

# **1. Electrical Specifications**

### Table 1. Electrical Characteristics<sup>1</sup>

$(V_{DD1} = 5 V \pm 10\%, V_{DD2} = 5 V \pm 10\%, T_A = -40$  to 125 °C; applies to narrow-body SOIC package)

| Parameter                 | Symbol          | Test Condition        | Min                      | Тур             | Max   | Unit |

|---------------------------|-----------------|-----------------------|--------------------------|-----------------|-------|------|

| High Level Input Voltage  | V <sub>IH</sub> |                       | 2.0                      |                 | —     | V    |

| Low Level Input Voltage   | V <sub>IL</sub> |                       | —                        | —               | 0.8   | V    |

| High Level Output Voltage | V <sub>OH</sub> | loh = –4 mA           | $V_{DD1}, V_{DD2} - 0.4$ | 4.8             | —     | V    |

| Low Level Output Voltage  | V <sub>OL</sub> | lol = 4 mA            | —                        | 0.2             | 0.4   | V    |

| Input Leakage Current     | ١L              |                       | —                        | _               | ±10   | μA   |

| Output Impedance          | Z <sub>O</sub>  | VDD = 5 V, 25 °C      | —                        | 50 <sup>2</sup> | —     | Ω    |

|                           | DC Supply       | Current (All inputs ( | ) V or at Supply)        |                 |       |      |

| Si8460Ax, Bx              |                 |                       |                          |                 |       |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC       | _                        | 2               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC       | —                        | 3               | TBD   | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC       | _                        | 7               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC       | _                        | 3               | TBD   |      |

| Si8461Ax, Bx              |                 |                       |                          |                 |       |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC       | _                        | 2               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC       | _                        | 3               | TBD   | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC       | _                        | 7               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC       | _                        | 4               | TBD   |      |

| Si8462Ax, Bx              |                 |                       |                          | -               |       |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC       | _                        | 3               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC       |                          | 3               | TBD   | mA   |

|                           |                 | All inputs 1 DC       |                          | 6               | TBD   |      |

| V <sub>DD1</sub>          |                 | All inputs 1 DC       | _                        | 6               | TBD   |      |

| V <sub>DD2</sub>          |                 |                       |                          | 0               | ТБО   |      |

| Si8463Ax, Bx              |                 |                       |                          | 2               | тор   |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC       | —                        | 3               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC       | —                        | 3               | TBD   | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC       | —                        | 6               | TBD   |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC       | —                        | 6               | TBD   |      |

|                           | Current (All ii | nputs = 500 kHz squa  | are wave, CI = 15 pl     | - on all out    | puts) |      |

| Si8460Ax, Bx              |                 |                       |                          | _               |       |      |

| V <sub>DD1</sub>          |                 |                       | —                        | 5               | TBD   | mA   |

| V <sub>DD2</sub>          |                 |                       | —                        | 4               | TBD   |      |

| Si8461Ax, Bx              |                 |                       |                          |                 |       |      |

| V <sub>DD1</sub>          |                 |                       | —                        | 5               | TBD   | mA   |

| V <sub>DD2</sub>          |                 |                       | _                        | 4               | TBD   |      |

| Notes:                    |                 |                       |                          |                 |       | 1    |

2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be terminated with 50  $\Omega$  controlled impedance PCB traces.

**3.** t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

#### Table 1. Electrical Characteristics<sup>1</sup> (Continued)

$(V_{DD1} = 5 V \pm 10\%, V_{DD2} = 5 V \pm 10\%, T_A = -40 \text{ to } 125 \text{ °C}; \text{ applies to narrow-body SOIC package})$

| Parameter                            | Symbol                              | Test Condition      | Min                | Тур            | Max        | Unit |

|--------------------------------------|-------------------------------------|---------------------|--------------------|----------------|------------|------|

| Si8462Ax, Bx                         |                                     |                     |                    |                |            |      |

| V <sub>DD1</sub>                     |                                     |                     | —                  | 5              | TBD        | mA   |

| V <sub>DD2</sub>                     |                                     |                     | —                  | 4              | TBD        |      |

| Si8463Ax, Bx                         |                                     |                     |                    |                |            |      |

| V <sub>DD1</sub>                     |                                     |                     |                    | 5              | TBD        | mA   |

| V <sub>DD2</sub>                     |                                     |                     | —                  | 4              | TBD        |      |

|                                      | y Current (All                      | inputs = 50 MHz squ | uare wave, CI = 15 | 5 pF on all ou | itputs)    |      |

| Si8460Bx                             |                                     |                     |                    |                |            |      |

| V <sub>DD1</sub>                     |                                     |                     |                    | 7              | TBD        | mA   |

| V <sub>DD2</sub>                     |                                     |                     | —                  | 28             | TBD        |      |

| Si8461Bx                             |                                     |                     |                    |                |            |      |

| V <sub>DD1</sub>                     |                                     |                     |                    | 14             | TBD        | mA   |

| V <sub>DD2</sub>                     |                                     |                     |                    | 33             | TBD        |      |

| Si8462Bx                             |                                     |                     |                    | 20             | тор        |      |

| V <sub>DD1</sub>                     |                                     |                     | _                  | 20<br>27       | TBD<br>TBD | mA   |

| V <sub>DD2</sub><br>Si8463Bx         |                                     |                     |                    | 21             |            |      |

|                                      |                                     |                     |                    | 18             | TBD        | mA   |

| V <sub>DD1</sub><br>V <sub>DD2</sub> |                                     |                     | _                  | 18             | TBD        |      |

| • 002                                |                                     | Timing Characteris  | stics              | 10             | 100        |      |

| Si846xA                              |                                     | Thining Characteris | 51105              |                |            |      |

| Maximum Data Rate                    |                                     |                     | 0                  |                | 1          | Mhno |

|                                      |                                     |                     | 0                  |                |            | Mbps |

| Minimum Pulse Width                  |                                     |                     | —                  |                | 250        | ns   |

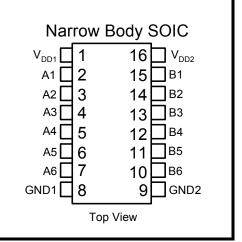

| Propagation Delay                    | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 1        |                    |                | 35         | ns   |

| Pulse Width Distortion               | PWD                                 | See Figure 1        | —                  | —              | 25         | ns   |

| It <sub>PLH</sub> - t <sub>PHL</sub> |                                     |                     |                    |                |            |      |

| Propagation Delay Skew <sup>3</sup>  | t <sub>PSK(P-P)</sub>               |                     | —                  | —              | 40         | ns   |

| Channel-Channel Skew                 | t <sub>PSK</sub>                    |                     | —                  | —              | 35         | ns   |

| Si846xB                              |                                     |                     |                    |                |            |      |

| Maximum Data Rate                    |                                     |                     | 0                  |                | 150        | Mbps |

| Minimum Pulse Width                  |                                     |                     | —                  |                | 6          | ns   |

| Propagation Delay                    | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 1        | 5                  | 8              | 15         | ns   |

| Pulse Width Distortion               | PWD                                 | See Figure 1        |                    |                | 3          | ns   |

| t <sub>PLH</sub> - t <sub>PHL</sub>  |                                     | Ŭ                   |                    |                |            |      |

| Propagation Delay Skew <sup>3</sup>  | t <sub>PSK(P-P)</sub>               |                     | —                  | <u> </u>       | 10         | ns   |

| Notes:                               | 1 01(11)                            |                     |                    |                |            |      |

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be terminated with 50  $\Omega$  controlled impedance PCB traces.

3. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

#### Table 1. Electrical Characteristics<sup>1</sup> (Continued)

(V<sub>DD1</sub> = 5 V±10%, V<sub>DD2</sub> = 5 V±10%, T<sub>A</sub> = -40 to 125 °C; applies to narrow-body SOIC package)

| Parameter                         | Symbol           | Test Condition                           | Min | Тур      | Мах | Unit  |

|-----------------------------------|------------------|------------------------------------------|-----|----------|-----|-------|

| Channel-Channel Skew              | t <sub>PSK</sub> |                                          | —   | —        | 3   | ns    |

| For All Models                    |                  |                                          | l   | <b>I</b> |     |       |

| Output Rise Time                  | t <sub>r</sub>   | C <sub>L</sub> = 15 pF<br>See Figure 1   | _   | 2        | _   | ns    |

| Output Fall Time                  | t <sub>f</sub>   | C <sub>L</sub> = 15 pF<br>See Figure 1   | —   | 2        | _   | ns    |

| Common Mode Transient<br>Immunity | CMTI             | $V_{I} = V_{DD} \text{ or } 0 \text{ V}$ | 20  | 25       | _   | kV/µs |

| Start-up Time <sup>4</sup>        | t <sub>SU</sub>  |                                          | —   | 30       | —   | μs    |

#### Notes:

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be terminated with 50  $\Omega$  controlled impedance PCB traces.

**3.** t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

Figure 1. Propagation Delay Timing

# Table 2. Electrical Characteristics<sup>1</sup>

$(V_{DD1} = 3.3 \text{ V}\pm 10\%, V_{DD2} = 3.3 \text{ V}\pm 10\%, T_A = -40 \text{ to } 125 \text{ °C}; \text{ applies to narrow-body SOIC package})$

| Parameter                                        | Symbol                | Test Condition        | Min                      | Тур        | Max   | Uni |

|--------------------------------------------------|-----------------------|-----------------------|--------------------------|------------|-------|-----|

| High Level Input Voltage                         | V <sub>IH</sub>       |                       | 2.0                      |            | —     | V   |

| Low Level Input Voltage                          | V <sub>IL</sub>       |                       | —                        |            | 0.8   | V   |

| High Level Output Voltage                        | V <sub>OH</sub>       | loh = –4 mA           | $V_{DD1}, V_{DD2} - 0.4$ | 3.1        | —     | V   |

| Low Level Output Voltage                         | V <sub>OL</sub>       | lol = 4 mA            | —                        | 0.2        | 0.4   | V   |

| Input Leakage Current                            | ΙL                    |                       | —                        | _          | ±10   | μA  |

|                                                  | DC Supply Cu          | Irrent (All inputs 0  | V or at supply)          |            |       |     |

| Si8460Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       | All inputs 0 DC       | —                        | 2          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   | mA  |

| V <sub>DD1</sub>                                 |                       | All inputs 1 DC       | —                        | 7          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 1 DC       | —                        | 3          | TBD   |     |

| Si8461Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       | All inputs 0 DC       | —                        | 2          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   | mA  |

| V <sub>DD1</sub>                                 |                       | All inputs 1 DC       | —                        | 7          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 1 DC       | —                        | 4          | TBD   |     |

| Si8462Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   | mA  |

| V <sub>DD1</sub>                                 |                       | All inputs 1 DC       |                          | 6          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 1 DC       | —                        | 6          | TBD   |     |

| Si8463Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 0 DC       | —                        | 3          | TBD   | mA  |

| V <sub>DD1</sub>                                 |                       | All inputs 1 DC       | —                        | 6          | TBD   |     |

| V <sub>DD2</sub>                                 |                       | All inputs 1 DC       | —                        | 6          | TBD   |     |

| 1 Mbps Supply                                    | Current (All inpu     | ts = 500 kHz squar    | e wave, CI = 15 pF       | on all out | puts) |     |

| Si8460Ax, Bx                                     |                       |                       |                          | _          |       |     |

| V <sub>DD1</sub>                                 |                       |                       | _                        | 5          | TBD   | mA  |

| V <sub>DD2</sub>                                 |                       |                       | —                        | 4          | TBD   |     |

| Si8461Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       |                       | —                        | 5          | TBD   | mA  |

| V <sub>DD2</sub>                                 |                       |                       | —                        | 4          | TBD   |     |

| Si8462Ax, Bx                                     |                       |                       |                          |            |       |     |

| V <sub>DD1</sub>                                 |                       |                       | —                        | 5          | TBD   | mA  |

| V <sub>DD2</sub>                                 |                       |                       | -                        | 4          | TBD   | 1   |

| VDD2<br>Notes:<br>1. Electrical specification va | alues are preliminary | Various specification |                          |            |       |     |

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

# Si8460/61/62/63

### Table 2. Electrical Characteristics<sup>1</sup> (Continued)

$(V_{DD1} = 3.3 \text{ V}\pm 10\%, \text{ V}_{DD2} = 3.3 \text{ V}\pm 10\%, \text{ T}_{A} = -40 \text{ to } 125 \text{ °C}; \text{ applies to narrow-body SOIC package})$

| Parameter                                                                    | Symbol                              | Test Condition                         | Min             | Тур          | Max        | Unit |

|------------------------------------------------------------------------------|-------------------------------------|----------------------------------------|-----------------|--------------|------------|------|

| Si8463Ax, Bx                                                                 |                                     |                                        |                 |              | ł          |      |

| V <sub>DD1</sub>                                                             |                                     |                                        | —               | 5            | TBD        | mA   |

| V <sub>DD2</sub>                                                             |                                     |                                        |                 | 4            | TBD        |      |

|                                                                              | Current (All inp                    | uts = 50 MHz square                    | e wave, CI = 15 | pF on all ou | tputs)     |      |

| Si8460Bx                                                                     |                                     |                                        |                 |              |            |      |

| V <sub>DD1</sub>                                                             |                                     |                                        | —               | 6<br>21      | TBD<br>TBD | mA   |

| V <sub>DD2</sub><br>Si8461Bx                                                 |                                     |                                        | —               | 21           | ТБО        |      |

| V <sub>DD1</sub>                                                             |                                     |                                        | _               | 10           | TBD        | mA   |

| V <sub>DD2</sub>                                                             |                                     |                                        | _               | 19           | TBD        |      |

| Si8462Bx                                                                     |                                     |                                        |                 |              |            |      |

| V <sub>DD1</sub>                                                             |                                     |                                        | —               | 12           | TBD        | mA   |

| V <sub>DD2</sub>                                                             |                                     |                                        |                 | 16           | TBD        |      |

| Si8463Bx                                                                     |                                     |                                        |                 |              |            |      |

| V <sub>DD1</sub>                                                             |                                     |                                        | —               | 13<br>13     | TBD<br>TBD | mA   |

| V <sub>DD2</sub>                                                             |                                     | nin a Charactariatia                   |                 | 13           | ТБО        |      |

| 0.040-4                                                                      | 110                                 | ning Characteristic                    | 5               |              |            |      |

| Si846xA                                                                      |                                     |                                        |                 |              |            |      |

| Maximum Data Rate                                                            |                                     |                                        | 0               |              | 1          | Mbps |

| Minimum Pulse Width                                                          |                                     |                                        |                 | —            | 250        | ns   |

| Propagation Delay                                                            | t <sub>PHL</sub> ,t <sub>PLH</sub>  | See Figure 1                           |                 | —            | 35         | ns   |

| Pulse Width Distortion                                                       | PWD                                 | See Figure 1                           | —               | —            | 25         | ns   |

| t <sub>PLH</sub> - t <sub>PHL</sub>  <br>Propagation Delay Skew <sup>2</sup> | +                                   |                                        |                 |              | 40         | ns   |

| Channel-Channel Skew                                                         | t <sub>PSK(P-P)</sub>               |                                        |                 |              | 35         | -    |

|                                                                              | t <sub>PSK</sub>                    |                                        |                 | _            | 35         | ns   |

| Si846xB                                                                      |                                     |                                        |                 |              | 1.50       |      |

| Maximum Data Rate                                                            |                                     |                                        | 0               |              | 150        | Mbps |

| Minimum Pulse Width                                                          |                                     |                                        |                 |              | 6          | ns   |

| Propagation Delay                                                            | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 1                           | 5               | 8            | 15         | ns   |

| Pulse Width Distortion                                                       | PWD                                 | See Figure 1                           | _               | _            | 3          | ns   |

| t <sub>PLH</sub> - t <sub>PHL</sub>                                          |                                     |                                        |                 |              | 40         |      |

| Propagation Delay Skew <sup>2</sup>                                          | t <sub>PSK(P-P)</sub>               |                                        |                 |              | 10         | ns   |

| Channel-Channel Skew                                                         | t <sub>PSK</sub>                    |                                        |                 |              | 3          | ns   |

| For All Models                                                               |                                     | · · · ·                                |                 | 1            | 1          | 1    |

| Output Rise Time                                                             | t <sub>r</sub>                      | C <sub>L</sub> = 15 pF<br>See Figure 1 | _               | 2            | -          | ns   |

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

Table 2. Electrical Characteristics<sup>1</sup> (Continued) $(V_{DD1} = 3.3 V \pm 10\%, V_{DD2} = 3.3 V \pm 10\%, T_A = -40$  to 125 °C; applies to narrow-body SOIC package)

| Parameter                                             | Symbol          | Test Condition                           | Min | Тур | Max | Unit  |

|-------------------------------------------------------|-----------------|------------------------------------------|-----|-----|-----|-------|

| Output Fall Time                                      | t <sub>f</sub>  | C <sub>L</sub> = 15 pF<br>See Figure 1   | _   | 2   | _   | ns    |

| Common Mode Transient<br>Immunity at Logic Low Output | CMTI            | $V_{I} = V_{DD} \text{ or } 0 \text{ V}$ | 20  | 25  | _   | kV/µs |

| Start-up Time <sup>3</sup>                            | t <sub>SU</sub> |                                          | _   | 30  | —   | μs    |

Notes:

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

#### Table 3. Electrical Characteristics<sup>1</sup>

(V<sub>DD1</sub> = 2.75 V, V<sub>DD2</sub> = 2.75 V, T<sub>A</sub> = -40 to 125 °C; applies to narrow-body SOIC package)

| Parameter                 | Symbol          | Test Condition       | Min                      | Тур | Max | Unit |

|---------------------------|-----------------|----------------------|--------------------------|-----|-----|------|

| High Level Input Voltage  | V <sub>IH</sub> |                      | 2.0                      |     |     | V    |

| Low Level Input Voltage   | V <sub>IL</sub> |                      | —                        |     | 0.8 | V    |

| High Level Output Voltage | V <sub>OH</sub> | loh = –4 mA          | $V_{DD1}, V_{DD2} - 0.4$ | 2.3 |     | V    |

| Low Level Output Voltage  | V <sub>OL</sub> | lol = 4 mA           | _                        | 0.2 | 0.4 | V    |

| Input Leakage Current     | ١L              |                      | —                        |     | ±10 | μA   |

|                           | DC Supply C     | urrent (All inputs 0 | V or at supply)          |     |     |      |

| Si8460Ax, Bx              |                 |                      |                          |     |     |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC      | —                        | 2   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC      | —                        | 3   | TBD | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC      | —                        | 7   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC      | —                        | 3   | TBD |      |

| Si8461Ax, Bx              |                 |                      |                          |     |     |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC      | —                        | 2   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC      |                          | 3   | TBD | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC      |                          | 7   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC      | _                        | 4   | TBD |      |

| Si8462Ax, Bx              |                 |                      |                          |     |     |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC      | _                        | 3   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC      |                          | 3   | TBD | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC      | _                        | 6   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC      | _                        | 6   | TBD |      |

| Si8463Ax, Bx              |                 |                      |                          |     |     |      |

| V <sub>DD1</sub>          |                 | All inputs 0 DC      |                          | 3   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 0 DC      |                          | 3   | TBD | mA   |

| V <sub>DD1</sub>          |                 | All inputs 1 DC      |                          | 6   | TBD |      |

| V <sub>DD2</sub>          |                 | All inputs 1 DC      | _                        | 6   | TBD |      |

|                           | urrent (All inp | uts = 500 kHz squar  | e wave. CI = 15 pF       |     |     |      |

| Si8460Ax, Bx              |                 | ,                    |                          |     | ,   |      |

| V <sub>DD1</sub>          |                 |                      |                          | 5   | TBD | mA   |

| V <sub>DD2</sub>          |                 |                      | _                        | 4   | TBD |      |

| Si8461Ax, Bx              |                 |                      |                          |     |     |      |

| V <sub>DD1</sub>          |                 |                      |                          | 5   | TBD | mA   |

| ▼ DD1<br>V===             |                 |                      |                          | 4   | TBD | 110  |

| V <sub>DD2</sub>          |                 |                      |                          | 7   |     |      |

| Si8462Ax, Bx              |                 |                      |                          | F   | TBD | ~^   |

| V <sub>DD1</sub>          |                 |                      |                          | 5   |     | mA   |

| V <sub>DD2</sub>          | 1               |                      |                          | 4   | TBD |      |

final product characterization data becomes available.

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

Table 3. Electrical Characteristics<sup>1</sup> (Continued)(V<sub>DD1</sub> = 2.75 V, V<sub>DD2</sub> = 2.75 V, T<sub>A</sub> = -40 to 125 °C; applies to narrow-body SOIC package)

| Parameter                            | Symbol                              | Test Condition         | Min              | Тур          | Max    | Unit |

|--------------------------------------|-------------------------------------|------------------------|------------------|--------------|--------|------|

| Si8463Ax, Bx                         |                                     |                        |                  |              |        |      |

| V <sub>DD1</sub>                     |                                     |                        | —                | 5            | TBD    | mA   |

| V <sub>DD2</sub>                     |                                     |                        | _                | 4            | TBD    |      |

| 100 Mbps Supply                      | y Current (All inp                  | outs = 50 MHz squar    | re wave, CI = 15 | pF on all ou | tputs) |      |

| Si8460Bx                             |                                     |                        |                  |              |        |      |

| V <sub>DD1</sub>                     |                                     |                        | —                | 6            | TBD    | mA   |

| V <sub>DD2</sub>                     |                                     |                        |                  | 18           | TBD    |      |

| Si8461Bx                             |                                     |                        |                  | 9            | TBD    | mA   |

| V <sub>DD1</sub><br>V <sub>DD2</sub> |                                     |                        | _                | 15           | TBD    | IIIA |

| Si8462Bx                             |                                     |                        |                  |              |        |      |

| V <sub>DD1</sub>                     |                                     |                        | _                | 11           | TBD    | mA   |

| V <sub>DD2</sub>                     |                                     |                        | —                | 13           | TBD    |      |

| Si8463Bx                             |                                     |                        |                  |              |        |      |

| V <sub>DD1</sub>                     |                                     |                        | —                | 12           | TBD    | mA   |

| V <sub>DD2</sub>                     |                                     |                        |                  | 12           | TBD    |      |

|                                      | Ti                                  | ming Characteristic    | CS               |              |        |      |

| Si846xA                              |                                     |                        |                  |              |        |      |

| Maximum Data Rate                    |                                     |                        | 0                | —            | 1      | Mbps |

| Minimum Pulse Width                  |                                     |                        |                  | _            | 250    | ns   |

| Propagation Delay                    | t <sub>PHL</sub> ,t <sub>PLH</sub>  | See Figure 1           |                  | _            | 35     | ns   |

| Pulse Width Distortion               | PWD                                 | See Figure 1           |                  |              | 25     | ns   |

| t <sub>PLH</sub> - t <sub>PHL</sub>  |                                     |                        |                  |              |        |      |

| Propagation Delay Skew <sup>2</sup>  | t <sub>PSK(P-P)</sub>               |                        | _                | —            | 40     | ns   |

| Channel-Channel Skew                 | t <sub>PSK</sub>                    |                        | _                | —            | 35     | ns   |

| Si846xB                              |                                     |                        |                  |              | •      |      |

| Maximum Data Rate                    |                                     |                        | 0                | —            | 150    | Mbps |

| Minimum Pulse Width                  |                                     |                        |                  |              | 6      | ns   |

| Propagation Delay                    | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 1           | 5                | 8            | 15     | ns   |

| Pulse Width Distortion               | PWD                                 | See Figure 1           |                  | <u> </u>     | 3      | ns   |

| t <sub>PLH</sub> - t <sub>PHL</sub>  |                                     | -                      |                  |              |        |      |

| Propagation Delay Skew <sup>2</sup>  | t <sub>PSK(P-P)</sub>               |                        |                  |              | 10     | ns   |

| Channel-Channel Skew                 | t <sub>PSK</sub>                    |                        | —                | —            | 3      | ns   |

| For All Models                       |                                     |                        | •                |              |        |      |

| Output Rise Time                     | t <sub>r</sub>                      | C <sub>L</sub> = 15 pF |                  | 2            | _      | ns   |

|                                      |                                     | See Figure 1           |                  |              |        |      |

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

### Table 3. Electrical Characteristics<sup>1</sup> (Continued)

(V<sub>DD1</sub> = 2.75 V, V<sub>DD2</sub> = 2.75 V, T<sub>A</sub> = -40 to 125 °C; applies to narrow-body SOIC package)

| Parameter                                             | Symbol          | Test Condition                           | Min | Тур | Мах | Unit  |

|-------------------------------------------------------|-----------------|------------------------------------------|-----|-----|-----|-------|

| Output Fall Time                                      | t <sub>f</sub>  | C <sub>L</sub> = 15 pF<br>See Figure 1   |     | 2   | _   | ns    |

| Common Mode Transient<br>Immunity at Logic Low Output | CMTI            | $V_{I} = V_{DD} \text{ or } 0 \text{ V}$ | 20  | 25  | _   | kV/µs |

| Start-up Time <sup>3</sup>                            | t <sub>SU</sub> |                                          |     | 30  | —   | μs    |

Notes:

1. Electrical specification values are preliminary. Various specifications will be adjusted to reflect actual performance as final product characterization data becomes available.

2. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

3. Start-up time is the time period from the application of power to valid data at the output.

#### **Table 4. Absolute Maximum Ratings**

|                                     |                                                                                           |                                                                                                                                          | Max                                                    | Unit                                                  |

|-------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|

| T <sub>STG</sub>                    | -65                                                                                       | —                                                                                                                                        | 150                                                    | °C                                                    |

| T <sub>A</sub>                      | -40                                                                                       | —                                                                                                                                        | 125                                                    | °C                                                    |

| V <sub>DD1</sub> , V <sub>DD2</sub> | -0.5                                                                                      | —                                                                                                                                        | 6                                                      | V                                                     |

| VI                                  | -0.5                                                                                      | —                                                                                                                                        | V <sub>DD</sub> + 0.5                                  | V                                                     |

| V <sub>O</sub>                      | -0.5                                                                                      |                                                                                                                                          | V <sub>DD</sub> + 0.5                                  | V                                                     |

| L <sub>O</sub>                      |                                                                                           |                                                                                                                                          | 10                                                     | mA                                                    |

|                                     |                                                                                           |                                                                                                                                          | 260                                                    | °C                                                    |

|                                     | _                                                                                         | —                                                                                                                                        | 3600                                                   | V <sub>RMS</sub>                                      |

|                                     | V <sub>DD1</sub> , V <sub>DD2</sub><br>V <sub>1</sub><br>V <sub>0</sub><br>L <sub>0</sub> | $\begin{array}{c c} V_{DD1}, V_{DD2} & -0.5 \\ \hline V_1 & -0.5 \\ \hline V_0 & -0.5 \\ \hline L_0 & \\ \hline & \\ \hline \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

should be restricted to conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum ratings for extended periods may degrade performance.

#### **Table 5. Recommended Operating Conditions**

| Parameter                      | Symbol           | Test Condition       | Min  | Тур | Max | Unit |

|--------------------------------|------------------|----------------------|------|-----|-----|------|

| Ambient Operating Temperature* | T <sub>A</sub>   | 150 Mbps, 15 pF, 5 V | -40  | 25  | 125 | °C   |

| Supply Voltage                 | V <sub>DD1</sub> |                      | 2.75 | _   | 5.5 | V    |

|                                | V <sub>DD2</sub> |                      | 2.75 | _   | 5.5 | V    |

#### Table 6. Regulatory Information\*

#### CSA

The Si846x is certified under CSA Component Acceptance Notice. For more details, see File 232873.

VDE

The Si846x is certified according to IEC 60747-5-2. For more details, see File 5006301-4880-0001.

UL

The Si846x is certified under UL1577 component recognition program. For more details, see File E257455.

\*Note: Pending. All 2.5 kV<sub>RMS</sub> rated devices are production tested to 3.6 kV<sub>RMS</sub> for 1 sec. For more information, see "6. Ordering Guide" on page 25.

#### Table 7. Insulation and Safety-Related Specifications

| Parameter                                        | Symbol          | Test Condition                   | Value            | Unit |

|--------------------------------------------------|-----------------|----------------------------------|------------------|------|

| Farameter                                        | Symbol          | lest condition                   | NB SOIC-16       | Onit |

| Minimum Air Gap (Clearance)                      | L(IO1)          |                                  | 5.0              | mm   |

| Minimum External Tracking (Creepage)             | L(IO2)          |                                  | 4.6              | mm   |

| Minimum Internal Gap (Internal Clearance)        |                 |                                  | 0.008            | mm   |

| Tracking Resistance (Comparative Tracking Index) | CTI             | DIN IEC 60112/VDE<br>0303 Part 1 | >175             | V    |

| Resistance (Input-Output) <sup>1</sup>           | R <sub>IO</sub> |                                  | 10 <sup>12</sup> | Ω    |

| Capacitance (Input-Output) <sup>1</sup>          | C <sub>IO</sub> | f = 1 MHz                        | 2                | pF   |

| Input Capacitance <sup>2</sup>                   | Cl              |                                  | 4.0              | pF   |

|                                                  |                 |                                  |                  |      |

Notes:

To determine resistance and capacitance, the Si846x is converted into a 2-terminal device. Pins 1–8 are shorted together to form the first terminal and pins 9–16 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

**2.** Measured from input pin to ground.

#### Table 8. IEC 60664-1 (VDE 0884 Part 2) Ratings

| Parameter                            | Test Conditions                             | Specification |

|--------------------------------------|---------------------------------------------|---------------|

| Basic isolation group Material Group |                                             | Illa          |

|                                      | Rated Mains Voltages ≤ 150 V <sub>RMS</sub> | I-IV          |

| Installation Classification          | Rated Mains Voltages ≤ 300 V <sub>RMS</sub> | I-III         |

|                                      | Rated Mains Voltages ≤ 400 V <sub>RMS</sub> | I-11          |

| Parameter                                                                                                                                                       | Symbol                                                                                                  | Test Condition                                                                                                                          | Characteristic        | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|

| Maximum Working Insulation Voltage                                                                                                                              | V <sub>IORM</sub>                                                                                       |                                                                                                                                         | 560                   | V peak |

|                                                                                                                                                                 |                                                                                                         | Method a<br>After Environmental Tests<br>Subgroup 1<br>$(V_{IORM} \times 1.6 = V_{PR}, t_m = 60 \text{ sec}, Partial Discharge < 5 pC)$ | 896                   |        |

| Input to Output Test Voltage                                                                                                                                    | Production Test, t <sub>m</sub> = 1 sec,<br>Partial Discharge < 5 pC)<br>After Input and/or Safety Test | 1050                                                                                                                                    | V peak                |        |

|                                                                                                                                                                 |                                                                                                         | Subgroup 2/3<br>( $V_{IORM} \times 1.2 = V_{PR}$ , t <sub>m</sub> = 60 sec,                                                             | 672                   |        |

| Highest Allowable Overvoltage (Transient<br>Overvoltage, t <sub>TR</sub> = 10 sec)                                                                              | V <sub>TR</sub>                                                                                         |                                                                                                                                         | 4000                  | V peak |

| Pollution Degree (DIN VDE 0110, Table 1)                                                                                                                        |                                                                                                         |                                                                                                                                         | 2                     |        |

| Insulation Resistance at $T_S$ , $V_{IO}$ = 500 V                                                                                                               | R <sub>S</sub>                                                                                          |                                                                                                                                         | >10 <sup>9</sup>      | Ω      |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V<br>*Note: This isolator is suitable for basic elect<br>ensured by protective circuits. The Si | rical isolatio                                                                                          |                                                                                                                                         | intenance of the safe |        |

#### Table 9. IEC 60747-5-2 Insulation Characteristics for Si846xxB\*

# Table 10. IEC Safety Limiting Values<sup>1</sup>

| Parameter                                                                                                      | Symbol         | Test Condition                                                                                                      | Min    | Tun | Max        | Unit |

|----------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|--------|-----|------------|------|

| Farameter                                                                                                      | Symbol         | lest Condition                                                                                                      | IVIIII | Тур | NB SOIC-16 | Unit |

| Case Temperature                                                                                               | Τ <sub>S</sub> |                                                                                                                     | —      | _   | 150        | °C   |

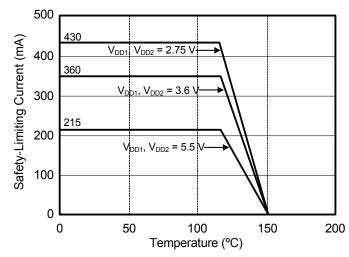

| Safety input, output, or supply current                                                                        | ۱ <sub>S</sub> | θ <sub>JA</sub> = 105 °C/W (NB SOIC-16),<br>V <sub>I</sub> = 5.5 V, T <sub>J</sub> = 150 °C, T <sub>A</sub> = 25 °C | -      | -   | 215        | mA   |

| Device Power Dissipation <sup>2</sup>                                                                          | P <sub>D</sub> |                                                                                                                     | —      |     | 415        | mW   |

| Notes:<br>1. Maximum value allowed in the event of a failure; also see the thermal derating curve in Figure 2. |                |                                                                                                                     |        |     |            |      |

Wraximum value anowed in the event of a failure; also see the thermal derating curve in Figure 2.

The Si8460 is tested with V<sub>DD1</sub> = V<sub>DD2</sub> = 5.5 V, T<sub>J</sub> = 150 °C, C<sub>L</sub> = 15 pF, input a 150 Mbps 50% duty cycle square wave.

#### **Table 11. Thermal Characteristics**

| Parameter                              | Symbol        | Test Condition                            | Min | Тур        | Max | Unit |

|----------------------------------------|---------------|-------------------------------------------|-----|------------|-----|------|

| i arameter                             | Symbol        |                                           |     | NB SOIC-16 | Wax | Onit |

| IC Junction-to-Case Thermal Resistance | θJC           | Thermocouple located at center of package | _   | 45         | _   | °C/W |

| IC Junction-to-Air Thermal Resistance  | $\theta_{JA}$ |                                           | —   | 105        | —   | °C/W |

Figure 2. (NB SOIC-16) Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN EN 60747-5-2

# 2. Typical Performance Characteristics

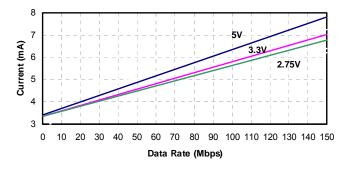

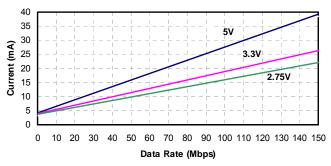

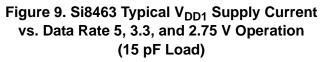

Figure 3. Si8460 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation

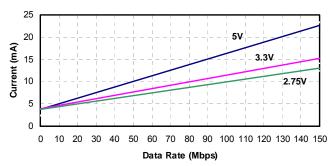

Figure 4. Si8460 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

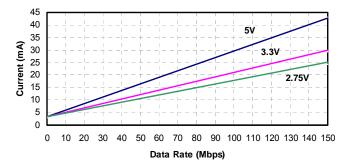

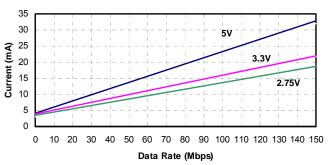

Figure 5. Si8461 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

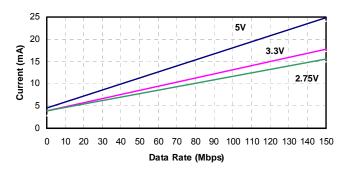

Figure 6. Si8461 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

Figure 7. Si8462 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

Figure 8. Si8462 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

16

# Si8460/61/62/63

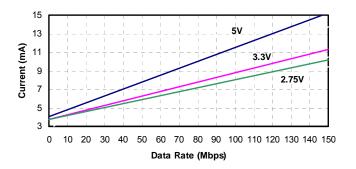

Figure 10. Si8463 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.75 V Operation (15 pF Load)

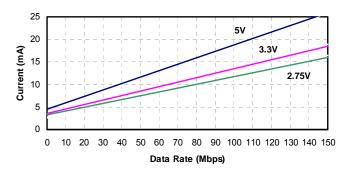

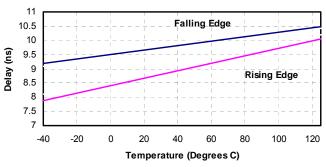

Figure 11. Propagation Delay vs. Temperature 5 V Operation

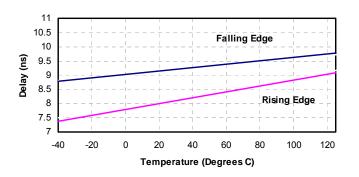

Figure 12. Propagation Delay vs. Temperature 3.3 V Operation

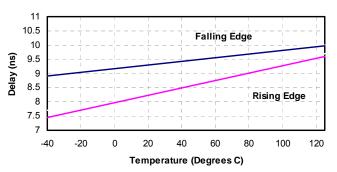

Figure 13. Propagation Delay vs. Temperature 2.75 V Operation

# 3. Application Information

### 3.1. Theory of Operation

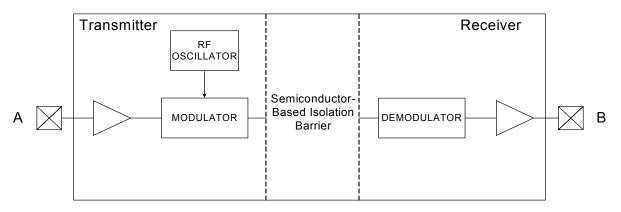

The operation of an Si846x channel is analogous to that of an opto coupler, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si846x channel is shown in Figure 14.

#### Figure 14. Simplified Channel Diagram

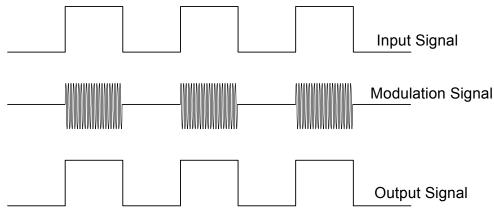

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See Figure 15 for more details.

Figure 15. Modulation Scheme

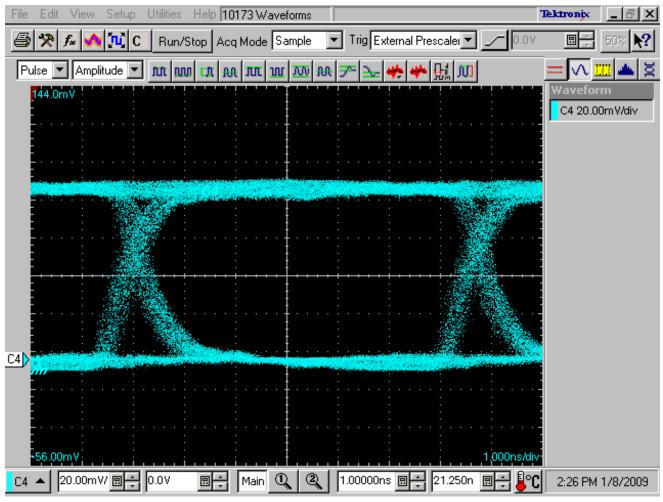

#### 3.2. Eye Diagram

Figure 16 illustrates an eye-diagram taken on an Si8460. For the data source, the test used an Anritsu (MP1763C) Pulse Pattern Generator set to 1000 ns/div. The output of the generator's clock and data from an Si8460 were captured on an oscilloscope. The results illustrate that data integrity was maintained even at the high data rate of 150 Mbps. The results also show that 2 ns pulse width distortion and 250 ps peak jitter were exhibited.

Figure 16. Eye Diagram

# 4. Layout Recommendations

Dielectric isolation is a set of specifications produced by the safety regulatory agencies from around the world that describes the physical construction of electrical equipment that derives power from a high-voltage power system such as 100–240  $V_{AC}$  systems or industrial power systems. The dielectric test (or HIPOT test) given in the safety specifications places a very high voltage between the input power pins of a product and the user circuits and the user touchable surfaces of the product. For the IEC relating to products deriving their power from the 220–240 V power grids, the test voltage is 2500  $V_{AC}$  (or 3750  $V_{DC}$ —the peak equivalent voltage).

There are two terms described in the safety specifications:

- Creepage—the distance along the insulating surface an arc may travel.

- Clearance—the distance through the shortest path through air that an arc may travel.

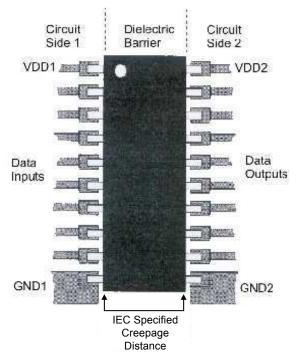

Figure 17 illustrates the accepted method of providing the proper creepage distance along the surface. For a 220–240  $V_{AC}$  application, this distance is 8 mm and the wide body SOIC package must be used. There must be no copper traces within this 8 mm exclusion area, and the surface should have a conformal coating such as solder resist. The digital isolator chip must straddle this exclusion area.

Figure 17. Creepage Distance

#### 4.1. Supply Bypass

The Si846x requires a 1  $\mu$ F bypass capacitor between V<sub>DD1</sub> and GND1 and V<sub>DD2</sub> and GND2. The capacitor should be placed as close as possible to the package.

### 4.2. Input and Output Characteristics

The Si846x inputs and outputs are standard CMOS drivers/receivers. Table 12 details powered and unpowered operation of the Si846x.

| V <sub>I</sub><br>Input <sup>1,2</sup> | VDDI<br>State <sup>1,3,4</sup> | VDDO<br>State <sup>1,3,4</sup> | V <sub>O</sub> Output <sup>1,2</sup> | Comments                                                                                                                                                 |

|----------------------------------------|--------------------------------|--------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н                                      | Р                              | Р                              | Н                                    | Enabled, normal operation                                                                                                                                |

| L                                      | Р                              | Р                              | L                                    |                                                                                                                                                          |

| Х                                      | Р                              | Р                              | Hi-Z                                 | Disabled                                                                                                                                                 |

| Х                                      | UP                             | Р                              | L                                    | Upon the transition of VDDI from unpowered to powered, $V_O$ returns to the same state as $V_I$ in less than 1 $\mu$ s.                                  |

| Х                                      | UP                             | Р                              | Hi-Z                                 | Disabled                                                                                                                                                 |

| Х                                      | Р                              | UP                             | L                                    | Upon the transition of VDDI from unpowered to powered, $V_O$ returns to the same state as $V_I$ in less than 1 µs, if EN is in either the H or NC state. |

| Notes:                                 |                                | 1                              | 1                                    |                                                                                                                                                          |

#### Table 12. Si846x Operation Table

VDDI and VDDO are the input and output power supplies. V<sub>I</sub> and V<sub>O</sub> are the respective input and output terminals.

X = not applicable; H = Logic High; L = Logic Low; Hi-Z = High Impedance.

3. "Powered" state (P) is defined as 2.75 V < VDD < 5.5 V.

4. "Unpowered" state (UP) is defined as VDD = 0 V.

### 4.3. RF Radiated Emissions

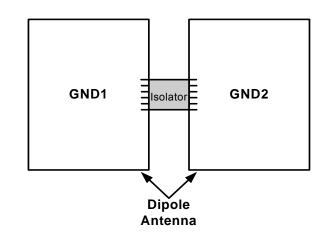

The Si846x family uses a RF carrier frequency of approximately 700 MHz. This results in a small amount of radiated emissions at this frequency and its harmonics. The radiation is not from the IC chip but due to a small amount of RF energy driving the isolated ground planes which can act as a dipole antenna.

The unshielded Si846x evaluation board passes FCC requirements. Table 13 shows measured emissions compared to FCC requirements.

Radiated emissions can be reduced if the circuit board is enclosed in a shielded enclosure or if the PCB is a less efficient antenna.

| Frequency<br>(GHz) | Measured<br>(dBµV/m)                                            | FCC Spec<br>(dBµV/m) | Compared<br>to Spec (dB) |  |  |  |

|--------------------|-----------------------------------------------------------------|----------------------|--------------------------|--|--|--|

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| TBD                | TBD                                                             | TBD                  | TBD                      |  |  |  |

| *Note: Data tal    | *Note: Data table to be updated pending final characterization. |                      |                          |  |  |  |

#### 4.4. RF Immunity and Common Mode Transient Immunity

The Si846x family has very high common mode transient immunity while transmitting data. This is typically measured by applying a square pulse with very fast rise/fall times between the isolated grounds. Measurements show no failures at 25 kV/ $\mu$ s. During a high surge event the output may glitch low for up to 20–30 ns, but the output corrects immediately after the surge event.

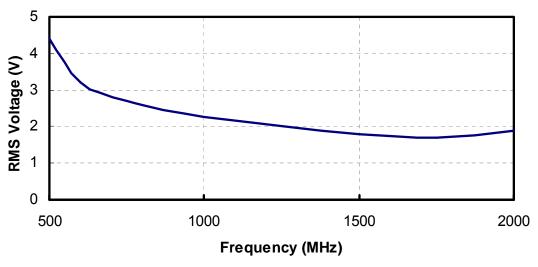

The Si846x family passes the industrial requirements of CISPR24 for RF immunity of 10 V/m using an unshielded evaluation board. As shown in Figure 18, the isolated ground planes form a parasitic dipole antenna, while Figure 19 shows the RMS common mode voltage versus frequency above which the Si846x becomes susceptible to data corruption. To avoid compromising data, care must be taken to keep RF common-mode voltage below the envelope specified in Figure 19. The PCB should be laid-out to not act as an efficient antenna for the RF frequency of interest. RF susceptibility is also significantly reduced when the end system is housed in a metal enclosure, or otherwise shielded.

Figure 18. Dipole Antenna

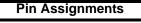

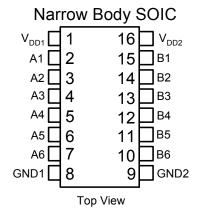

# 5. Pin Descriptions

| Name             | SOIC-16 Pin# | Туре           | Description                     |

|------------------|--------------|----------------|---------------------------------|

| V <sub>DD1</sub> | 1            | Supply         | Side 1 power supply.            |

| A1               | 2            | Digital Input  | Side 1 digital input.           |

| A2               | 3            | Digital Input  | Side 1 digital input.           |

| A3               | 4            | Digital Input  | Side 1 digital input.           |

| A4               | 5            | Digital I/O    | Side 1 digital input or output. |

| A5               | 6            | Digital I/O    | Side 1 digital input or output. |

| A6               | 7            | Digital I/O    | Side 1 digital input or output. |

| GND1             | 8            | Ground         | Side 1 ground.                  |

| GND2             | 9            | Ground         | Side 2 ground.                  |

| B6               | 10           | Digital I/O    | Side 2 digital input or output. |

| B5               | 11           | Digital I/O    | Side 2 digital input or output. |

| B4               | 12           | Digital I/O    | Side 2 digital input or output. |

| B3               | 13           | Digital Output | Side 2 digital output.          |

| B2               | 14           | Digital Output | Side 2 digital output.          |

| B1               | 15           | Digital Output | Side 2 digital output.          |

| V <sub>DD2</sub> | 16           | Supply         | Side 2 power supply.            |

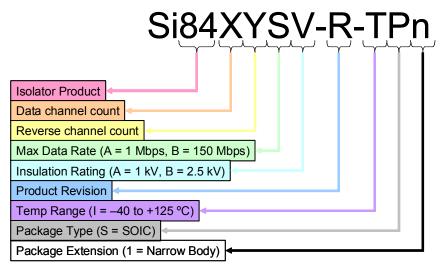

# 6. Ordering Guide

Figure 20. Ordering Part Number (OPN) Convention

| Ordering Part<br>Number (OPN)                                                                                                                                                                                       | Number of<br>Inputs<br>VDD1 Side | Number of<br>Inputs<br>VDD2 Side | Maximum<br>Data Rate<br>(Mbps) | Isolation<br>Rating | Temp Range    | Package<br>Type | Legacy Part<br>Equivalent |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|---------------------|---------------|-----------------|---------------------------|---|

| Si8460AA-A-IS1                                                                                                                                                                                                      | 6                                | 0                                | 1                              |                     |               |                 | —                         |   |

| Si8460BA-A-IS1                                                                                                                                                                                                      | 6                                | 0                                | 150                            |                     |               |                 | —                         |   |

| Si8461AA-A-IS1                                                                                                                                                                                                      | 5                                | 1                                | 1                              |                     |               |                 | —                         |   |

| Si8461BA-A-IS1                                                                                                                                                                                                      | 5                                | 1                                | 150                            | 1 kVrms             | –40 to 125 °C | NB SOIC-16      | —                         |   |

| Si8462AA-A-IS1                                                                                                                                                                                                      | 4                                | 2                                | 1                              | I KVIIIIS           | -4010125 C    | NB 5010-10      |                           |   |