### INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

# **74HC/HCT163**Presettable synchronous 4-bit binary counter; synchronous reset

Product specification

File under Integrated Circuits, IC06

December 1990

Philips Semiconductors

# 74HC/HCT163

#### **FEATURES**

- Synchronous counting and loading

- Two count enable inputs for n-bit cascading

- Positive-edge triggered clock

- · Synchronous reset

- · Output capability: standard

- · I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT163 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

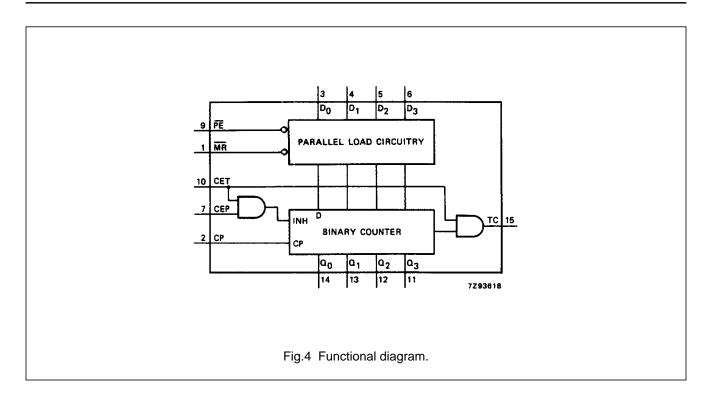

The 74HC/HCT163 are synchronous presettable binary counters which feature an internal look-ahead carry and can be used for high-speed counting.

Synchronous operation is provided by having all flip-flops clocked simultaneously on the positive-going edge of the clock (CP).

The outputs  $(Q_0 \text{ to } Q_3)$  of the counters may be preset to a HIGH or LOW level. A LOW level at the parallel enable input  $(\overline{PE})$  disables the counting action and causes the data at the data inputs  $(D_0 \text{ to } D_3)$  to be loaded into the counter on the positive-going edge of the clock (providing that the set-up and hold time requirements for  $\overline{PE}$  are met).

Preset takes place regardless of the levels at count enable inputs (CEP and CET).

For the "163" the clear function is synchronous.

A LOW level at the master reset input  $(\overline{MR})$  sets all four outputs of the flip-flops  $(Q_0 \text{ to } Q_3)$  to LOW level after the next positive-going transition on the clock (CP) input (provided that the set-up and hold time requirements for  $\overline{MR}$  are met). This action occurs regardless of the levels at  $\overline{PE}$ , CET and CEP inputs.

This synchronous reset feature enables the designer to modify the maximum count with only one external NAND gate.

The look-ahead carry simplifies serial cascading of the counters. Both count enable inputs (CEP and CET) must be HIGH to count. The CET input is fed forward to enable the terminal count output (TC). The TC output thus enabled will produce a HIGH output pulse of a duration approximately equal to a HIGH level output of Q<sub>0</sub>. This pulse can be used to enable the next cascaded stage.

The maximum clock frequency for the cascaded counters is determined by the CP to TC propagation delay and CEP to CP set-up time, according to the following formula:

$$f_{max} = \frac{1}{t_{P (max)} (CP \text{ to TC}) + t_{SU} (CEP \text{ to CP})}$$

### QUICK REFERENCE DATA

$GND = 0 V; T_{amb} = 25 °C; t_r = t_f = 6 ns$

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                       | TYI | PICAL | UNIT |

|-------------------------------------|-------------------------------------------|--------------------------------------------------|-----|-------|------|

| STWIBOL                             | FARAMETER                                 | CONDITIONS                                       | нс  | нст   | ONIT |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay                         | $C_L = 15 \text{ pF};$                           |     |       |      |

|                                     | CP to Q <sub>n</sub>                      | $C_L = 15 \text{ pF};$<br>$V_{CC} = 5 \text{ V}$ | 17  | 20    | ns   |

|                                     | CP to TC                                  |                                                  | 21  | 25    | ns   |

|                                     | CET to TC                                 |                                                  | 11  | 14    | ns   |

| f <sub>max</sub>                    | maximum clock frequency                   |                                                  | 51  | 50    | MHz  |

| Cı                                  | input capacitance                         |                                                  | 3.5 | 3.5   | pF   |

| C <sub>PD</sub>                     | power dissipation capacitance per package | notes 1 and 2                                    | 33  | 35    | pF   |

#### **Notes**

C<sub>PD</sub> is used to determine the dynamic power dissipation (P<sub>D</sub> in µW):

$$P_{D} = C_{PD} \times V_{CC}^{2} \times f_{i} +$$

$$\sum (C_{L} \times V_{CC}^{2} \times f_{o})$$

where:

$\begin{array}{l} f_i & = \text{input frequency in MHz} \\ f_o & = \text{output frequency in MHz} \\ \sum \left( C_L \times V_{CC}^2 \times f_o \right) = \text{sum of} \\ \text{outputs} \end{array}$

$C_L$  = output load capacitance in pF

$V_{CC}$  = supply voltage in V

2. For HC the condition is  $V_1 = GND$  to  $V_{CC}$ For HCT the condition is  $V_1 = GND$  to  $V_{CC} - 1.5$  V

# 74HC/HCT163

### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

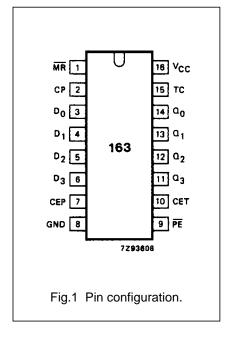

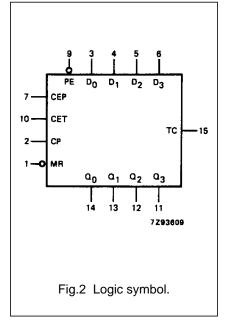

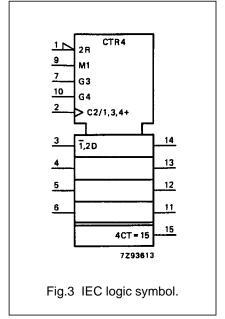

### **PIN DESCRIPTION**

| PIN NO.        | SYMBOL                           | NAME AND FUNCTION                         |

|----------------|----------------------------------|-------------------------------------------|

| 1              | MR                               | synchronous master reset (active LOW)     |

| 2              | CP                               | clock input (LOW-to-HIGH, edge-triggered) |

| 3, 4, 5, 6     | D <sub>0</sub> to D <sub>3</sub> | data inputs                               |

| 7              | CEP                              | count enable input                        |

| 8              | GND                              | ground (0 V)                              |

| 9              | PE                               | parallel enable input (active LOW)        |

| 10             | CET                              | count enable carry input                  |

| 14, 13, 12, 11 | Q <sub>0</sub> to Q <sub>3</sub> | flip-flop outputs                         |

| 15             | TC                               | terminal count output                     |

| 16             | V <sub>CC</sub>                  | positive supply voltage                   |

# Presettable synchronous 4-bit binary counter; synchronous reset

## 74HC/HCT163

#### **FUNCTION TABLE**

| OPERATING MODE    |        |        | OUTPUTS |        |        |                |                                  |          |

|-------------------|--------|--------|---------|--------|--------|----------------|----------------------------------|----------|

| OPERATING MODE    | MR     | СР     | CEP     | CET    | PE     | D <sub>n</sub> | Q <sub>n</sub>                   | TC       |

| reset (clear)     | I      | 1      | Х       | Х      | Х      | Х              | L                                | L        |

| parallel load     | h<br>h | ↑<br>↑ | X<br>X  | X<br>X | I<br>I | l<br>h         | L<br>H                           | L<br>(1) |

| count             | h      | 1      | h       | h      | h      | Х              | count                            | (1)      |

| hold (do nothing) | h<br>h | X<br>X | I<br>X  | X<br>I | h<br>h | X<br>X         | q <sub>n</sub><br>q <sub>n</sub> | (1)<br>L |

#### **Notes**

- 1. The TC output is HIGH when CET is HIGH and the counter is at terminal count (HHHHH).

- H = HIGH voltage level

- h = HIGH voltage level one set-up time prior to the LOW-to-HIGH CP transition

- L = LOW voltage level

- I = LOW voltage level one set-up time prior to the LOW-to-HIGH CP transition

- ${\bf q}$  = lower case letters indicate the state of the referenced output one set-up time prior to the LOW-to-HIGH CP transition

- X = don't care

- ↑ = LOW-to-HIGH CP transition

# Presettable synchronous 4-bit binary counter; synchronous reset

# 74HC/HCT163

# 74HC/HCT163

# Presettable synchronous 4-bit binary counter; synchronous reset

74HC/HCT163

### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                         | T <sub>amb</sub> (°C) |                 |                 |                 |                 |                 |                 |      | TEST CONDITIONS   |                    |  |

|-------------------------------------|---------------------------------------------------------|-----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------|-------------------|--------------------|--|

| SYMBOL                              | DADAMETED                                               | 74HC                  |                 |                 |                 |                 |                 |                 |      |                   | WAVEEODIA          |  |

|                                     | PARAMETER                                               | +25                   |                 |                 | -40 to +85   −4 |                 | -40 to +125     |                 | UNIT | V <sub>CC</sub>   | WAVEFORMS          |  |

|                                     |                                                         | min.                  | typ.            | max.            | min.            | max.            | min.            | max.            |      | (',               |                    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to Q <sub>n</sub>               |                       | 55<br>20<br>16  | 185<br>37<br>31 |                 | 230<br>46<br>39 |                 | 280<br>56<br>48 | ns   | 2.0<br>4.5<br>6.0 | Fig.8              |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to TC                           |                       | 69<br>25<br>20  | 215<br>43<br>37 |                 | 270<br>54<br>46 |                 | 320<br>65<br>55 | ns   | 2.0<br>4.5<br>6.0 | Fig.8              |  |

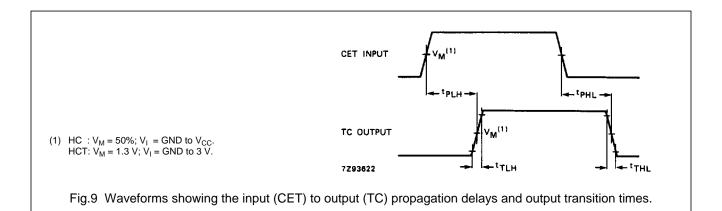

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CET to TC                          |                       | 36<br>13<br>10  | 120<br>24<br>20 |                 | 150<br>30<br>26 |                 | 180<br>36<br>31 | ns   | 2.0<br>4.5<br>6.0 | Fig.9              |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                  |                       | 19<br>7<br>6    | 75<br>15<br>13  |                 | 95<br>19<br>16  |                 | 110<br>22<br>19 | ns   | 2.0<br>4.5<br>6.0 | Figs 8 and 9       |  |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW                        | 80<br>16<br>14        | 17<br>6<br>5    |                 | 100<br>20<br>17 |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.8              |  |

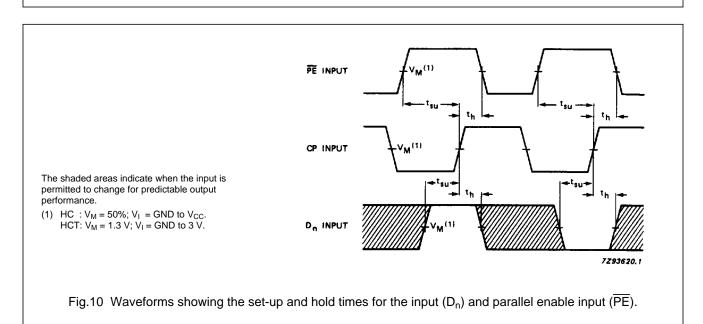

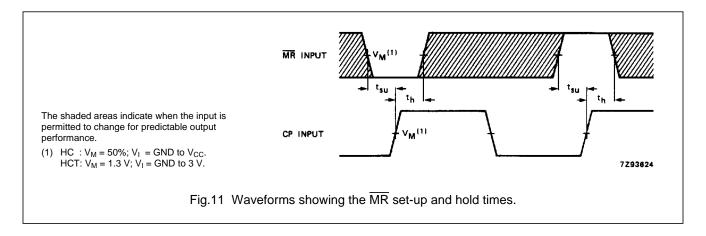

| t <sub>su</sub>                     | set-up time<br>MR, D <sub>n</sub> to CP                 | 80<br>16<br>14        | 17<br>6<br>5    |                 | 100<br>20<br>17 |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0 | Figs 10 and 11     |  |

| t <sub>su</sub>                     | set-up time<br>PE to CP                                 | 80<br>16<br>14        | 22<br>8<br>6    |                 | 100<br>20<br>17 |                 | 120<br>24<br>20 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.10             |  |

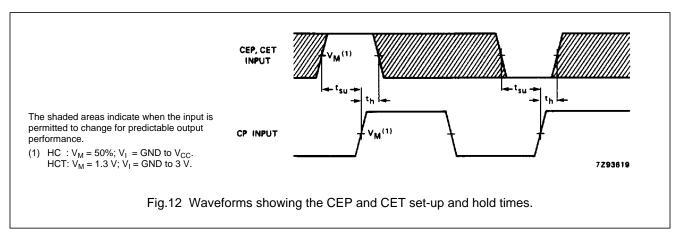

| t <sub>su</sub>                     | set-up time<br>CEP, CET to CP                           | 175<br>35<br>30       | 58<br>21<br>17  |                 | 220<br>44<br>37 |                 | 265<br>53<br>45 |                 | ns   | 2.0<br>4.5<br>6.0 | Fig.12             |  |

| t <sub>h</sub>                      | hold time<br>D <sub>n</sub> , PE, CEP,<br>CET, MR to CP | 0<br>0<br>0           | -14<br>-5<br>-4 |                 | 0<br>0<br>0     |                 | 0<br>0<br>0     |                 | ns   | 2.0<br>4.5<br>6.0 | Figs 10, 11 and 12 |  |

| f <sub>max</sub>                    | maximum clock pulse frequency                           | 5<br>27<br>32         | 15<br>46<br>55  |                 | 4<br>22<br>26   |                 | 4<br>18<br>21   |                 | MHz  | 2.0<br>4.5<br>6.0 | Fig.8              |  |

# Presettable synchronous 4-bit binary counter; synchronous reset

74HC/HCT163

### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

### Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| MR             | 0.95                  |

| СР             | 1.10                  |

| CEP            | 0.25                  |

| D <sub>n</sub> | 0.25                  |

| CET            | 0.75                  |

| PE             | 0.30                  |

# Presettable synchronous 4-bit binary counter; synchronous reset

# 74HC/HCT163

### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                         | T <sub>amb</sub> (°C) 74HCT |      |      |                  |      |        |             |      | TE                     | TEST CONDITIONS    |  |

|-------------------------------------|---------------------------------------------------------|-----------------------------|------|------|------------------|------|--------|-------------|------|------------------------|--------------------|--|

| SYMBOL                              | PARAMETER                                               |                             |      |      |                  |      |        |             | UNIT |                        | WAVEFORMS          |  |

|                                     |                                                         | +25                         |      |      | -40 to +85   -40 |      | -40 to | -40 to +125 |      | V <sub>CC</sub><br>(V) | WAVEFORMS          |  |

|                                     |                                                         | min.                        | typ. | max. | min.             | max. | min.   | max.        |      | (-,                    |                    |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to Q <sub>n</sub>               |                             | 23   | 39   |                  | 49   |        | 59          | ns   | 4.5                    | Fig.8              |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP to TC                           |                             | 29   | 49   |                  | 61   |        | 74          | ns   | 4.5                    | Fig.8              |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CET to TC                          |                             | 17   | 32   |                  | 44   |        | 48          | ns   | 4.5                    | Fig.9              |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                  |                             | 7    | 15   |                  | 19   |        | 22          | ns   | 4.5                    | Figs 8 and 9       |  |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW                        | 20                          | 6    |      | 25               |      | 30     |             | ns   | 4.5                    | Fig.8              |  |

| t <sub>su</sub>                     | set-up time MR, D <sub>n</sub> to CP                    | 20                          | 9    |      | 25               |      | 30     |             | ns   | 4.5                    | Figs 10 and 11     |  |

| t <sub>su</sub>                     | set-up time PE to CP                                    | 20                          | 11   |      | 25               |      | 30     |             | ns   | 4.5                    | Fig.10             |  |

| t <sub>su</sub>                     | set-up time<br>CEP, CET to CP                           | 40                          | 24   |      | 50               |      | 60     |             | ns   | 4.5                    | Fig.12             |  |

| t <sub>h</sub>                      | hold time<br>D <sub>n</sub> , PE, CEP,<br>CET, MR to CP | 0                           | -5   |      | 0                |      | 0      |             | ns   | 4.5                    | Figs 10, 11 and 12 |  |

| f <sub>max</sub>                    | maximum clock pulse frequency                           | 26                          | 45   |      | 21               |      | 17     |             | MHz  | 4.5                    | Fig.8              |  |

## 74HC/HCT163

#### **AC WAVEFORMS**

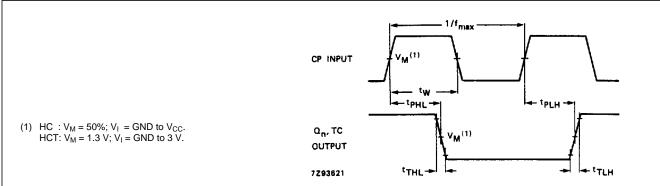

Fig.8 Waveforms showing the clock (CP) to outputs  $(Q_n, TC)$  propagation delays, the clock pulse width, the output transition times and the maximum clock frequency.

### 74HC/HCT163

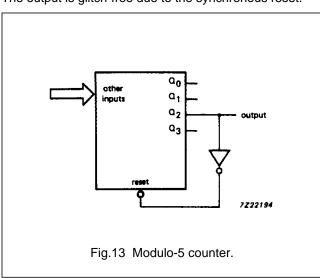

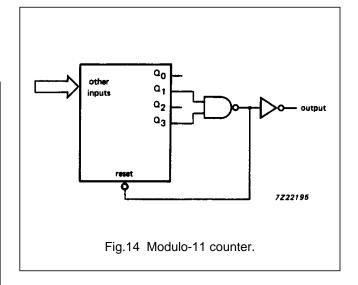

#### **APPLICATION INFORMATION**

The HC/HCT163 facilitate designing counters of any modulus with minimal external logic.

The output is glitch-free due to the synchronous reset.

#### **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".