# Geode™ CS9211 Graphics Companion Flat Panel Display Controller

# **General Description**

The National Semiconductor<sup>®</sup> Geode<sup>™</sup> CS9211 graphics companion is suitable for systems that use any GX-series processor (e.g., GX1, GXLV, GXm) along with the CS5530A I/O companion, also members of the Geode family of products.

The CS9211 converts the digital pixel stream output of the CS5530A to the digital RGB inputs used by standard single and dual-scan STN LCD display panels. Support is provided for both color and monochrome dual-scan STN (DSTN) flat panels up to 1024x768 resolution, and for color single-scan panels up to 640x480 resolution.

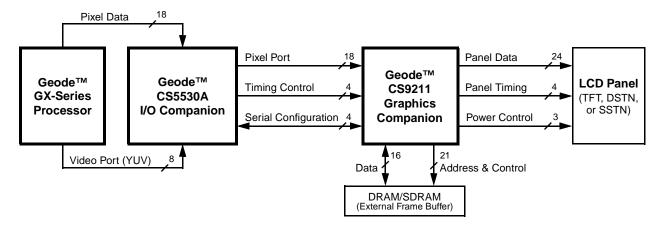

The typical system connection shows how to connect the CS9211 with other system components. Note that the external frame buffer is only required for DSTN panels.

#### **Features**

- Supports most SVGA DSTN panels and the VESA FPDI (Flat Panel Display Interface) Revision 1.0 Specification.

- Directly interfaces to panels; no external drivers needed (excluding backlight inverter).

- Supports 18-bit color pixel input data stream in 6:6:6 format, for a maximum display of 262,144 colors.

- Supports up to 65 MHz pixel clock (DOTCLK).

- Supports resolutions up to 1024x768 pixels.

- Fast display refresh rate, up to 120 Hz for DSTN panels, achieved by writing both panel halves simultaneously.

- 16- or 24-bit dual-scan color STN (DSTN) support.

- 8- or 16-bit dual-scan monochrome STN (DSTN) support.

- 8-bit single-scan color STN (SSTN) panel support.

- TFT panel support provided via pass-through mode.

- 9-, 12- or 18-bit TFT support.

- 9+9 or 12+12-bit, 2 pixels per clock TFT panel support.

- Frame rate modulation (FRM) allows up to 32 shades of gray (intensities) for each primary color (R,G,B) with no loss of spatial resolution.

- Proprietary dithering algorithm allows display of additional colors for a maximum of 262,144 colors.

- Programmable control of input and output sync pulse widths, delays, and polarities allows interfaces to many panel types.

- Programmable panel power sequence controls.

- Built-in memory controller supports either SDRAM or EDO memory for the DSTN frame buffer.

- Configuration via a serial programming interface.

- Low-power, 3.3V operation.

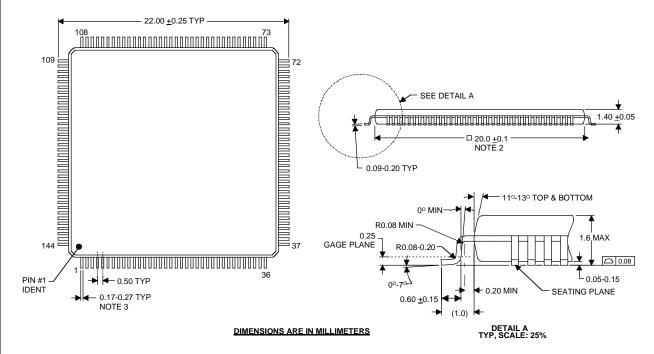

- 144-pin LQFP (Low-profile Quad Flat Pack).

# **Typical System Connection**

National Semiconductor is a registered trademark of National Semiconductor Corporation. Geode is a trademark of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

# **Table of Contents**

| 1.0 | Arch | nitectur            | e Overview 4                                                                                                     |  |  |  |  |  |

|-----|------|---------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2.0 | Sigr | nal Defii           | nitions                                                                                                          |  |  |  |  |  |

|     | 2.1  | 2.1 PIN ASSIGNMENTS |                                                                                                                  |  |  |  |  |  |

|     | 2.2  | SIGNA               | L DESCRIPTIONS9                                                                                                  |  |  |  |  |  |

|     |      | 2.2.1               | Pixel Port Interface Signals9                                                                                    |  |  |  |  |  |

|     |      | 2.2.2               | Serial Interface Signals10                                                                                       |  |  |  |  |  |

|     |      | 2.2.3               | Flat Panel Interface Signals10                                                                                   |  |  |  |  |  |

|     |      | 2.2.4               | Memory Interface Signals11                                                                                       |  |  |  |  |  |

|     |      | 2.2.5               | Reset, Crystal, and GPIO Pins                                                                                    |  |  |  |  |  |

|     |      | 2.2.6               | National Semiconductor Internal Test Pins13                                                                      |  |  |  |  |  |

|     |      | 2.2.7               | Power and Ground Pins                                                                                            |  |  |  |  |  |

| 3.0 | Fun  | ctional             | Description14                                                                                                    |  |  |  |  |  |

|     | 3.1  | SYSTE               | M INTERCONNECTIONS14                                                                                             |  |  |  |  |  |

|     |      | 3.1.1               | CS550A Connections                                                                                               |  |  |  |  |  |

|     |      | 3.1.2               | Panel Connections                                                                                                |  |  |  |  |  |

|     |      | 3.1.3               | Memory Connections                                                                                               |  |  |  |  |  |

|     |      | 3.1.4               | Crystal Oscillator Interface                                                                                     |  |  |  |  |  |

|     | 3.2  | FUNCT               | TIONAL BLOCKS                                                                                                    |  |  |  |  |  |

|     |      | 3.2.1               | Serial Interface                                                                                                 |  |  |  |  |  |

|     |      |                     | 3.2.1.1 Write Transfer Sequence (52 clocks)                                                                      |  |  |  |  |  |

|     |      |                     | 3.2.1.2 Read Transfer Sequence (56 clocks)                                                                       |  |  |  |  |  |

|     |      | 3.2.2               | Mode Selection                                                                                                   |  |  |  |  |  |

|     |      |                     | 3.2.2.1 TFT Mode                                                                                                 |  |  |  |  |  |

|     |      |                     | 3.2.2.2       STN Mode       19         3.2.2.3       Output Data Mapping       19                               |  |  |  |  |  |

|     |      | 3.2.3               | Timing Signals                                                                                                   |  |  |  |  |  |

|     |      | 0.2.0               | 3.2.3.1 Input Timing Signals                                                                                     |  |  |  |  |  |

|     |      |                     | 3.2.3.2 Output Timing Signals                                                                                    |  |  |  |  |  |

|     |      | 3.2.4               | Frame Rate Modulation26                                                                                          |  |  |  |  |  |

|     |      |                     | 3.2.4.1 Removal of Flickering                                                                                    |  |  |  |  |  |

|     |      | 3.2.5               | FRM Memory                                                                                                       |  |  |  |  |  |

|     |      | 3.2.6               | Dithering                                                                                                        |  |  |  |  |  |

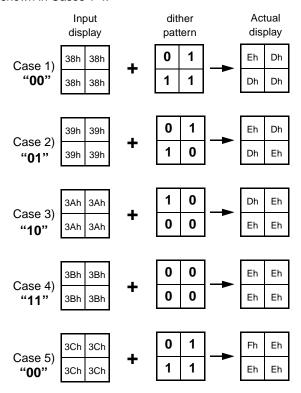

|     |      |                     | 3.2.6.1 Theory Of Dithering                                                                                      |  |  |  |  |  |

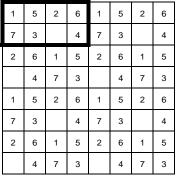

|     |      |                     | 3.2.6.2       Pre-Programmed Dither Patterns (ROM)       29         3.2.6.3       Controlling Dithering       30 |  |  |  |  |  |

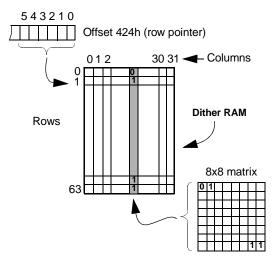

|     |      | 3.2.7               | User-defined Dither Patterns                                                                                     |  |  |  |  |  |

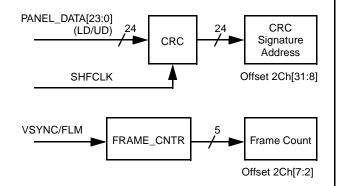

|     |      | 3.2.8               | CRC Signature                                                                                                    |  |  |  |  |  |

|     |      | 3.2.9               | Simultaneous Display                                                                                             |  |  |  |  |  |

|     |      | 3.2.10              | Maximum Frequency                                                                                                |  |  |  |  |  |

|     |      | 3.2.11              | Memory Controller                                                                                                |  |  |  |  |  |

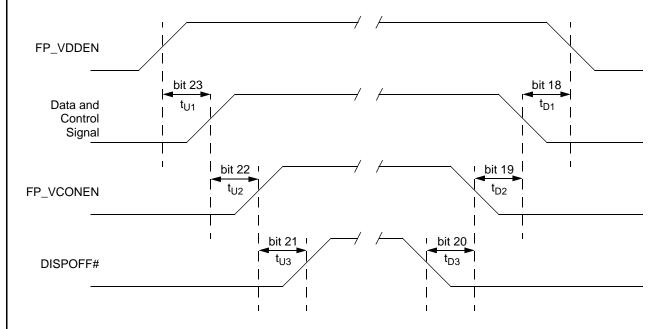

|     |      | 3.2.12              | Power Sequence Control                                                                                           |  |  |  |  |  |

|     |      | ~. <b>_</b>         | 3.2.12.1 External Power Sequencing                                                                               |  |  |  |  |  |

|     |      |                     | 3.2.12.2 Internal Power Sequencing                                                                               |  |  |  |  |  |

|     |      | 3.2.13              | General Purpose I/O Pins                                                                                         |  |  |  |  |  |

| 4.0 | Reg  | ister De            | escriptions40                                                                                                    |  |  |  |  |  |

| Table of Contents (Continued) |       |                                 |  |  |  |

|-------------------------------|-------|---------------------------------|--|--|--|

| 5.0                           | Elec  | ctrical Specifications          |  |  |  |

|                               | 5.1   | TEST MODES48                    |  |  |  |

|                               |       | 5.1.1 NAND Tree Mode            |  |  |  |

|                               | 5.2   | ABSOLUTE MAXIMUM RATINGS        |  |  |  |

|                               | 5.3   | OPERATING CONDITIONS            |  |  |  |

|                               | 5.4   | DC CHARACTERISTICS50            |  |  |  |

|                               | 5.5   | AC CHARACTERISTICS51            |  |  |  |

|                               |       | 5.5.1 Pixel Port Timing52       |  |  |  |

|                               |       | 5.5.2 Serial Interface Timing53 |  |  |  |

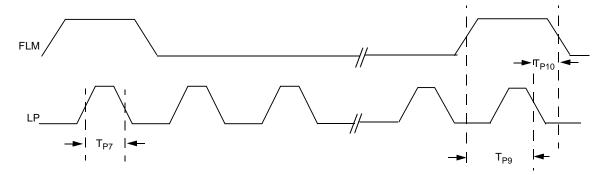

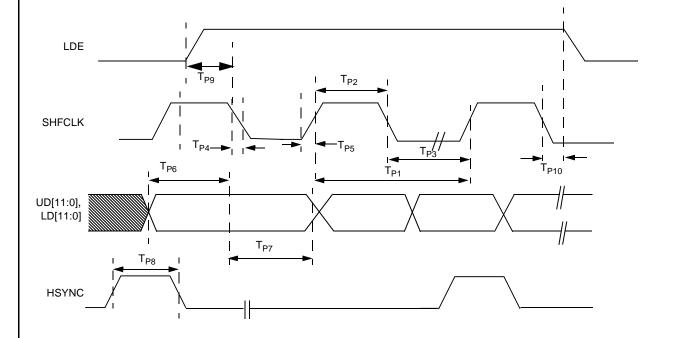

|                               |       | 5.5.3 Flat Panel Timing54       |  |  |  |

|                               |       | 5.5.4 Memory Interface Timing55 |  |  |  |

|                               |       | 5.5.5 Panel Timings             |  |  |  |

| 6.0                           | Mec   | chanical Package Outline        |  |  |  |

| App                           | endix | A Support Documentation         |  |  |  |

|                               | A.1   | REVISION HISTORY                |  |  |  |

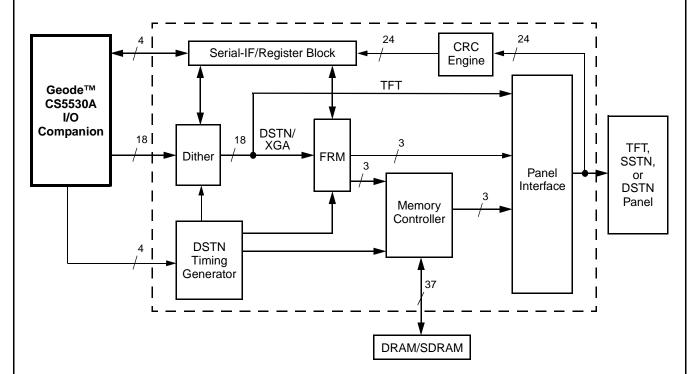

# 1.0 Architecture Overview

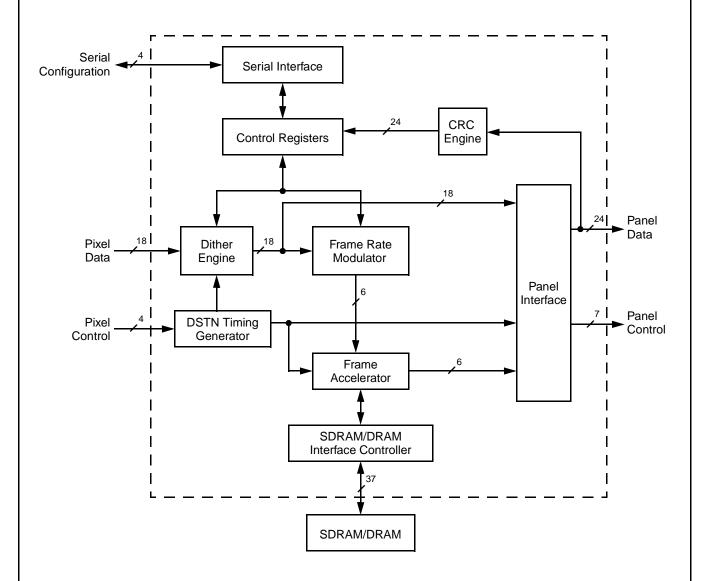

The major functional blocks, as shown in Figure 1-1, of the CS9211 graphics companion flat panel display controller:

- Serial Interface

- Dither Engine

- Frame Rate Modulator (FRM)

- · Control Registers

- DSTN Timing Generator

- Panel Interface

- Frame Accelerator

- CRC (Cyclical Redundancy Check) Engine

- SDRAM/DRAM Interface Controller

Figure 1-1. Internal Block Diagram

# 2.0 Signal Definitions

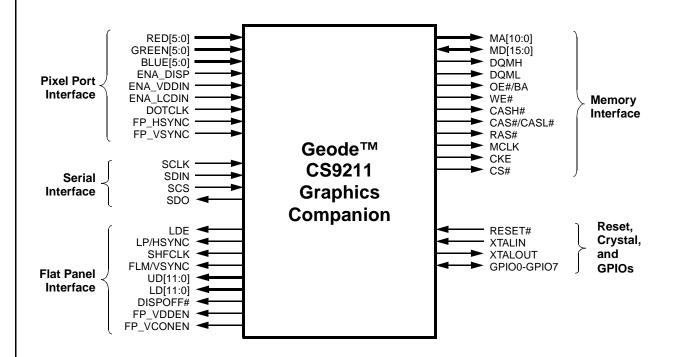

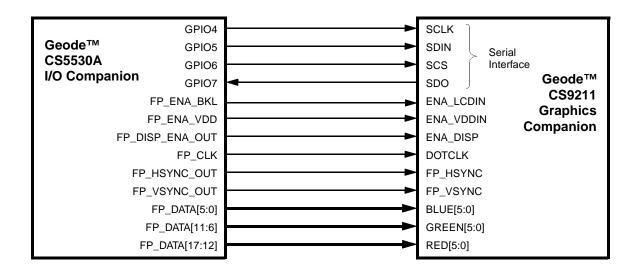

This section defines the signals and external interface of the CS9211. Figure 2-1 shows the pins organized by their functional groupings (internal test and electrical pins are not shown).

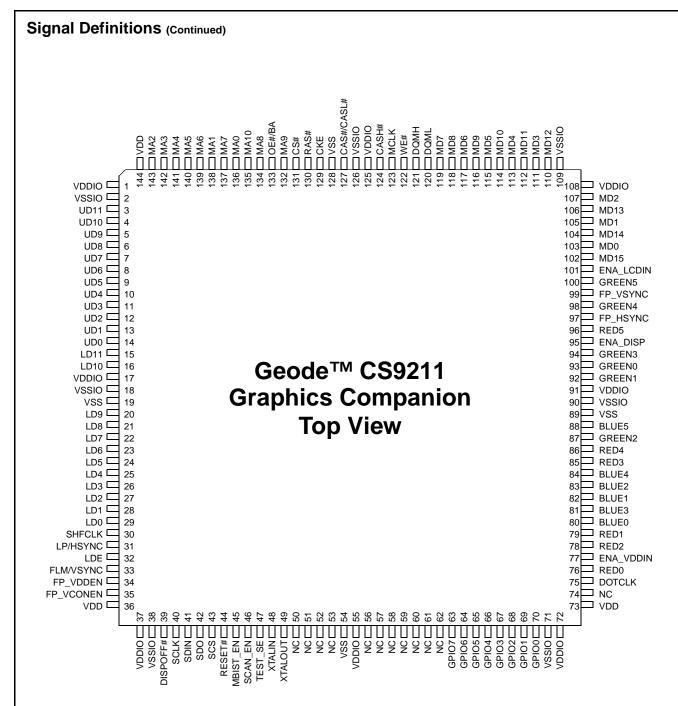

#### 2.1 PIN ASSIGNMENTS

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings.

Figure 2-2 shows the pin assignment for the CS9211 with Tables 2-2 and 2-3 listing the pin assignments sorted by pin number and alphabetically by signal name, respectively.

In Section 2.2 "Signal Descriptions" on page 9 a description of each signal within its associated functional group is provided.

**Table 2-1. Pin Type Definitions**

| Mnemonic  | Definition                                                                                                                                                                                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | Standard input pin                                                                                                                                                                                                                                |

| I/O       | Bidirectional pin                                                                                                                                                                                                                                 |

| 0         | Totem-pole output                                                                                                                                                                                                                                 |

| OD        | Open-drain output structure that allows multiple devices to share the pin in a wired-OR configuration                                                                                                                                             |

| PU        | Pull-up resistor                                                                                                                                                                                                                                  |

| PD        | Pull-down resistor                                                                                                                                                                                                                                |

| smt       | Schmitt Trigger                                                                                                                                                                                                                                   |

| t/s       | TRI-STATE signal                                                                                                                                                                                                                                  |

| VDD (PWR) | Power pin                                                                                                                                                                                                                                         |

| VSS (GND) | Ground pin                                                                                                                                                                                                                                        |

| #         | The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the a high voltage level. |

Figure 2-1. Signal Groups

Figure 2-2. 144-Pin LQFP Pin Assignment Diagram Order Number: CS9211-VNG

Table 2-2. Pin Assignments - Sorted by Pin Number

|            | Tabl        |          |               |  |

|------------|-------------|----------|---------------|--|

| Pin<br>No. | Signal Name | Туре     | Drive<br>(mA) |  |

| 1          | 1 VDDIO     |          |               |  |

| 2          | VSSIO       | GND      |               |  |

| 3          | UD11        | 0        | 8             |  |

| 4          | UD10        | 0        | 8             |  |

| 5          | UD9         | 0        | 8             |  |

| 6          | UD8         | 0        | 8             |  |

| 7          | UD7         | 0        | 8             |  |

| 8          | UD6         | 0        | 8             |  |

| 9          | UD5         | 0        | 8             |  |

| 10         | UD4         | 0        | 8             |  |

| 11         | UD3         | 0        | 8             |  |

| 12         | UD2         | 0        | 8             |  |

| 13         | UD1         | 0        | 8             |  |

| 14         | UD0         | 0        | 8             |  |

| 15         | LD11        | 0        | 8             |  |

| 16         | LD10        | 0        | 8             |  |

| 17         | VDDIO       | PWR      |               |  |

| 18         | VSSIO       | GND      |               |  |

| 19         | VSS         | GND      |               |  |

| 20         | LD9         | 0        | 8             |  |

| 21         | LD8         | 0        | 8             |  |

| -          | 22 LD7      |          | 8             |  |

| 23         | LD6         | 0        | 8             |  |

| 24         | LD5         | 0        | 8             |  |

| 25         | LD4         | 0        | 8             |  |

| 26         | LD3         | 0        | 8             |  |

| 27         | LD2         | 0        | 8             |  |

| 28         | LD1         | 0        | 8             |  |

| 29         | LD0         | 0        | 8             |  |

| 30         | SHFCLK      | 0        | 12            |  |

| 31         | LP/HSYNC    | 0        | 8             |  |

| 32         | LDE         | 0        | 8             |  |

| 33         | FLM/VSYNC   | 0        | 8             |  |

| 34         | FP_VDDEN    | 0        | 8             |  |

| 35         | FP_VCONEN   | 0        | 8             |  |

| 36         | VDD         | PWR      |               |  |

| 37         | VDDIO       | PWR      |               |  |

| 38         | VSSIO       | GND      |               |  |

| 39         | DISPOFF#    | 0        | 8             |  |

| 40         | SCLK        | ı        |               |  |

| 41         | SDIN        | ı        |               |  |

| 42         |             |          | 8             |  |

| 43         | SCS         | 0        |               |  |

| 43         | RESET#      | ı        |               |  |

| 45         | MBIST_EN    | <u>'</u> |               |  |

| 46         | SCAN_EN     | <u>'</u> |               |  |

| 46         | TEST_SE     | 1        |               |  |

|            | XTALIN      | <u>'</u> |               |  |

| 48         | AIALIN      | '        |               |  |

| Pin A      | ssignments - | Sorted | d by Pi       |

|------------|--------------|--------|---------------|

| Pin<br>No. | Signal Name  | Туре   | Drive<br>(mA) |

| 49         | XTALOUT      | 0      |               |

| 50         | NC           |        |               |

| 51         | NC           |        |               |

| 52         | NC           |        |               |

| 53         | NC           |        |               |

| 54         | VSS          | GND    |               |

| 55         | VDDIO        | PWR    |               |

| 56         | NC           |        |               |

| 57         | NC           |        |               |

| 58         | NC           |        |               |

| 59         | NC           |        |               |

| 60         | NC           |        |               |

| 61         | NC           |        |               |

| 62         | NC           |        |               |

| 63         | GPIO7        | I/O    | 4             |

| 64         | GPIO6        | I/O    | 4             |

| 65         | GPIO5        | I/O    | 4             |

| 66         | GPIO4        | I/O    | 4             |

| 67         | GPIO3        | I/O    | 4             |

|            | +            | 1/0    | 4             |

| 68         | GPIO2        |        |               |

| 69         | GPIO1        | 1/0    | 4             |

| 70         | GPIO0        | I/O    | 4             |

| 71         | VSSIO        | GND    |               |

| 72         | VDDIO        | PWR    |               |

| 73         | VDD          | PWR    |               |

| 74         | NC           |        |               |

| 75         | DOTCLK       | I      |               |

| 76         | RED0         | I      |               |

| 77         | ENA_VDDIN    | I      |               |

| 78         | RED2         | I      |               |

| 79         | RED1         | I      |               |

| 80         | BLUE0        | I      |               |

| 81         | BLUE3        | I      |               |

| 82         | BLUE1        | I      |               |

| 83         | BLUE2        | I      |               |

| 84         | BLUE4        | ı      |               |

| 85         | RED3         | I      |               |

| 86         | RED4         | ı      |               |

| 87         | GREEN2       | 1      |               |

| 88         | BLUE5        | 1      |               |

| 89         | VSS          | GND    |               |

| 90         | VSSIO        | GND    |               |

| 91         | VDDIO        | PWR    |               |

| 92         | GREEN1       | I      |               |

|            |              | 1      |               |

| 93         | GREENO       |        |               |

| 94         | GREEN3       |        |               |

| 95         | ENA_DISP     |        |               |

| 96         | RED5         | I      |               |

| Pin<br>No. | Signal Name | Туре | Drive<br>(mA) |

|------------|-------------|------|---------------|

| 97         | FP HSYNC    | ı    |               |

| 98         | GREEN4      | ı    |               |

| 99         | FP_VSYNC    | ı    |               |

| 100        | GREEN5      | ı    |               |

| 101        | ENA_LCDIN   | I    |               |

| 102        | MD15        | I/O  | 8             |

| 103        | MD0         | I/O  | 8             |

| 104        | MD14        | I/O  | 8             |

| 105        | MD1         | I/O  | 8             |

| 106        | MD13        | I/O  | 8             |

| 107        | MD2         | I/O  | 8             |

| 108        | VDDIO       | PWR  |               |

| 109        | VSSIO       | GND  |               |

| 110        | MD12        | I/O  | 8             |

| 111        | MD3         | I/O  | 8             |

| 112        | MD11        | I/O  | 8             |

| 113        | MD4         | I/O  | 8             |

| 114        | MD10        | I/O  | 8             |

| 115        | MD5         | I/O  | 8             |

| 116        | MD9         | I/O  | 8             |

| 117        | MD6         | I/O  | 8             |

| 118        | MD8         | I/O  | 8             |

| 119        | MD7         | I/O  | 8             |

| 120        | DQML        | 0    | 8             |

| 121        | DQMH        | 0    | 8             |

| 122        | WE#         | 0    | 8             |

| 123        | MCLK        | 0    | 12            |

| 124        | CASH#       | 0    | 8             |

| 125        | VDDIO       | PWR  |               |

| 126        | VSSIO       | GND  |               |

| 127        | CAS#/CASL#  | 0    | 8             |

| 128        | VSS         | GND  |               |

| 129        | CKE         | 0    | 8             |

| 130        | RAS#        | 0    | 8             |

| 131        | CS#         | 0    | 8             |

| 132        | MA9         | 0    | 8             |

| 133        | OE#/BA      | 0    | 8             |

| 134        | MA8         | 0    | 8             |

| 135        | MA10        | 0    | 8             |

| 136        | MA0         | 0    | 8             |

| 137        | MA7         | 0    | 8             |

| 138        | MA1         | 0    | 8             |

| 139        | MA6         | 0    | 8             |

| 140        | MA5         | 0    | 8             |

| 141        | MA4         | 0    | 8             |

| 142        | MA3<br>MA2  | 0    | 8             |

| 143        |             | PWR  | 8             |

| 144        | VDD         | FVVK |               |

Table 2-3. Pin Assignments - Sorted Alphabetically by Signal Name

| •           | 1    | able 2-       | 3. Pin     |

|-------------|------|---------------|------------|

| Signal Name | Туре | Drive<br>(mA) | Pin<br>No. |

| BLUE0       | -    |               | 80         |

| BLUE1       | I    |               | 82         |

| BLUE2       | I    |               | 83         |

| BLUE3       | I    |               | 81         |

| BLUE4       | I    |               | 84         |

| BLUE5       | I    |               | 88         |

| CAS#/CASL#  | 0    | 8             | 127        |

| CASH#       | 0    | 8             | 124        |

| CKE         | 0    | 8             | 129        |

| CS#         | 0    | 8             | 131        |

| DISPOFF#    | 0    | 8             | 39         |

| DOTCLK      | I    |               | 75         |

| DQMH        | 0    | 8             | 121        |

| DQML        | 0    | 8             | 120        |

| ENA_DISP    | I    |               | 95         |

| ENA_LCDIN   | ı    |               | 101        |

| ENA_VDDIN   | I    |               | 77         |

| FLM/VSYNC   | 0    | 8             | 33         |

| FP_HSYNC    | I    |               | 97         |

| FP_VCONEN   | 0    | 8             | 35         |

| FP_VDDEN    | 0    | 8             | 34         |

| FP_VSYNC    | I    |               | 99         |

| GPIO0       | I/O  | 4             | 70         |

| GPIO1       | I/O  | 4             | 69         |

| GPIO2       | I/O  | 4             | 68         |

| GPIO3       | I/O  | 4             | 67         |

| GPIO4       | I/O  | 4             | 66         |

| GPIO5       | I/O  | 4             | 65         |

| GPIO6       | I/O  | 4             | 64         |

| GPIO7       | I/O  | 4             | 63         |

| GREEN0      | I    |               | 93         |

| GREEN1      | I    |               | 92         |

| GREEN2      | I    |               | 87         |

| GREEN3      | I    |               | 94         |

| GREEN4      | I    |               | 98         |

| GREEN5      | I    |               | 100        |

| LD0         | 0    | 8             | 29         |

| LD1         | 0    | 8             | 28         |

| LD2         | 0    | 8             | 27         |

| LD3         | 0    | 8             | 26         |

| LD4         | 0    | 8             | 25         |

| LD5         | 0    | 8             | 24         |

| LD6         | 0    | 8             | 23         |

| LD7         | 0    | 8             | 22         |

| LD8         | 0    | 8             | 21         |

| LD9         | 0    | 8             | 20         |

| LD10        | 0    | 8             | 16         |

| LD11        | 0    | 8             | 15         |

| Signal Name | Туре | Drive<br>(mA) | Pin<br>No. |

|-------------|------|---------------|------------|

| RED3        | I    |               | 85         |

| RED4        | I    |               | 86         |

| RED5        | I    |               | 96         |

| RESET#      | I    |               | 44         |

| SCAN_EN     | I    |               | 46         |

| SCLK        | I    |               | 40         |

| SCS         | I    |               | 43         |

| SDIN        | I    |               | 41         |

| SDO         | 0    | 8             | 42         |

| SHFCLK      | 0    | 12            | 30         |

| TEST_SE     | I    |               | 47         |

| UD0         | 0    | 8             | 14         |

| UD1         | 0    | 8             | 13         |

| UD2         | 0    | 8             | 12         |

| UD3         | 0    | 8             | 11         |

| UD4         | 0    | 8             | 10         |

| UD5         | 0    | 8             | 9          |

| UD6         | 0    | 8             | 8          |

| UD7         | 0    | 8             | 7          |

| UD8         | 0    | 8             | 6          |

| UD9         | 0    | 8             | 5          |

| UD10        | 0    | 8             | 4          |

| UD11        | 0    | 8             | 3          |

| VDD         | PWR  |               | 36         |

| VDD         | PWR  |               | 73         |

| VDD         | PWR  |               | 144        |

| VDDIO       | PWR  |               | 1          |

| VDDIO       | PWR  |               | 17         |

| VDDIO       | PWR  |               | 37         |

| VDDIO       | PWR  |               | 55         |

| VDDIO       | PWR  |               | 72         |

| VDDIO       | PWR  |               | 91         |

| VDDIO       | PWR  |               | 108        |

| VDDIO       | PWR  |               | 125        |

| VSS         | GND  |               | 19         |

| VSS         | GND  |               | 54         |

| VSS         | GND  |               | 89         |

| VSS         | GND  |               | 128        |

| VSSIO       | GND  |               | 2          |

| VSSIO       | GND  |               | 18         |

| VSSIO       | GND  |               | 38         |

| VSSIO       | GND  |               | 71         |

| VSSIO       | GND  |               | 90         |

| VSSIO       | GND  |               | 109        |

| VSSIO       | GND  |               | 126        |

| WE#         | 0    | 8             | 122        |

| XTALIN      | ı    |               | 48         |

| XTALOUT     | 0    |               | 49         |

|             |      | <u> </u>      |            |

# 2.2 SIGNAL DESCRIPTIONS

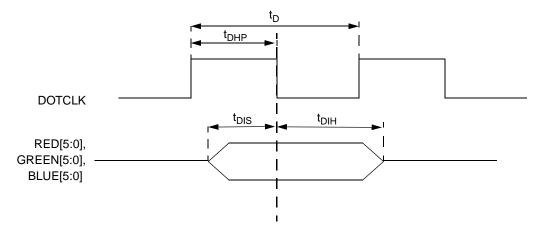

# 2.2.1 Pixel Port Interface Signals

| Signal Name                                          | Pin No.                                  | Type<br>(Drive)     | Description                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------|------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED[5:0]                                             | 96, 86,                                  | I                   | Red Pixel Channel                                                                                                                                                                                                                                                                                                  |

|                                                      | 85, 78,<br>79, 76                        |                     | These six pins are the red component of the pixel port input. The six most significant bits of the pixel port (FP_DATA[17:12] on an 18-bit pixel port) from the CS5530A are connected to these pins. RED5 is the MSB (most significant bit) and RED0 is the LSB (least significant bit).                           |

| GREEN[5:0]                                           | REEN[5:0] 100, 98, I Green Pixel Channel | Green Pixel Channel |                                                                                                                                                                                                                                                                                                                    |

| 92, 93 dle bits of the pixel CS5530A are conne       |                                          |                     | These six pins are the green component of the pixel port input. The six middle bits of the pixel port (FP_DATA[11:6] on an 18-bit pixel port) from the CS5530A are connected to these pins. GREEN5 is the MSB and GREEN0 is the LSB.                                                                               |

| BLUE[5:0]                                            | 88, 84,                                  | I                   | Blue Pixel Channel                                                                                                                                                                                                                                                                                                 |

|                                                      | 81, 83,<br>82, 80                        |                     | These six pins are the blue component of the pixel port input. The six least significant bits of the pixel port (FP_DATA[5:0] on an 18-bit pixel port) from the CS5530A are connected to these pins. BLUE5 is the MSB and BLUE0 is the LSB.                                                                        |

| ENA_DISP                                             | 95                                       | I                   | Active Display Enable                                                                                                                                                                                                                                                                                              |

|                                                      |                                          |                     | This input is asserted when the pixel data stream is presenting valid display data to the pixel port.                                                                                                                                                                                                              |

| ENA_VDDIN                                            | 77                                       | I                   | Input VDD Enable                                                                                                                                                                                                                                                                                                   |

|                                                      |                                          |                     | When this input is asserted high, it indicates that the CS9211 should apply voltage to the LCD panel. FP_VDDEN (pin 34) follows this assertion if external power sequencing is selected; it is ignored if internal power sequencing is selected.                                                                   |

| ENA_LCDIN                                            | 101                                      | I                   | Input LCD Enable                                                                                                                                                                                                                                                                                                   |

|                                                      |                                          |                     | When this input is asserted high, it indicates that the CS9211 should drive the contrast voltage to the LCD panel. FP_VCONEN (pin 35) follows this assertion if external power sequencing is selected; it is ignored if internal power sequencing is selected.                                                     |

| DOTCLK                                               | 75                                       | ı                   | DOT Clock                                                                                                                                                                                                                                                                                                          |

| clocks data in from the p is used as the input clock |                                          |                     | This signal is the pixel clock from the video controller within the CS550A. It clocks data in from the pixel port on the rising edge. Additionally, this signal is used as the input clock for the entire CS9211 device. This clock must be running at all times after reset for the CS9211 to function correctly. |

| FP_HSYNC                                             | 97                                       | I                   | Flat Panel Horizontal Sync Input                                                                                                                                                                                                                                                                                   |

|                                                      |                                          |                     | When the input data stream is in a horizontal blanking period, this input is asserted. It is a pulse used to synchronize display lines and to indicate when the pixel data stream is not valid due to blanking.                                                                                                    |

| FP_VSYNC                                             | 99                                       | I                   | Flat Panel Vertical Sync Input                                                                                                                                                                                                                                                                                     |

|                                                      |                                          |                     | When the input data stream is in a vertical blanking period, this input is asserted. It is a pulse used to synchronize display frames and to indicate when the pixel data stream is not valid due to blanking.                                                                                                     |

# 2.2.2 Serial Interface Signals

| Signal Name | Pin No. | Type<br>(Drive) | Description                                                                                                                                                                                             |

|-------------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK        | 40      | I               | Serial Interface Clock                                                                                                                                                                                  |

|             |         |                 | This input signal is the clock for the serial control interface. Data is clocked in and out on the rising edge. The other serial interface signals (SDIN, SCS, and SDO) are synchronous to this signal. |

| SDIN        | 41      | I               | Serial Data Input                                                                                                                                                                                       |

|             |         |                 | This is the data input line for the serial control interface. Input data is serialized on this pin, including the command stream for register reads and writes.                                         |

| ·           |         | _               | Serial Data Output                                                                                                                                                                                      |

|             |         | (8 mA)          | This is the data output line for the serial control interface. Output data is serialized on this pin in response to register read commands.                                                             |

| SCS         | 43      | I               | Serial Chip Select                                                                                                                                                                                      |

|             |         |                 | This active high chip select indicates when valid data is being clocked in or out via the SDIN/SDO pins.                                                                                                |

# 2.2.3 Flat Panel Interface Signals

| Signal Name | Pin No.          | Type<br>(Drive) | Function<br>Selection | Description                                                                                                                                                                                                |

|-------------|------------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHFCLK      | 30               | 0               |                       | Panel Clock (Shift Clock)                                                                                                                                                                                  |

|             |                  | (12<br>mA)      |                       | This is the shift clock or pixel clock for the flat panel data. This signal is used to clock pixel data into the LCD panel.                                                                                |

|             |                  |                 |                       | Depending on the type of panel being interfaced, this signal can also be referred to as CL2 or SHIFT.                                                                                                      |

| UD[11:0]    | 3:14             | 0               |                       | Upper and Lower Scan Data                                                                                                                                                                                  |

| LD[11:0]    | 15, 16,<br>20:29 | (8 mA)          |                       | These outputs are the panel pixel data bus to the LCD panel. The data format is dependent on the panel type selected. Refer to Section 3.2.2 "Mode Selection" on page 19.                                  |

| LDE         | 32               | 0               | Offset                | Flat Panel Display Enable (TFT Panels)                                                                                                                                                                     |

|             |                  | (8 mA)          | 404h[25] = 1          | LDE is the display enable for active-matrix TFT panels and is used to indicate the active pixel data on UD[11:0] and LD[11:0].                                                                             |

| LP          | 31               | 0               | Offset                | Latch Pulse (SSTN/DSTN Panels)                                                                                                                                                                             |

|             |                  | (8 mA)          | 404h[26] = 0          | Latch Pulse is the line pulse or latch pulse for the flat panel data, indicating that a display line is about to start.                                                                                    |

|             |                  |                 |                       | Depending on the type of panel being interfaced, this signal can also be referred to as CL1 or LINE.                                                                                                       |

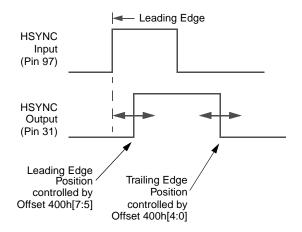

| HSYNC       |                  |                 | Offset                | Horizontal Sync (TFT Panels)                                                                                                                                                                               |

|             |                  |                 | 404h[26] = 1          | HSYNC is the horizontal sync for the active-matrix TFT panel. This is a delayed version of the input HSYNC signal with the appropriate pipeline delay relative to the pixel data on UD[11:0] and LD[11:0]. |

|             |                  |                 |                       | If pin 31 is set as HSYNC at Offset 404h[26], its polarity is programmable through Offset 404h[22]: 0 = Active high; 1 = Active low.                                                                       |

# 2.2.3 Flat Panel Interface Signals (Continued)

| Signal Name | Pin No. | Type<br>(Drive) | Function<br>Selection | Description                                                                                                                                                                                                               |  |

|-------------|---------|-----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FLM         | 33      | 0               | Offset                | First Line Marker (SSTN/DSTN Panels)                                                                                                                                                                                      |  |

|             |         | (8 mA)          | 404h[24] = 0          | This is the frame pulse for the flat panel data indicating a display frame is about to start.                                                                                                                             |  |

|             |         |                 |                       | Depending on the type of panel being interfaced, this signal can also be referred to as FP or FRAME.                                                                                                                      |  |

| VSYNC       |         |                 | Offset                | Vertical Sync (TFT Panels)                                                                                                                                                                                                |  |

|             |         |                 | 404h[24] = 1          | VSYNC is the vertical sync for active-matrix TFT panel. This is a delayed version of the input VSYNC signal with the appropriate pipeline delay relative to the pixel data on UD[11:0] and LD[11:0].                      |  |

|             |         |                 |                       | If pin 33 is selected as VSYNC at Offset 404h[24], its polarity is programmable through Offset 404h[23]: 0 = Active high; 1 = Active low.                                                                                 |  |

| DISPOFF#    | 39      | 0               |                       | Disables Backlight                                                                                                                                                                                                        |  |

|             |         | (8 mA)          |                       | When this output is asserted low, it turns the backlight off.                                                                                                                                                             |  |

| FP_VDDEN    | 34      | 0               |                       | Controls LCD VDD FET                                                                                                                                                                                                      |  |

|             |         | (8 mA)          |                       | When this output is asserted high, VDD voltage is applied to the panel. This signal is intended to control a power FET to the LCD panel. The FET may be internal to the panel or not, depending on the panel manufacturer |  |

| FP_VCONEN   | 35      | 0               |                       | Controls LCD Bias Voltage Enable                                                                                                                                                                                          |  |

|             |         | (8 mA)          |                       | When this output is asserted high, the contrast voltage is applied to the panel. This signal should be connected directly to the panel.                                                                                   |  |

# 2.2.4 Memory Interface Signals

| Signal Name | Pin No.                                                                                             | Type<br>(Drive) | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA[10:0]    | 135, 132,<br>134, 137,<br>139, 140,<br>141, 142,<br>143, 138,<br>136                                | O<br>(8 mA)     | Memory Address Bus  These signals are the address bits to the external frame buffer. Ten bits are used for EDO (Extended Data Out) DRAM and eleven bits are used for SDRAM.  Row and column addresses are multiplexed on the same pins. |

| MD[15:0]    | 102, 104,<br>106, 110,<br>112, 114,<br>116, 118,<br>119, 117,<br>115, 113,<br>111, 107,<br>105, 103 | I/O<br>(8 mA)   | Memory Data Bus  These bidirectional signals are the external frame buffer data bus.                                                                                                                                                    |

# 2.2.4 Memory Interface Signals (Continued)

| Signal Name | Pin No. | Type<br>(Drive) | Description                                                                                                                                                                                                                                                                                                         |  |

|-------------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DQMH        | 121     | 0               | Data Input/Output Mask                                                                                                                                                                                                                                                                                              |  |

| DQML        | 120     | (8 mA)<br>O     | DQMx is an input mask signal to the frame buffer SDRAM for write accesses and an output enable signal for read accesses.                                                                                                                                                                                            |  |

|             |         | (8 mA)          | Input data to the SDRAM is masked when DQMx is sampled high during a write cycle.                                                                                                                                                                                                                                   |  |

|             |         |                 | The output buffers are placed in a High-Z state (two-clock latency) when DQMx is sampled high during a read cycle.                                                                                                                                                                                                  |  |

|             |         |                 | DQMH corresponds to DQ8-DQ15 of the SDRAM. DQML corresponds to DQ0-DQ7 of the SDRAM. This signal is not used for EDO DRAM.                                                                                                                                                                                          |  |

|             |         |                 |                                                                                                                                                                                                                                                                                                                     |  |

| OE#/BA      | 133     | 0               | Output Enable and Bank Select Address                                                                                                                                                                                                                                                                               |  |

|             |         | (8 mA)          | This pin is the output enable for the DRAM and the bank address selection for SDRAM.                                                                                                                                                                                                                                |  |

|             |         |                 | BA defines to which bank the active, read, write or precharge command is being applied. This function is not used in the CS9211.                                                                                                                                                                                    |  |

| RAS#        | 130     | 0               | Row Address Strobe                                                                                                                                                                                                                                                                                                  |  |

|             |         | (8 mA)          | The row address strobe for DRAM/SDRAM.                                                                                                                                                                                                                                                                              |  |

| CASH#       | 124     | 0               | Column Address Strobe                                                                                                                                                                                                                                                                                               |  |

|             |         | (8 mA)          | The column address strobe for the upper byte of EDO DRAM. This pin should not be connected if SDRAM is used.                                                                                                                                                                                                        |  |

| CAS#/CASL#  | 127     | 0               | Column Address Strobe                                                                                                                                                                                                                                                                                               |  |

|             |         | (8 mA)          | The column address strobe for the lower byte of DRAM. This pin should be connected (to CAS#) if SDRAM is used.                                                                                                                                                                                                      |  |

| WE#         | 122     | 0               | Write Enable                                                                                                                                                                                                                                                                                                        |  |

|             |         | (8 mA)          | The write enable output for DRAM/SDRAM.                                                                                                                                                                                                                                                                             |  |

| MCLK        | 123     | 0               | Memory Clock                                                                                                                                                                                                                                                                                                        |  |

|             |         | (12<br>mA)      | This clock output from the CS9211 should be connected to the SDRAM. It is not used for EDO DRAM.                                                                                                                                                                                                                    |  |

| CKE         | 129     | 0               | Clock Enable                                                                                                                                                                                                                                                                                                        |  |

|             |         | (8 mA)          | This output signal should be connected to the SDRAM. When CKE is active (high), the MCLK signal is low. Deactivating the clock provides precharge power-down and self-refresh operations (all banks idle), active power-down (row active CKE in either bank) or clock Suspend operation (burst/access in progress). |  |

|             |         |                 | CKE is synchronous to MCLK, except after the device enters power-down and self refresh modes, where CKE becomes asynchronous until after exiting the same mode. The input buffers, including MCLK, are disabled during power-down and self refresh modes, and provide low power. CKE may be tied high.              |  |

|             |         |                 | This signal is not used for EDO DRAM.                                                                                                                                                                                                                                                                               |  |

| CS#         | 131     | 0               | Chip Select                                                                                                                                                                                                                                                                                                         |  |

|             |         | (8 mA)          | This output is connected to the chip select of SDRAM. CS# enables (registered low) and disables (registered high) the command decoder of the SDRAM. All commands are masked when CS# is deasserted (high).                                                                                                          |  |

### 2.2.5 Reset, Crystal, and GPIO Pins

| Signal Name | Pin No. | Type<br>(Drive) | Description                                                                                                                                                             |

|-------------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET#      | 44      | I               | System Reset Input                                                                                                                                                      |

|             |         |                 | A system reset should be at least as long as one clock cycle of the slowest of DOTCLK, XTALIN or SCLK. RESET# should be active for at least 1 ms.                       |

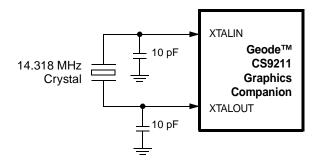

| XTALIN      | 48      | I               | Crystal Oscillator Connection                                                                                                                                           |

|             |         |                 | This pin is the crystal input for the on-chip reference oscillator or a CMOS clock input from an external reference source. It should be 14.318 MHz.                    |

| XTALOUT     | 49      | 0               | Crystal Oscillator Connection                                                                                                                                           |

|             |         |                 | This pin is the crystal output for the on-chip reference oscillator. If an external clock is used, leave this pin unconnected.                                          |

| GPIO0-GPIO7 | 70:63   | I/O             | General Purpose Inputs/Outputs                                                                                                                                          |

|             |         | (4 mA)          | Each GPIO pin can be configured independently as an input or output. For further programming information refer to Section 3.2.13 "General Purpose I/O Pins" on page 38. |

# 2.2.6 National Semiconductor Internal Test Pins

| Signal Name | Pin No. | Type<br>(Drive) | Description                                                                                                       |

|-------------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------|

| TEST_SE     | 47      | I               | Reserved                                                                                                          |

|             |         |                 | This pin must be tied to ground for normal operation. It is a National Semiconductor internal test mode pin only. |

| MBIST_EN    | 45      | I               | Reserved                                                                                                          |

|             |         |                 | This pin must be tied to ground for normal operation. It is a National Semiconductor internal test mode pin only. |

| SCAN_EN     | 46      | I               | Reserved                                                                                                          |

|             |         |                 | This pin must be tied to ground for normal operation. It is a National Semiconductor internal test mode pin only. |

### 2.2.7 Power and Ground Pins

| Signal Name | Pin No.                                  | Type<br>(Drive) | Description                                                                                                                   |

|-------------|------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| VDDIO       | 1, 17, 37,<br>55, 72,<br>91, 108,<br>125 | PWR             | Power Connection (total of 8 pins)  Power for the DRAM and system interface signals. These pins should be supplied with 3.3V. |

| VSSIO       | 2, 18, 38,<br>71, 90,<br>109, 126        | GND             | Ground Connection (total of 7 pins) Ground connection.                                                                        |

| VDD         | 36, 73,<br>144                           | PWR             | Power Connection (total of 3 pins)  Power for the DRAM and system interface signals. These pins should be supplied with 3.3V. |

| VSS         | 19, 54,<br>89, 128                       | GND             | Ground Connection (total of 4 pins) Ground connection.                                                                        |

# 3.0 Functional Description

This chapter discusses the detailed operations of the CS9211 in two categories: system-level and the operations/programming of the major functional blocks.

#### 3.1 SYSTEM INTERCONNECTIONS

The system-level discussion topics revolve around events that affect the device as a whole unit and how the CS9211 connects/interfaces with other system devices (i.e., CS5530A, panel, memory, and crystal oscillator).

#### 3.1.1 CS550A Connections

The CS9211 graphics companion connects to the TFT graphics data port of the CS550A I/O companion chip, as shown in Figure 3-1. In order for this interface to function, the CS550A must be in the "Limited ISA Mode", not the "ISA Master Mode", as discussed in the CS550A data book

Register programming and internal memory loading commands are delivered to the CS9211 by means of a GPIO interface. The GPIOs can come from any device capable of controlling those signals, as described in Section 3.2.1 "Serial Interface" on page 17. For example, National's Superl/O (PC97317) also produces compatible GPIO signals.

The CS9211 reformats the incoming pixel data stream and produces an output data stream that is directly compatible with the attached LCD panel.

Timing and power sequence control signals are delivered to the CS9211 from the CS550A. Various "pass-through" or "internal/external" selection modes of the CS9211 allow those external signals to be used or modified internally, before being passed on to the panel, or ignored completely, in which case they would be generated internally.

The CS9211 receives a pixel data stream from the CS550A. The chief function of the CS9211 is to reformat this received input stream into an output stream suitable for display on the LCD panels it supports.

Figure 3-1. CS550A and CS9211 Signal Connections

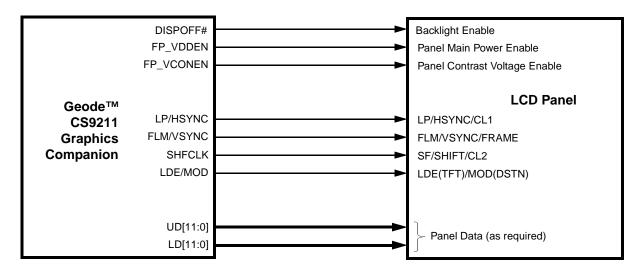

#### 3.1.2 Panel Connections

As illustrated in Figure 3-3, the connections between the CS9211 and the LCD panel being driven are simple. There are three groups of interconnect: Power Control, Timing, and Data. Because of the wide variety of LCD panels currently used in the industry, this interface is discussed briefly and generically.

Power control signals enable the panel's backlight, main power, and contrast voltage. In some cases, these signals may be directly connected to the panel being used; in other cases, external circuitry such as a power FET, may be required. Consult the data sheet of the panel being used in the design for details.

Timing signals are connected directly to the panel. Different panel manufacturers use various nomenclatures to identify the timing signals, some of which are shown (separated by the "/" character) in Figure 3-3.

The output of the CS9211 is a 24-bit data bus that is artificially split into two 12-bit data buses by the CS9211's adopted nomenclature (UD/LD). The output data presented on these buses "moves" from pin to pin depending on the type of panel being used, as determined by the contents of several of the CS9211's internal registers. These output buses should be thought of as one 24-bit bus for ease of the designer's understanding and to avoid confusion with panels which have a UD/LD-type data bus nomenclature.

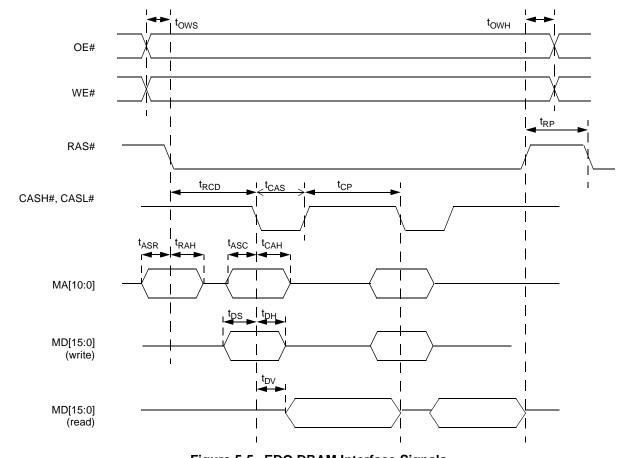

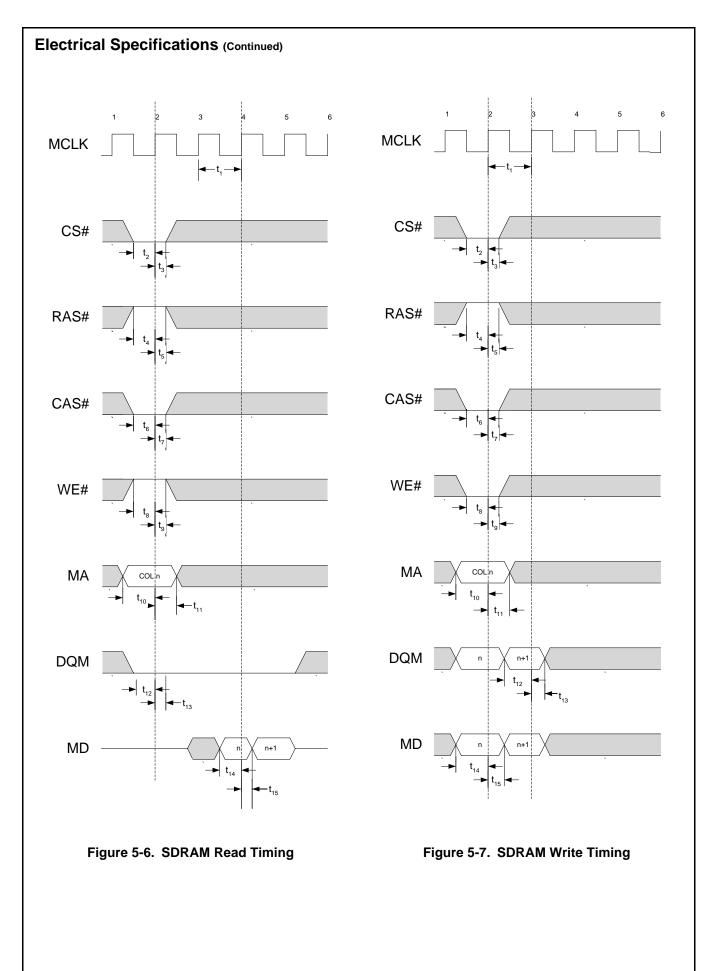

#### 3.1.3 Memory Connections

The interface between the CS9211 and the frame buffer memory (if used) is straightforward. Signal names used in the CS9211 match up with those used by the standard EDO DRAM and SDRAM devices. Note that the frame buffer memory is only required for DSTN panels. If the memory is not required, the memory interface signals from the CS9211 may remain unconnected.

If a DSTN panel is used, the CS9211 must be connected to an external frame buffer RAM, which may be either EDO DRAM or SDRAM. The external frame buffer is not required if an SSTN panel is used. Pixel data is received by the pixel port, formatted by a dither block and programmable FRM, and stored in the CS9211 frame buffer. The formatted pixel data is subsequently read from the frame buffer and used to refresh half the DSTN panel, while the other half receives "live" data from the CS550A.

#### 3.1.4 Crystal Oscillator Interface

The CS9211 requires a 14.318 MHz input clock to generate power sequencing signals to the panel. The input frequency should be 14.318 MHz. The clock may come from a compatible clock source anywhere in the design, or from a dedicated crystal oscillator tank circuit. The recommended oscillator tank circuit is shown in Figure 3-2.

Figure 3-2. Oscillator Tank Circuit

Figure 3-3. CS9211 and Flat Panel Signal Connections

#### 3.2 FUNCTIONAL BLOCKS

The block diagram of the CS9211, along with the basic system interconnections are shown in Figure 3-4. Details of each block will be discussed in this section.

The CS9211 interfaces directly to industry standard 8-, 16and 24-bit color or monochrome single or dual-scan STN flat panels (not all combinations are supported). It can also support 18-bit active matrix thin-film-transistor (TFT) with one or two pixels per clock.

The digital RGB or video data that is supplied by the CS5530A is converted into a suitable format to drive the supported panels. The heart of the device is the Frame Rate Modulator (FRM), which provides the ability to display various intensities of each primary color. Dithering logic is included to further increase the apparent number of colors that can be displayed. To support the DSTN panels, a memory controller that interfaces to external EDO DRAM or SDRAM (used as a frame buffer) is built into the

CS9211. A configurable timing generator provides timing pulses tailored to the panel being driven. The CS9211 supports automatic power sequence of panel power supplies. The device contains a CRC generator which may be used for self-validation during silicon validation.

Each pixel on an SSTN or DSTN LCD panel consists of three primary color components: red, green, and blue. Each primary color component, for a given pixel, can be turned on or off; there are no intermediate intensities. A total of eight colors can be generated for a given pixel through various combinations of turning each color component on or off. In order to generate more colors, frame rate modulation and dithering are used. The CS9211 is capable of generating 256K different colors, based on the 18-bit RGB pixel inputs.

Figure 3-4. CS9211 Block Diagram

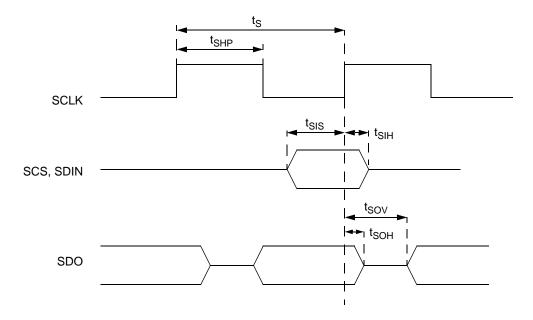

#### 3.2.1 Serial Interface

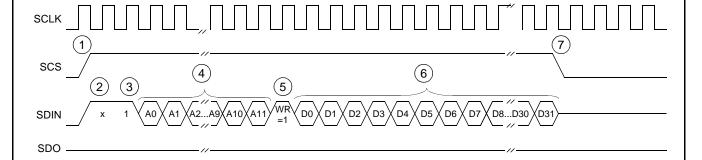

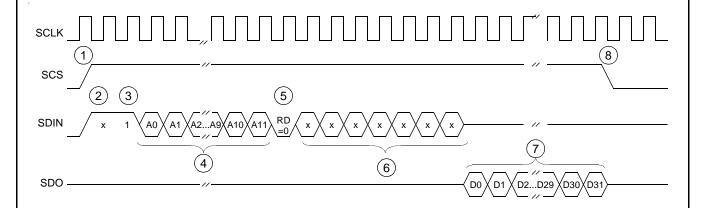

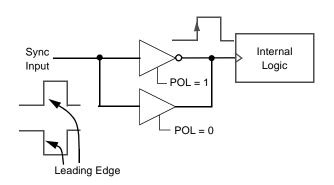

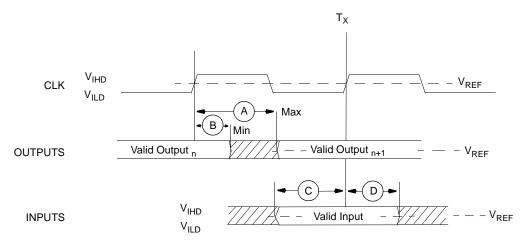

Two commands are defined for the serial interface, a read command and a write command. The read and write protocols are summarized in Table 3-1. Figure 3-5 on page 18 shows the write cycle timing, and Figure 3-6 on page 18 shows the read cycle timing. In order for the CS9211 to properly receive commands through the serial interface, the DOTCLK input signal must be active.

The protocol begins with the assertion of the SCS input, followed by activity on the SCLK (serial command clock) and SDIN (serial data input) lines. The serial data must be in the following order: one start bit (value = X), one control bit (value = 1), 12 address bits, a read/write command bit (1 = Write, 0 = Read), and 32 data bits. In the case of a read, seven (7) idle clock pulses must occur between the read command and the beginning of the 32 bits of data transmission on the SDO line. After the last bit of the serial data transfer, SCS should be deasserted.

The CS9211 samples the serial interface input signals on the rising edge of SCLK. Therefore, data driven onto the SDIN input should change on the falling edge of SCLK. Data driven by the CS9211 onto the SDO output changes on the rising edge of SCLK. Therefore data being read should be sampled on the falling edge of SCLK.

#### 3.2.1.1 Write Transfer Sequence (52 clocks)

- 1) Assert SCS input.

- One SCLK period "don't care" transfer (i.e., clock toggle).

- 3) Write a 1 to SDIN.

- Next, the address is transmitted with the LSB (Address[0]) first... MSB (Address[11]) last.

- 5) The Write bit = 1.

- The data is transmitted LSB (Data[0]) first... MSB (Data[31]) last, on the positive edges of the next 32 SCLKS.

- Deassert SCS (one clock period) and toggle SCLK for four clock periods.

### 3.2.1.2 Read Transfer Sequence (56 clocks)

- 1) Assert SCS input.

- One SCLK period "don't care" transfer (i.e., clock toggle).

- 3) Write a 1 to SDIN.

- Next the address is transmitted with the LSB (Address[0]) first ... MSB (Address[11]) last.

- 5) The Read bit = 0.

- Seven SCLK periods of "don't care" transfer (i.e., clock toggles).

- The data is transmitted on SDO with the LSB (Data[0]) first ... MSB (Data[31]) last, on the positive edges of the next 32 SCLK.

- Deassert SCS (one clock period) and toggle SCLK for one clock period.

Table 3-1. Serial Interface Write/Read Sequences

| Cycle(s) | Write Sequence with SCS = "1"      |                   | Cycle(s) | Read Seque        | nce with SCS = "1"    |

|----------|------------------------------------|-------------------|----------|-------------------|-----------------------|

| 1        | 1 Start bit                        | SDIN = Don't care | 1        | 1 Start bit       | SDIN = Don't care     |

| 1        | 1 Control bit                      | SDIN = 1          | 1        | 1 Control bit     | SDIN = 1              |

| 12       | 12 Address bits                    | SDIN = 4xx        | 12       | 12 Address bits   | SDIN = 4xx            |

| 1        | 1 Write bit                        | SDIN = 1          | 1        | 1 Read bit        | SDIN = 0              |

| 32       | 32 data bits ex: SDIN = A8A8_A8A8h |                   | 7        | 7 Idle SCLKs      | ex: SDIN = Don't care |

|          |                                    |                   | 32       | 32 Read data bits | ex: SDO = A8A8_A8A8h  |

Figure 3-5. Serial Interface Write Cycle Timing Diagram

Figure 3-6. Serial Interface Read Cycle Timing Diagram

#### 3.2.2 Mode Selection

The CS9211 can be configured for various modes depending on the type of LCD panel being connected. The panel type and mode selection is through Offset 404h[21:16] as shown in Table 3-2 on page 20 and described below.

- DSTN or TFT and Color or Monochrome:

- DSTN or TFT: Allows a common connector to be used for TFT LCD panels and DSTN LCD panels. The system software can configure the CS9211 to operate in a pass-through mode that presents the digital pixel (RGB) input data on the UD/LD output pins to drive a TFT panel on the common connector. The input data is latched internally before being presented at the output pins to better control the timing of the panel interface signals.

- Color or Monochrome: Monochrome must be selected for 8-bit DSTN Mode.

- 8-Bit DSTN Mode (Monochrome Only):

- Supports DSTN panels with 640x480 pixel resolution.

- Register programming: Offset 404h[21:16] = 00\_1\_000.

- 8-Bit single scan Color STN Mode:

- Supports single scan STN panels with 640x480 color pixel resolution.

- Register programming: Offset 404h[21:16] = 00\_0\_011.

- 16-Bit Color DSTN Mode:

- Supports DSTN panels with 640x480 or 800x600 color pixel resolutions.

- Register programming: Offset 404h[21:16] = 00\_0\_001.

- 24-Bit Color DSTN Mode:

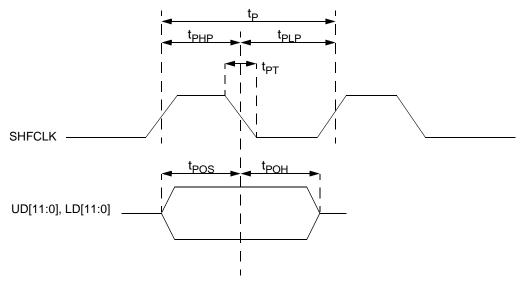

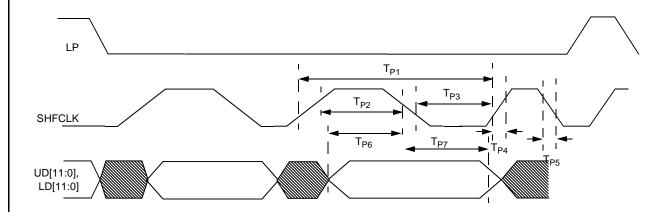

- Supports DSTN panels with 1024x768 color pixel resolution.