T.52-13-90

# **OKI** semiconductor

(Underdevelopment)

40-BIT GRID DRIVER

**MSC7701**

### **GENERAL DESCRIPTION**

The MSC7701 is a monolithic IC using the high withstand voltage driver process for hybridizing CMOS and DMOS transistors on one chip.

The logic portion such as the input stage, shift register and latch is formed by CMOS, and the output driver requiring a high withstand voltage is formed by DMOS transistors.

Since the pin assignment allows single side pattern formation on the printed circuit board, the display unit size can be reduced.

The bidirectional shift register facilitates the pattern design when the devices are arranged symmetrically with the display at the center axis.

### **FEATURES**

- Logic supply voltage (V<sub>CC</sub>) : + 5 V

- VF driver supply voltage (V<sub>hv</sub>) : + 130 V ;

- VF driver output current

(lohvh) : - 40 mA (1 driver output high)

(l<sub>ohyl</sub>) : +2 mA

- Clock frequency : 5.5 MHz

- Built-in 40-Bit latch

- Built-in 40-Bit bidirectional shift register

- 60 Pin FLAT Package

72

T-52-13-90

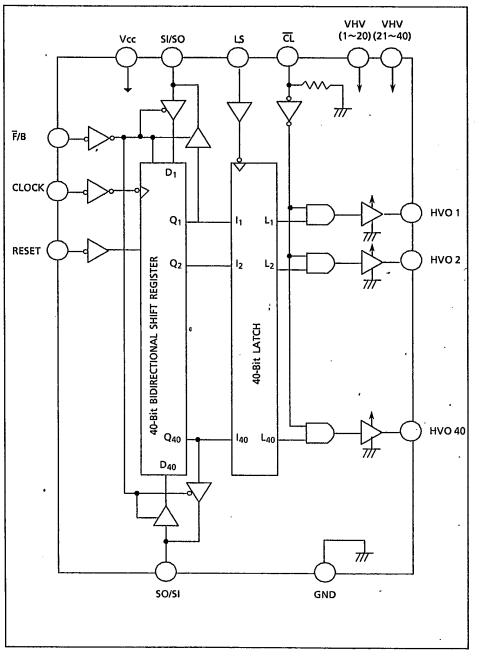

# **BLOCK DIAGRAM**

73

This Material Copyrighted By Its Respective Manufacturer

Downloaded from Datasheet.su

T-52-13-90

•

### PIN CONFDIGURATION

74

🗰 6724240 0006423 o 🔳

PIN DESCRIPTION

T-52-13-90

| Pin No.             | Symbol          | Name                             | Description                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>20<br>41<br>50 | HVO 1<br>HVO 40 | Driver output                    | <ol> <li>Each terminal is a high withstand voltage driver<br/>output terminal to drive the grid of the VF<br/>display tube, which corresponds to each bit of<br/>the shift register.</li> <li>Each terminal can be directly connected to the<br/>grid terminal of the VF display tube.</li> </ol>                                                                    |

| 22<br>39            | V <sub>HV</sub> | Driver supply<br>voltage         | 1. This is a power terminal of the high withstand<br>voltage driver to drive the VF display tuve.                                                                                                                                                                                                                                                                    |

| 28                  | Vcc             | Logic supply<br>voltage          | 2. This is a power terminal of the logic portion.                                                                                                                                                                                                                                                                                                                    |

| 36                  | ĊĹ              | Clear input                      | <ol> <li>This is an input terminal containing a pull-down<br/>resistor.</li> <li>The terminal is generally kept High. The driver<br/>output, High or Low, is driven by the output of<br/>the corresponding latch circuit.</li> <li>When the terminal is Low, the driver outputs<br/>are fixed to "Low" regardless of the output of<br/>the latch circuit.</li> </ol> |

| 26                  | LS              | Latch strobe input               | <ol> <li>When the terminal is High, the latch circuit is<br/>slewed, and the output of the shift register is<br/>read into the latch circuit.</li> <li>When the terminal is Low, the latch circuit holds<br/>the output of the shift register immediately<br/>before the terminal is turned Low.</li> </ol>                                                          |

| 34                  | CLOCK           | Clock input                      | <ol> <li>This is a clock terminal of the shift register. The<br/>data of the shift register is shifted at the falling<br/>edge of a clock pulse.</li> </ol>                                                                                                                                                                                                          |

| 32                  | RESET           | Reset input                      | <ol> <li>When the terminal is Low; all the data of the<br/>shift register is Low. Generally and when not in<br/>use, connect the terminal to the V<sub>CC</sub> terminal.</li> </ol>                                                                                                                                                                                 |

| 38                  | F/B             | Shift direction<br>control input | <ol> <li>When the terminal is Low, data is shifted from<br/>to 40, and Pin 31 is a serial in terminal and Pin 30<br/>is a serial out terminal.</li> <li>When the terminal is High, data is shifted from<br/>40 to 1, and Pin 30 is a serial in terminal and Pin<br/>31 is a serial out terminal.</li> </ol>                                                          |

| 31                  | SI/SO           | Serial input/serial<br>output    | <ol> <li>When the F/B terminal is Low, this terminal is<br/>serial data input terminal.</li> <li>When the F/B terminal is High, this terminal is<br/>serial data output terminal.</li> </ol>                                                                                                                                                                         |

| 30                  | SO/SI           | Serial output/serial<br>input    | <ol> <li>When the F/B terminal is Low, this terminal is<br/>serial data output terminal.</li> <li>When the F/B terminal is High, this terminal is<br/>serial data input terminal.</li> </ol>                                                                                                                                                                         |

| 24                  | GND             | GND                              | 1. This is a grounding (GND) terminal.                                                                                                                                                                                                                                                                                                                               |

75

This Material Copyrighted By Its Respective Manufacturer

Downloaded from Datasheet.su

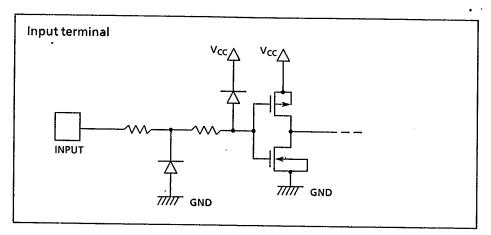

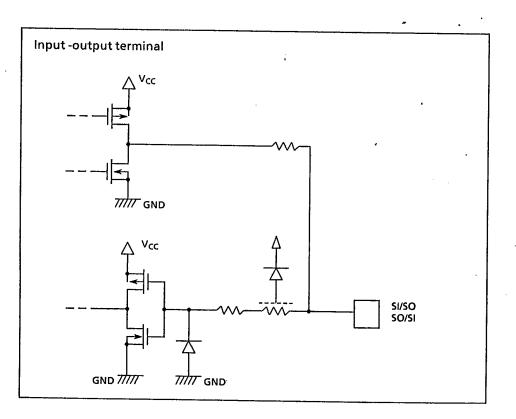

T-52-13-90 SCHEMATIC DIAGRAMS OF LOGIC PORTION INPUT AND OUTPUT TERMINAL CIRCUITS

76

#### O K I SEMICONDUCTOR GROUP 23E D ■ 6724240 0006425 4 **mm**

T-52-13-90

. .

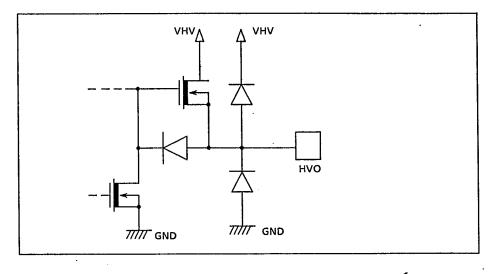

SCHEMATIC DIAGRAM OF DRIVER OUTPUT TERMINAL CIRCUIT

# **FUNCTION TABLE**

ł

| RESET | CLK         | Ŧ/в | SI/SO           | Q1              | Q2              | Q3              | <br>Q39          | Q40              | SO/SI             |

|-------|-------------|-----|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------------------|

| L     | Х           | L   | х               | L               | L               | L               | L                | Ľ                | L                 |

| L     | х           | н   | L               | L               | L               | L               | L                | L                | x                 |

| Η.    | <b>_</b> ₹  | L   | н               | н               | Q <sub>1n</sub> | Q <sub>2n</sub> | Q <sub>38n</sub> | Q <sub>39n</sub> | Q <sub>39rr</sub> |

| Н     | لم<br>م     | L   | ۰L              | L               | Q <sub>1n</sub> | Q <sub>2n</sub> | Q <sub>38n</sub> | Q <sub>39n</sub> | Q <sub>39n</sub>  |

| н     | ~~          | Н   | Q <sub>2n</sub> | Q <sub>2n</sub> | Q <sub>3n</sub> | Q <sub>4n</sub> | Q <sub>40n</sub> | н                | н                 |

| н     | _ <b>√_</b> | н   | Q <sub>2n</sub> | Q <sub>2n</sub> | Q <sub>3n</sub> | Q <sub>4n</sub> | Q <sub>40n</sub> | L                | L                 |

| ĊĹ | LS | Qn | HVOn |

|----|----|----|------|

| L  | х  | х  | L    |

| н  | н  | н  | н    |

| н  | н  | L  | L    |

| н  | L  | x  | NC   |

L: Low Level, H: High Level X: Don't Care, NC: No Change

77

- 6 -

-----.

📰 6724240 0006426 6 📰

T-52-13-90

# **ELECTRICAL CHARACTERISTICS**

| • | Absolute | Maximum Ra | tings |

|---|----------|------------|-------|

|   |          |            |       |

| Parameter             | Symbol                                                                                 | Conditios                             | Limits                      | Unit | Note |

|-----------------------|----------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|------|------|

| Logic supply voltage  | V <sub>CC</sub>                                                                        | Applicable to logic power terminal    | - 0.3~6.5                   | v    | 1    |

| Driver supply voltage | voltage V <sub>HV</sub> Applicable to V <sub>CC</sub> ~150<br>driver power<br>terminal |                                       | v                           | 1    |      |

| Input voltage         | VIN                                                                                    | Applicable to all input teminals      | -0.3~V <sub>CC</sub> +0.3   | V    | 1    |

| Data ouptput voltage  | Vod                                                                                    | Applicable to data<br>output terminal | -0.3~V <sub>CC</sub> +0.3   | v    | 1    |

| Driver output voltage | Vohv                                                                                   | Applicable to all driver terminals    | - 0.3~V <sub>CC</sub> + 0.3 | v    | 1    |

| Power Dissipation     | Pd                                                                                     | Ta≦25°C                               | 860                         | mW   |      |

| Attenuation Rate      | Rj-a                                                                                   | Ta>25°C                               | 145                         | °C/W | 2    |

| Operating temperature | Тор                                                                                    | VHV≦ 130V                             | - 40~ + 85                  | °C   |      |

| Storage temperature   | Tstg                                                                                   |                                       | - 55~ + 150                 | °C   |      |

Notes: 1. The maximum voltage which can be applied to the GND terminal.

2. Thermal resistance of the package (between junction and atmosphere).

The junction temperature (Tj) expressed by the equation indicated below should not exceed 150°C.

$Tj = P \times Rj - a + Ta (P: Maximum power consumption of IC)$

78

. .

🔳 6724240 0006427 8 🔳

T-52-13-90

• • • •

# Recommended Operating Conditions

| Parameter                           | Symbol             | Conditions                                           |                        | MIN  | ΜΑΧ      | Unit |  |

|-------------------------------------|--------------------|------------------------------------------------------|------------------------|------|----------|------|--|

| Logic supply voltage                | V <sub>cc</sub>    | Applicable to logic power<br>terminal                |                        | 4.5  | 5.5      | v    |  |

| Driver supply voltage               | V <sub>HV</sub>    | Applicable to logic<br>terminal                      | power                  | 10   | 130      | v    |  |

| High level input voltage            | VIH                | Applicable to all                                    | V <sub>CC</sub> = 4.5V | 3.6  | -        | v    |  |

|                                     |                    | V <sub>CC</sub> = 5.5V                               | 4.4                    | -    | •        |      |  |

| Low level input voltage             | VIL                | Applicable to all                                    | V <sub>CC</sub> = 4.5V | -    | 0.9      | v    |  |

| Low level input voltage             | νïL                | input terminals                                      | V <sub>CC</sub> = 5.5V |      | 1.1      | v    |  |

| Driver high level output<br>current | I <sub>ОНVН</sub>  | 1 driver output : High<br>Other driver outputs : Low |                        | -    | - 40     | mA   |  |

| Driver low level output<br>current  | <sup>I</sup> OHVL  | Applicable to all dri<br>terminals                   | -                      | 2    | mA       |      |  |

| Clock frequency                     | fØ                 | See timing chart.                                    |                        | -    | 5.5      | MHz  |  |

| Clock pulse width                   | t <sub>wciki</sub> | See timing chart.                                    |                        | 70   | -        | nS   |  |

| Data setup time                     | t <sub>ds</sub>    | See timing chart.                                    |                        | 20   |          | nS   |  |

| Data hold time                      | t <sub>dh</sub>    | See timing chart.                                    |                        | 45   | -        | nS · |  |

| LS pulse width                      | t <sub>wis</sub>   | See timing chart.                                    |                        | 80   |          | nS   |  |

| CLK-LS delay time                   | t <sub>dcl</sub>   | See timing chart.                                    |                        | 45   | <b>—</b> | nS   |  |

| LS-CL delay time                    | t <sub>dlcl</sub>  | See timing chart.                                    |                        | 0    | <u> </u> | , nS |  |

| CL pulse width                      | t <sub>wcl</sub>   | See timing chart.                                    |                        | 2    | -        | μS   |  |

| Operating temperature               | Тор                | See timing chart.                                    |                        | - 40 | + 85     | °C   |  |

79

This Material Copyrighted By Its Respective Manufacturer

STATE IN TAXABLE

Through a back of the

### • DC Characteristics

# T-52-13-90

$V_{CC} = 5V \pm 10\%$ ,  $V_{HV} = 110V$ ,  $Ta = -40^{\circ}C \sim +85^{\circ}C$

| Parameter                          | Symbol                                                  |                           | Conditions                                                                |      |     | MAX  | Unit |

|------------------------------------|---------------------------------------------------------|---------------------------|---------------------------------------------------------------------------|------|-----|------|------|

| Logic supply current               | Icc1                                                    | No load                   | All inputs : Low                                                          |      |     | 50   |      |

|                                    | I <sub>CC2</sub>                                        | V <sub>CC</sub> ≈ 5.5V    | All inputs : High<br>1 driver output : High<br>Other driver outputs : Low | _    | _   | 200  | μA   |

| Driver supply                      | lhv1                                                    | No load                   | All driver outputs : Low                                                  | -    |     | 50   | μA   |

| current                            | I <sub>HV2</sub>                                        | V <sub>cc</sub> ≈ 5.5V    | 1 driver output : High                                                    |      | 1.1 | 1.5  | mA   |

| High level input                   | VIH                                                     | V <sub>cc</sub> = 4.5V    | Applicable to all input                                                   | 3.15 | -   |      | v    |

| voltage                            |                                                         | V <sub>cc</sub> = 5.5V    | terminals                                                                 | 3.85 | _   |      | v    |

| Low level input                    | Low level input $V_{IL} = \frac{V_{cc} = 4.5V}{V_{IL}}$ |                           | Applicable to all input                                                   |      |     | 1.35 | v    |

| voltage                            |                                                         | V <sub>cc</sub> = 5.5V    | terminals                                                                 |      | -   | 1.65 | v    |

| Input leak current                 | I <sub>ILEEK</sub>                                      | Ta = 25℃                  | Input terminals except CL<br>terminal                                     | -    | _   | ± 1  | μА   |

| High level input                   | Чн                                                      | V <sub>cc</sub> = 4.5V    | Applicable to CL terminal                                                 | 20   | 50  | 100  | μА   |

| current                            |                                                         | V <sub>cc</sub> = 5.5V    |                                                                           | 25   | 60  | 200  |      |

| Input capacitance                  | CIN                                                     | Ta = 25°C                 | 1                                                                         | _    | 15  | _    | рF   |

| High level data                    | VODH                                                    | lo = −0.1mA               | V <sub>cc</sub> ≈ 4.5V                                                    | 3.5  | 1   | —    |      |

| output voltage                     |                                                         |                           | V <sub>CC</sub> = 5.5V                                                    | 4.5  | -   | ·    | v    |

| Low level data                     | VODL                                                    | lo = −0.1mA               | V <sub>cc</sub> = 4.5V                                                    | -    |     | 0.9  |      |

| output voltage                     |                                                         |                           | V <sub>CC</sub> = 5.5V                                                    | ·    | —   | 1.1  | v    |

| High level driver<br>output voltae | V <sub>онvн</sub>                                       | I <sub>OHV</sub> = - 40mA |                                                                           | 106  | -   | -    | v    |

| Low level driver<br>output voltae  | V <sub>OHVL</sub>                                       | I <sub>OHV</sub> = 2mA    |                                                                           | _    | _   | 4    | v    |

80

experiment of a new statement of the statement

This Material Copyrighted By Its Respective Manufacturer

T-52-13-90

### **AC Characteristics**

| $V_{CC} = 5V_{c}$ | $V_{HV} = 200V_{c}$ | Ta = 25°C |

|-------------------|---------------------|-----------|

| Parameter                           | Symbol           | Conditios                           | MIN | ТҮР | MAX | Unit | Note |

|-------------------------------------|------------------|-------------------------------------|-----|-----|-----|------|------|

| CLK-DOUT delay time t <sub>pd</sub> |                  | See timing chart<br>and test chart. | -   | 100 | 150 | nS   | 4    |

| Delay time : L→H                    | t <sub>dlh</sub> | See timing chart<br>and test chart. | -   | 0.3 | 1   | μs   | 5,6  |

| Transit time : L→H                  | t <sub>tih</sub> | See timing chart<br>and test chart. | —   | 2   | 5   | μs   | 5    |

| Delay time : H→L                    | t <sub>dhi</sub> | See timing chart<br>and test chart. | -   | 0.3 | 1   | μs   | 5,6  |

| Transit time : H→L                  | t <sub>thi</sub> | See Timing chart<br>and test chart. | -   | 3   | 6   | μs   | 5    |

Note 4 : Note 5 : Note 6 :

Applicable to data output terminal. Applicable to driver output termin<u>al.</u> t<sub>dlh</sub> and T<sub>dhl</sub> are delay times from CL signal.

#### **Timing Chart**

This Material Copyrighted By Its Respective Manufacturer

:

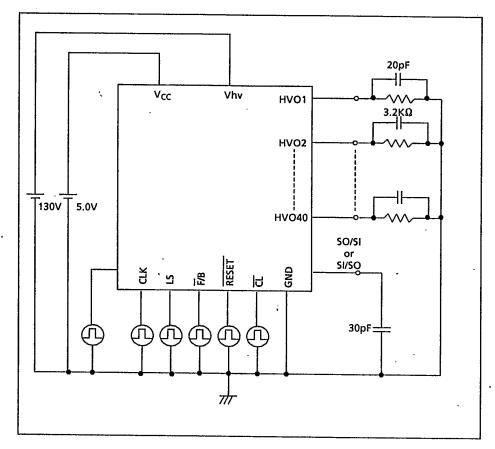

## **TEST CIRCUIT**

T-52-13-90

Information furnished by OKI is believed to be accurate and reliable. However, no responsibility is assumed by OKI for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of OKI.

82

-----

2