### Freescale Semiconductor

Data Sheet: Advanced Information

Document Number: IMX50CEC Rev. 0, 7/2011

# i.MX50 Applications Processors for Consumer Products

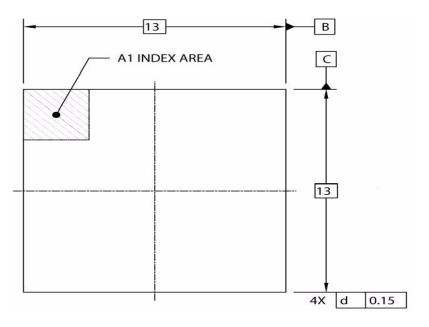

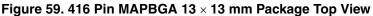

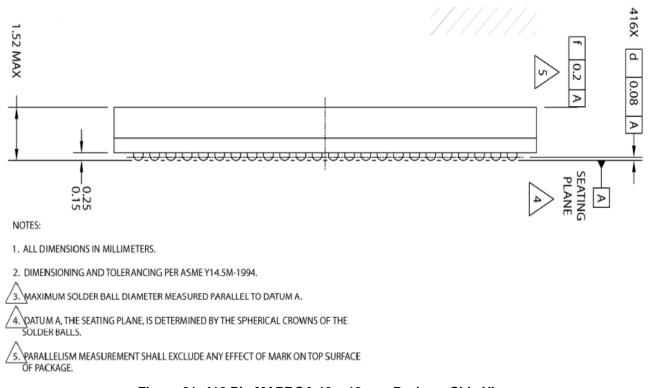

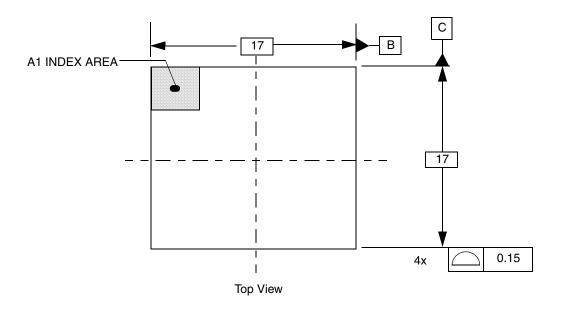

Package Information Plastic Package Case MAPBGA 13 x 13 mm, 0.5 mm pitch 416 pin PBGA

#### **Ordering Information**

See Table 1 on page 7 for ordering information.

# 1 Introduction

The i.MX50 Applications Processors (i.MX50) represent Freescale Semiconductor's latest addition to a growing family of multimedia-focused products, offering high performance processing optimized for lowest power consumption.

The i.MX50 is optimized for portable multimedia applications and features Freescale's advanced implementation of the ARM Cortex-A8<sup>TM</sup> core, which operates at speed as high as 800 MHz. The i.MX50 provides a powerful display architecture, including a 2D Graphics Processing Unit (GPU) and Pixel Processing Pipeline (ePXP). In addition, i.MX508 includes a complete integration of the electrophoretic display function. The i.MX50 supports DDR2, LPDDR2, and LPDDR1 DRAM at clock rate up to 266 MHz to enable a range of performance and power trade-offs.

The flexibility of the i.MX50 architecture allows it to be used in a variety of applications. As the heart of the application chipset, the i.MX50 provides a rich set of interfaces for connecting peripherals, such as WLAN, Bluetooth<sup>TM</sup>, GPS, and displays.

| 1. | Intro                  | duction                                               |  |  |  |  |

|----|------------------------|-------------------------------------------------------|--|--|--|--|

|    | 1.1.                   | Product Overview                                      |  |  |  |  |

|    | 1.2.                   | Features                                              |  |  |  |  |

|    | 1.3.                   | Ordering Information7                                 |  |  |  |  |

|    | 1.4.                   | Part Number Feature Comparison7                       |  |  |  |  |

|    | 1.5.                   | Package Feature Comparison                            |  |  |  |  |

| 2. | Architectural Overview |                                                       |  |  |  |  |

|    | 2.1.                   | Block Diagram9                                        |  |  |  |  |

| 3. | Modules List           |                                                       |  |  |  |  |

|    | 3.1.                   | Special Signal Considerations 16                      |  |  |  |  |

| 4. | Elect                  | rical Characteristics 19                              |  |  |  |  |

|    | 4.1.                   | Chip-Level Conditions 19                              |  |  |  |  |

|    | 4.2.                   | Supply Power-Up/Power-Down Requirements and           |  |  |  |  |

|    |                        | Restrictions                                          |  |  |  |  |

|    | 4.3.                   | I/O DC Parameters 26                                  |  |  |  |  |

|    | 4.4.                   | Output Buffer Impedance Characteristics 34            |  |  |  |  |

|    | 4.5.                   | I/O AC Parameters                                     |  |  |  |  |

|    | 4.6.                   | System Modules Timing 45                              |  |  |  |  |

|    | 4.7.                   | External Interface Module (EIM) 57                    |  |  |  |  |

|    | 4.8.                   | DRAM Timing Parameters                                |  |  |  |  |

|    | 4.9.                   | External Peripheral Interfaces                        |  |  |  |  |

| 5. | Pack                   | age Information and Contact Assignments 98            |  |  |  |  |

|    | 5.1.                   | 416 MAPBGA $13 \times 13$ mm Package Information . 98 |  |  |  |  |

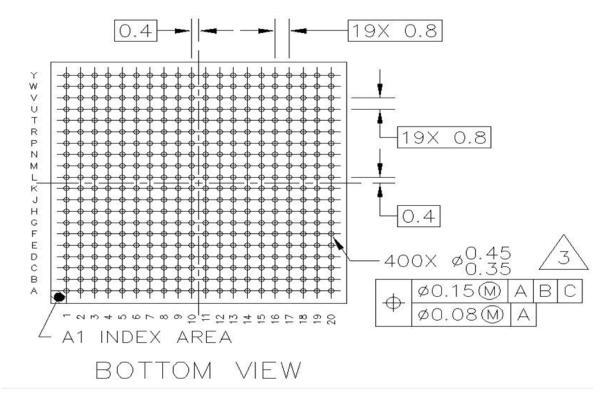

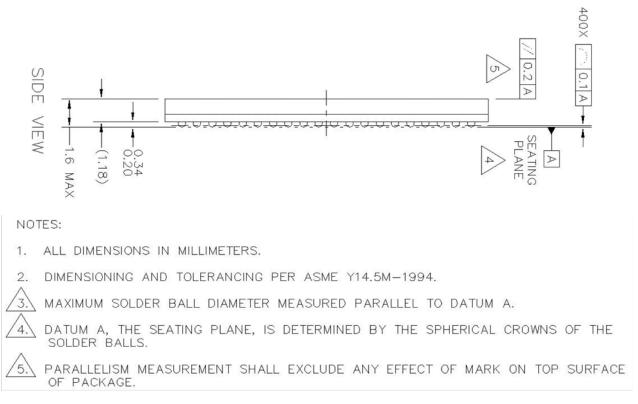

|    | 5.2.                   | 400 MAPBGA 17x 17 mm 0.8 mm Pitch Package             |  |  |  |  |

|    |                        | Information 103                                       |  |  |  |  |

|    | 5.3.                   | Signal Assignments 109                                |  |  |  |  |

| 6. | Revision History       |                                                       |  |  |  |  |

© Freescale Semiconductor, Inc., 2011. All rights reserved.

## 1.1 **Product Overview**

The i.MX50 is designed to enable high-tier portable applications by satisfying the performance requirements of advanced operating systems and applications.

# 1.1.1 Dynamic Performance Scaling

Freescale's dynamic voltage and frequency scaling (DVFS) allows the device to run at much lower voltage and frequency with ample processing capacity for tasks, such as audio decode, resulting in significant power reduction.

### 1.1.2 Multimedia Processing Powerhouse

The multimedia performance of the i.MX50 processor ARM Cortex-A8 core is boosted by a multi-level cache system, a NEON co-processor with SIMD media processing architecture and 32-bit single-precision floating point support, and two vector floating point co-processors. The system is further enhanced by a programmable smart DMA (SDMA) controller.

### 1.1.3 Powerful Display System

The i.MX50 includes support for both standard LCD displays as well as electrophoretic displays (e-paper). The display subsystem consists of the following modules:

• Electrophoretic Display Controller (EPDC) (i.MX508 only)

The EPDC is a feature-rich, low power, and high-performance direct-drive active matrix EPD controller. It is specifically designed to drive E-INK<sup>TM</sup> EPD panels, supporting a wide variety of TFT architectures. The goal of the EPDC is to provide an efficient SoC integration of this functionality for e-paper applications, allowing a significant bill of materials cost savings over an external solution while reaching much higher levels of performance and lower power. The EPDC module is defined in the context of an optimized hardware/software partitioning and works in conjunction with the ePXP (see Section 1.1.4, "Graphics Accelerators").

• Enhanced LCD Controller Interface (eLCDIF)

The eLCDIF is a high-performance LCD controller interface that supports a rich set of modes and allows interoperability with a wide variety of LCD panels, including DOTCK/RGB and smart panels. The module also supports synchronous operation with the ePXP to allow the processed frames to be passed from the ePXP to the eLCDIF through an on-chip SRAM buffer. The eLCDIF can support up to 32-bit interfaces.

# 1.1.4 Graphics Accelerators

Integrated graphics accelerators offload processing from the ARM processor, enabling high performance graphic applications at minimum power.

• Pixel Processing Pipeline (ePXP)

The ePXP is a high-performance pixel processor capable of 1 pixel/clock performance for combined operations, such as color-space conversion, alpha blending, gamma mapping, and

rotation. The ePXP is enhanced with features specifically for grayscale applications working in conjunction with the electrophoretic display controller to form a full grayscale display solution. In addition, the ePXP supports traditional pixel/frame processing paths for still-image and video processing applications, allowing it to interface with the integrated LCD controller (eLCDIF).

• Graphics acceleration The i.MX50 provides a 2D graphics accelerator with performance up to 200 Mpix/s.

### 1.1.5 Multilevel Memory System

The multilevel memory system of the i.MX50 is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The i.MX50 supports many types of external memory devices, including DDR2, LPDDR2, LPDDR1, NOR Flash, PSRAM, Cellular RAM, NAND Flash (MLC and SLC) and OneNAND<sup>TM</sup>, and managed NAND including eMMC up to rev 4.4.

### 1.1.6 Smart Speed<sup>™</sup> Technology

The i.MX50 device has power management throughout the SOC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart Speed technology enables the designer to deliver a feature-rich product that requires levels of power that are far less than industry expectations.

### 1.1.7 Interface Flexibility

The i.MX50 supports connection to a variety of interfaces, including an LCD controller for displays, two high-speed USB on-the-go-capable PHYs, multiple expansion card ports (high-speed MMC/SDIO host and others), 10/100 Ethernet controller, and a variety of other popular interfaces (for example, UART,  $I^2C$ , and  $I^2S$  serial audio).

### 1.1.8 Advanced Security

The i.MX50 delivers hardware-enabled security features, such as High-Assurance Boot 4 (HAB4) for signed/authenticated firmware images, basic DRM support with random private keys and AES encryption/decryption, and storage and programmability of on-chip fuses.

# 1.2 Features

The i.MX50 Application Processor (AP) is based on ARM Cortex-A8 platform and has the following features:

- MMU, L1 instruction cache, and L1 data cache

- Unified L2 cache

- 800 MHz target frequency of the core (including NEON, VFPv3, and L1 cache)

- NEON coprocessor (SIMD Media Processing Architecture) and Vector Floating Point (VFP-Lite) coprocessor supporting VFPv3

i.MX50 Applications Processors for Consumer Products, Rev. 0

#### Introduction

The memory system consists of the following components:

- Level 1 cache:

- Instruction (32 Kbyte)

- Data (32 Kbyte)

- Level 2 cache:

- Unified instruction and data (256 Kbyte)

- Level 2 (internal) memory:

- Boot ROM, including HAB (96 Kbyte)

- Internal multimedia/shared, fast access RAM (128 Kbyte)

- External memory interfaces:

- 16/32-bit DDR2-533, LPDDR2-533, or LPDDR1-400 up to a total of 2 GByte

- 8-bit NAND SLC/MLC Flash with up to 100 MHz synchronous clock rate and up to 32-bit hardware ECC for 1 Kbyte block size

- 16/32-bit NOR Flash with a dedicated 16-bit muxed-mode interface. I/O muxing logic selects EIMv2 port as primary muxing at system boot.

- 16-bit PSRAM, Cellular RAM

- Managed NAND, including eMMC up to rev 4.4

The i.MX50 introduces a next generation system bus fabric architecture that aggregates various sub-system buses and masters for access to system peripherals and memories. The various bus-systems and components are as follows:

- 64-bit AXI Fabric (266 MHz)—This bus-fabric is the SoC's central bus aggregation point.

- Provides access to all slave targets in the SoC:

- ROM (ROMCP)

- On-chip RAM (OCRAM)

- External DRAM (DRAM MC)

- External static RAM (EIM)

- Interrupt controller (TZIC)

- Decode into the AHB MAX crossbar second level AHB fabric.

- Provides arbitration to the following masters in the system:

- ARM CPU complex

- Pixel processing pipeline (ePXP)

- Electrophoretic display controller (EPDC)

- eLCDIF LCD display controller

- DCP Crypto engine

- BCH ECC engine

- MAX AHB crossbar

- GPU 2D

- SDMA

- USBOH1 (USB OTG and host controller complex)

- FEC Ethernet controller

- MAX AHB crossbar (133 MHz)—This connects the various AHB bus sub-segments in the system and provides decode into the following slaves:

- IP-Bus 1 (66 MHz)—This bus segment contains peripherals accessible by the ARM core and without DMA capability

- IP-Bus 2 (66 MHz)—This bus segment contains peripherals accessible by the ARM core and without DMA capability

- APBH DMA bridge (133 MHz)—The APBH DMA bridge is a master to the MAX for its memory-side DMA operations. The APBH bus is an AMBA APB slave bus providing peripheral access to many of the high-speed IP blocks on the i.MX50.

- IP-Bus 3 (66 MHz)—This third peripheral bus segment contains peripherals accessible by the ARM core and SDMA and as such houses peripherals with DMA capability. The IP-Bus 3 can be accessed by the ARM CPU through IP-Bus 1 and SPBA.

- Quality of service controller (QoSC)—This provides both soft and dynamic arbitration/priority control. The QoSC works in conjunction with the critical display modules such as the eLCDIF and EPDC to provide dynamic priority control, based on real-time metrics.

The i.MX50 makes use of dedicated hardware accelerators to achieve state-of-the-art multimedia performance. The use of hardware accelerators provides both high performance and low power consumption, while freeing up the CPU core for other tasks.

The i.MX50 incorporates the following hardware accelerators:

- GPU2Dv1—2D Graphics accelerator, OpenVG 1.1, 200 Mpix/s performance

- ePXP—enhanced PiXel Processing Pipeline off loading key pixel processing operations required to support both LCD and EPD display applications

The i.MX50 includes the following interfaces to external devices:

### NOTE

Not all the interfaces are available simultaneously depending on I/O multiplexer configuration.

- Displays:

- EPDC (i.MX508 Only)—Supporting direct-driver TFT backplanes beyond 2048 × 1536 at 106 Hz refresh (or 4096 × 4096 at 20 Hz)

- eLCDIF—Supporting beyond SXGA + (1400 × 1050) at 60 Hz resolutions with up to a 32-bit display interface

- On the i.MX508, both displays can be active simultaneously. If both displays are active, the eLCDIF only provides a 16-bit interface due to pin muxing.

- Expansion cards:

- Four SD/MMC card

- USB:

- One High Speed (HS) USB 2.0 OTG-capable port with integrated HS USB PHY

#### i.MX50 Applications Processors for Consumer Products, Rev. 0

#### Introduction

- One High Speed (HS) USB 2.0 host port with integrated HS USB PHY

- Miscellaneous interfaces:

- One-wire (OWIRE) port

- Two I2S/SSI/AC97 ports, supporting up to 1.4 Mbps each connected to the Audio Multiplexer (AUDMUX) providing four external ports

- Five UART RS232 ports, up to 4.0 Mbps each

- Two eCSPI (Enhanced CSPI) ports, up to 66 Mbps each plus CSPI port, up to 16.6 Mbps

- Three  $I^2C$  ports, supporting 400 kbps

- Fast Ethernet controller IEEE 802.3, 10/100 Mbps

- Key pad port (KPP)

- Two pulse width modulators (PWM)

- GPIO with interrupt capabilities

- Secure JTAG controller (SJC)

The system supports efficient and smart power control and clocking:

- Supporting DVFS techniques for low power modes, including auto slow architecture

- Power gating-SRPG (state retention power gating) for ARM core and NEON

- Support for various levels of system power modes

- Flexible clock gating control scheme

- On-chip temperature monitor

- On-chip 32 kHz and 24 MHz oscillators

- A total of four PLLs with the fourth PLL providing up to eight independently controllable outputs, improving the ease of clocking control, especially for display and connectivity modules

Security functions are enabled and accelerated by the following hardware:

- Secure JTAG controller (SJC)—Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features

- Secure real-time clock (SRTC)—Tamper resistant RTC with dedicated power domain and mechanism to detect voltage and clock glitches

- Advanced high assurance boot (A-HAB)—HAB with the next embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization

#### 1.3 **Ordering Information**

Table 1 provides the ordering information.

| Part Number   | Mask<br>Set | Features                  | Ambient<br>Temperature<br>Range ( <sup>°</sup> C) | Package <sup>1</sup>                             |

|---------------|-------------|---------------------------|---------------------------------------------------|--------------------------------------------------|

| MCIMX508CVK8B | N78A        | Full Specification        | 0 to 70                                           | 13 x 13 mm, 0.5 mm pitch BGA<br>Case: 416MAPBGA  |

| MCIMX508CVM8B | N78A        | Full Specification        | 0 to 70                                           | 17 x 17 mm, 0.8 mm pitch BGA<br>Case: 400MAPBGA  |

| MCIMX507CVM8B | N78A        | No GPU                    | 0 to 70                                           | 17 x 17 mm, 0.8 mm pitch BGA,<br>Case: 400MAPBGA |

| MCIMX503CVM8B | N78A        | No EPD controller         | 0 to 70                                           | 17 x 17 mm, 0.8 mm pitch BGA<br>Case: 400MAPBGA  |

| MCIMX502CVM8B | N78A        | No GPU, no EPD controller | 0 to 70                                           | 17 x 17 mm, 0.8 mm pitch BGA,<br>Case: 400MAPBGA |

**Table 1. Ordering Information**

Case MAPBGA is RoHS compliant, lead-free MSL (Moisture Sensitivity Level) 3.

#### 1.4 Part Number Feature Comparison

Table 2 provides an overview of the feature differences between the i.MX50 part numbers.

**Table 2. Part Number Feature Comparison**

| Part Number | Disabled<br>Features | Comments                                                                                                                                                                                                                                                                |

|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCIMX508    | None                 |                                                                                                                                                                                                                                                                         |

| MCIMX507    | GPU                  |                                                                                                                                                                                                                                                                         |

| MCIMX503    | EPDC                 | The i.MX503 has the same ballmap and IOMUX as the i.MX508. The EPDC pins still exist on the i.MX503, but because the EPDC block is disabled, those pins cannot be used for EPDC functionality (ALT0) and must be configured in the IOMUX with another ALT-mode setting. |

| MCIMX502    | GPU, EPDC            | The i.MX502 has the same ballmap and IOMUX as the i.MX508. The EPDC pins still exist on the i.MX502, but because the EPDC block is disabled, those pins cannot be used for EPDC functionality (ALT0) and must be configured in the IOMUX with another ALT-mode setting. |

# **1.5** Package Feature Comparison

Table 3 provides an overview of the feature and pin differences between the i.MX50 packages.

### Table 3. Package Feature Comparison

| Package   | Dimensions                  | I/O Pin Differences<br>Versus 416MAPBGA                                                              | Notes on Package Differences                                                                                                                                                                                                                             |

|-----------|-----------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 416MAPBGA | 13 x 13 mm,<br>0.5 mm pitch | _                                                                                                    | <ul> <li>USB_OTG_VDDA25 and USB_H1_VDDA25 are shorted together on the 416MAPBGA package substrate.</li> <li>USB_OTG_VDDA33 and USB_H1_VDDA33 are shorted together on the 416MAPBGA package substrate.</li> </ul>                                         |

| 400MAPBGA | 17 x 17 mm,<br>0.8 mm pitch | Deleted Pins:<br>DRAM_SDCLK_1<br>DRAM_SDCLK_1_B<br>DRAM_A14<br>DRAM_SDODT1<br>UART2_CTS<br>UART2_RTS | <ul> <li>USB_OTG_VDDA25 and USB_H1_VDDA25 are independent and NOT shorted together on the 400MAPBGA package substrate.</li> <li>USB_OTG_VDDA33 and USB_H1_VDDA33 are independent and NOT shorted together on the 400MAPBGA package substrate.</li> </ul> |

# 2 Architectural Overview

The following sections provide an architectural overview of the i.MX50 processor system.

# 2.1 Block Diagram

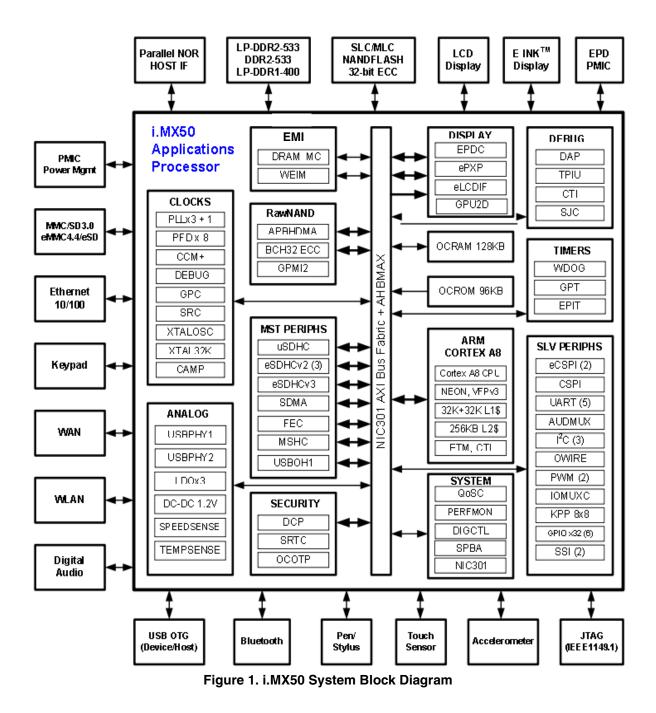

Figure 1 shows the functional modules in the i.MX50 processor system.

i.MX50 Applications Processors for Consumer Products, Rev. 0

### NOTE

The numbers in brackets indicate the number of module instances. For example, PWM (2) indicates two separate PWM peripherals.

# 3 Modules List

The i.MX50 processor contains a variety of digital and analog modules that are described in Table 4 in alphabetical order.

| Block<br>Mnemonic | Block Name                               | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM<br>Cortex-A8  | ARM Cortex-A8<br>Platform                | ARM                                     | The ARM Cortex-A8 Core Platform consists of the ARM Cortex-A8 processor<br>and its essential sub-blocks. It contains the 32 Kbyte L1 instruction cache,<br>32 Kbyte L1 data cache, Level 2 cache controller and a 256 Kbyte L2 cache.<br>The platform also contains an event monitor and debug modules. It also has<br>a NEON co-processor with SIMD media processing architecture, register file<br>with 32 × 64-bit general-purpose registers, an Integer execute pipeline (ALU,<br>Shift, MAC), dual, single-precision floating point execute pipeline (FADD,<br>FMUL), load/store and permute pipeline, and a non-pipelined vector floating<br>point (VFP Lite) co-processor supporting VFPv3. |

| EPDC              | Electrophoretic<br>Display<br>Controller | Display<br>Peripherals                  | The EPDC is a feature-rich, low power, and high-performance direct-drive active matrix EPD controller. It is specifically designed to drive E-INK <sup>TM</sup> EPD panels supporting a wide variety of TFT backplanes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ePXP              | enhanced PiXel<br>Processing<br>Pipeline | Display<br>Peripherals                  | A high-performance pixel processor capable of 1 pixel/clock performance for combined operations such as color-space conversion, alpha blending, gamma-mapping, and rotation. The ePXP is enhanced with features specifically for grayscale applications. In addition, the ePXP supports traditional pixel/frame processing paths for still-image and video processing applications allowing it to interface with the integrated LCD controller (eLCDIF).                                                                                                                                                                                                                                           |

| eLCDIF            | enhanced LCD<br>Interface                | Display<br>Peripherals                  | The eLCDIF is a high-performance LCD controller interface supporting a rich set of modes allowing inter operability with a wide variety of LCD panels, including DOTCK/RGB and smart panels. The module also supports a synchronous operation with the ePXP to allow the processed frames to be passed from the ePXP to the eLCDIF through an on-chip SRAM buffer. The eLCDIF can support up to 32-bit interfaces.                                                                                                                                                                                                                                                                                 |

| AUDMUX            | Digital Audio<br>Mux                     | Slave<br>Connectivity<br>Peripherals    | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example, SSI1<br>and SSI2) and peripheral serial interfaces (audio and voice codecs). The<br>AUDMUX has six ports (two internal and four external) with identical<br>functionality and programming models. A desired connectivity is achieved by<br>configuring two or more AUDMUX ports.                                                                                                                                                                                                                                                                          |

| CAMP-1            | Clock Amplifier                          | Clocks,<br>Resets, and<br>Power Control | Clock Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Block<br>Mnemonic          | Block Name                                                                          | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|-------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCM<br>GPC<br>SRC          | Clock Control<br>Module<br>Global Power<br>Controller<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system,<br>and also for system power management.<br>The system includes four PLLs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CSPI<br>eCSPI-1<br>eCSPI-2 | Configurable<br>SPI, Enhanced<br>CSPI                                               | Slave<br>Connectivity<br>Peripherals    | Full-duplex enhanced synchronous serial interface, with data rate up to 66.5 Mbit/s (for eCSPI, master mode). It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DAP<br>TPIU<br>CTI         | Debug System                                                                        | System<br>Control<br>Peripherals        | The Debug System provides real-time trace debug capability of both<br>instructions and data. It supports a trace protocol that is an integral part of the<br>ARM Real Time Debug solution (RealView).<br>Real-time tracing is controlled by specifying a set of triggering and filtering<br>resources, which include address and data comparators, three cross-system<br>triggers (CTI), counters, and sequencers.<br>Debug access port (DAP)—The DAP provides real-time access for the<br>debugger without halting the core to System memory and peripheral<br>registers. All debug configuration registers and Debugger access to JTAG<br>scan chains. |

| DRAM MC                    | DRAM Memory<br>Controller                                                           | External<br>Memory<br>Interface         | The DRAM MC consists of a DRAM memory controller and PHY, supporting LPDDR2, DDR2, and LPDDR1 memories with clock frequencies up to 266 MHz with 32-bit interface. It is tightly linked with the system bus fabric and employs advanced arbitration mechanism to maximize DRAM bandwidth efficiency.                                                                                                                                                                                                                                                                                                                                                     |

| EIM                        | Static Memory<br>Controller                                                         | External<br>Memory<br>Interface         | The EIM is an external static memory and generic host interface. It supports<br>up to a 32-bit interface (through pin-muxing) or a dedicated 16-bit muxed<br>interface. It can be used to interface to PSRAMs (sync and async), NOR-flash<br>or any external memory mapped peripheral.                                                                                                                                                                                                                                                                                                                                                                   |

| BCH32/GPMI2                | Raw NAND<br>System with<br>ECC                                                      | RawNAND<br>and SSP<br>Peripherals       | The i.MX50 contains a fully hardware accelerated raw NAND flash solution supporting SLC and MLC devices. The system consists of the GPMI2 module, which is driven by the APBH DMA engine to perform the NAND flash interface function (supporting up to ONFI2.1). Coupled with the GPMI2 is the BCH32 hardware error-correction engine which is an AXI bus-master and supports up to 32-bits of correction over block sizes up to 1 Kbyte (that is, supports up to 2 Kbyte code-size).                                                                                                                                                                   |

| System Fabric<br>and QoS   | System Fabric<br>and QoS                                                            | System<br>Peripherals                   | In order to aggregate the multitude of masters and memory mapped devices,<br>the i.MX50 contains a next-generation AMBA3 AXI bus fabric. In addition, the<br>i.MX50 contains a Quality of Service Controller IP (QoSC) which allows both<br>soft priority control and dynamic priority elevation. Software priority control<br>works for all masters but dynamic hardware control only works for EPDC and<br>eLCDIF.                                                                                                                                                                                                                                     |

| EPIT                       | Enhanced<br>Periodic<br>Interrupt Timer                                             | Timer<br>Peripherals                    | Each EPIT is a 32-bit <i>set and forget</i> timer that starts counting after the EPIT is enabled by software. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. It has a 12-bit prescaler for division of input clock frequency to get the required time setting for the interrupts to occur, and counter values can be programmed on the fly.                                                                                                                                                                                                                                                     |

#### **Modules List**

| Block<br>Mnemonic                                        | Block Name                                                                                        | Subsystem                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eSDHCv3-3<br>(eMMC 4.4)                                  | Ultra-High-<br>Speed<br>Multi-Media<br>Card/<br>Secure Digital<br>card host<br>controller, ver. 3 | Master<br>Connectivity<br>Peripherals | Ultra High-Speed eSDHC, enhanced to support eMMC 4.4 standard specification, for 832 Mbps.<br>IP is backward compatible to eSDHCv2 IP. See complete features listing in eSDHCv2 entry below.<br>Port 3 is specifically enhanced to support eMMC 4.4 specification, for double data rate (832 Mbps, 8-bit port).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| eSDHCv2-1<br>eSDHCv2-2<br>eSDHCv2-4                      | Enhanced<br>Multi-Media<br>Card/<br>Secure Digital<br>Host Controller,<br>ver. 2                  |                                       | <ul> <li>In Enhanced Multi-Media Card/Secure Digital Host Controller the Ports 1, 2, and 4 are compatible with the <i>MMC System Specification</i> version 4.3, full support</li> <li>The generic features of the eSDHCv2 module, when serving as SD/MMC host, include the following: <ul> <li>Can be configured either as SD/MMC controller</li> <li>Supports eSD and eMMC standard, for SD/MMC embedded type cards</li> <li>Conforms to <i>SD Host Controller Standard Specification</i> version 2.0, full support</li> <li>Compatible with the SD Memory Card Specification version 1.1</li> <li>Compatible with the SDIO Card Specification version 1.2</li> <li>Designed to work with SD Memory, miniSD Memory, SDIO, miniSDIO, SD Combo, MMC and MMC RS cards</li> <li>Configurable to work in one of the following modes: <ul> <li>—SD/SDIO 1-bit, 4-bit</li> <li>—MMC 1-bit, 4-bit</li> <li>Host clock frequency variable between 32 kHz to 52 MHz</li> <li>Up to 200 Mbps data transfer for SD/SDIO cards using four parallel data lines</li> </ul> </li> </ul></li></ul> |

| FEC                                                      | Fast Ethernet<br>Controller                                                                       | Master<br>Connectivity<br>Peripherals | The Ethernet Media Access Controller (MAC) is designed to support both 10 Mbps and 100 Mbps Ethernet/IEEE Std 802.3 <sup>™</sup> networks. An external transceiver interface and transceiver function are required to complete the interface to the media.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6 | General<br>Purpose I/O<br>Modules                                                                 | Slave<br>Connectivity<br>Peripherals  | These modules are used for general purpose input/output to external ICs.<br>Each GPIO module supports up to 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPT                                                      | General<br>Purpose Timer                                                                          | Timer<br>Peripherals                  | Each GPT is a 32-bit <i>free-running</i> or <i>set</i> and <i>forget</i> mode timer with a programmable prescaler and compare and capture register. A timer counter value can be captured using an external event, and can be configured to trigger a capture event on either the leading or trailing edges of an input pulse. When the timer is configured to operate in "set and forget" mode, it is capable of providing precise interrupts at regular intervals with minimal processor intervention. The counter has output compare logic to provide the status and interrupt at comparison. This timer can be configured to run either on an external clock or on an internal clock.                                                                                                                                                                                                                                                                                                                                                                                          |

| Block<br>Mnemonic                                              | Block Name                                | Subsystem                            | Brief Description                                                                                                                                                                                                                                                |

|----------------------------------------------------------------|-------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPU2Dv1                                                        | Graphics<br>Processing<br>Unit-2D, ver. 1 | Display<br>Peripherals               | The GPU2Dv1 provides hardware acceleration for 2D graphic algorithms with sufficient processor power to run desk-top quality interactive graphics applications on displays up to HD1080 resolution.                                                              |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3 | I <sup>2</sup> C Interface                | Connectivity<br>Peripherals          | $I^2C$ provides serial interface for controlling peripheral devices. Data rates of up to 400 kbps are supported.                                                                                                                                                 |

| OCOTP<br>Controller                                            | On-chip OTP<br>controller                 | Security<br>Peripherals              | The on-chip one-time -programmable (OCOTP) ROM serves the functions of hardware and software capability bits, Freescale operations and unique-ID, the customer-programmable cryptography key, and storage of various ROM and general purpose configuration bits. |

| IOMUXC                                                         | IOMUX Control                             | Slave<br>Connectivity<br>Peripherals | This module enables flexible I/O multiplexing. Each I/O pad has default as well as several alternate functions. The alternate functions are software configurable.                                                                                               |

| КРР                                                            | Keypad Port                               | Slave<br>Connectivity<br>Peripherals | <ul> <li>The KPP supports an 8 × 8 external keypad matrix. The KPP features are as follows:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>               |

| OWIRE                                                          | One-Wire<br>Interface                     | Slave<br>Connectivity<br>Peripherals | One-Wire support provided for interfacing with an on-board EEPROM, and smart battery interfaces, for example, Dallas DS2502.                                                                                                                                     |

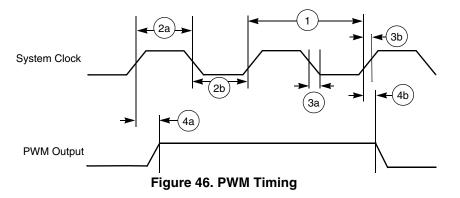

| PWM-1<br>PWM-2                                                 | Pulse Width<br>Modulation                 | Slave<br>Connectivity<br>Peripherals | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones. The PWM uses 16-bit resolution and a 4 x 16 data FIFO to generate sound.                                    |

| RAM<br>128 Kbytes                                              | Internal RAM                              | Internal<br>Memory                   | The On-Chip Memory controller (OCRAM) module, is an interface between<br>the system's AXI bus, to the internal (on-chip) SRAM memory module. It is<br>used for controlling the 128 Kbyte multimedia RAM, through a 64-bit AXI bus.                               |

| ROM<br>96 Kbytes                                               | Boot ROM                                  | Internal<br>Memory                   | Supports secure and regular Boot Modes.<br>The ROM Controller supports ROM Patching.                                                                                                                                                                             |

#### **Modules List**

| Block<br>Mnemonic | Block Name                          | Subsystem                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|-------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDMA              | Smart Direct<br>Memory<br>Access    | Master<br>Connectivity<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by offloading various cores in dynamic data routing.</li> <li>The SDMA features list is as follows:</li> <li>Powered by a 16-bit instruction-set micro-RISC engine</li> <li>Multi-channel DMA supports up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM Cortex-A8 and SDMA</li> <li>Very fast context-switching with two-level priority-based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle uni-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers for EMI</li> <li>Support of byte-swapping and CRC calculations</li> <li>A library of scripts and API is available</li> </ul> |

| SJC               | Secure JTAG<br>Controller           | System<br>Control<br>Peripherals      | The Secure JTAG Controller provides a mechanism for regulating JTAG access, preventing unauthorized JTAG usage while allowing JTAG access for manufacturing tests and software debugging.<br>The i.MX50 JTAG port provides debug access to several hardware blocks including the ARM processor and the system bus, therefore, it must be accessible for initial laboratory bring-up, manufacturing tests and troubleshooting, and for software debugging by authorized entities. However, if the JTAG port is left unsecured it provides a method for executing unauthorized program code, getting control over secure applications, and running code in privileged modes.<br>The Secure JTAG controller provides three different security modes that can be selected through an e-fuse configuration to prevent unauthorized JTAG access.                                                                                                                                                                                                                                                                                                           |

| SPBA              | Shared<br>Peripheral Bus<br>Arbiter | System<br>Control<br>Peripherals      | SPBA (Shared Peripheral Bus Arbiter) is a two-to-one IP bus interface (IP bus) arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SRTC              | Secure Real<br>Time Clock           | Security<br>Peripherals               | The SRTC incorporates a special System State Retention Register (SSRR) that stores system parameters during system shutdown modes. This register and all SRTC counters are powered by dedicated supply rail NVCC_SRTC. The NVCC_SRTC can be energized separately even if all other supply rails are shut down. This register is helpful for storing warm boot parameters. The SSRR also stores the system security state. In case of a security violation, the SSRR marks the event (security violation indication).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 4. i.MX50 Digital and Analog Modules (continued)

| Block<br>Mnemonic                              | Block Name                                             | Subsystem                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------|--------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2                                 | I2S/SSI/AC97<br>Interface                              | Slave<br>Connectivity<br>Peripherals  | The SSI is a full-duplex synchronous interface used on the i.MX50 processor to provide connectivity with off-chip audio peripherals. The SSI interfaces connect internally to the AUDMUX for mapping to external ports. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock/frame sync options. Each SSI has two pairs of 8 x 24 FIFOs and hardware support for an external DMA controller in order to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream, which reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| Temperature<br>Monitor                         | Temp Sensor                                            | Analog                                | The temperature sensor is an internal module to the i.MX50 that monitors the die temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface,<br>ver. 2                              | Slave<br>Connectivity<br>Peripherals  | <ul> <li>Each of the UARTv2 modules supports the following serial data transmit/receive protocols and configurations:</li> <li>7 or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd, or none)</li> <li>Programmable bit-rates up to 4 Mbps. This is a higher max baud rate relative to the 1.875 Mbps, which is specified by the TIA/EIA-232-F standard.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> </ul>                                                                                                                                                                                      |

| USB-OH-1                                       | USB 2.0<br>High-Speed<br>OTG-capable<br>and Host ports | Master<br>Connectivity<br>Peripherals | <ul> <li>USB-OH-1 supports USB2.0 HS/FS/LS, and contains:</li> <li>One high-speed OTG-capable module with integrated HS USB PHY</li> <li>One high-speed Host module with integrated HS USB PHY</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-1                                         | Watch Dog                                              | Timer<br>Peripherals                  | The Watchdog (WDOG) timer module protects against system failures by providing a method of escaping from unexpected events or programming errors. The WDOG Timer supports two comparison points during each counting period. Each of the comparison points is configurable to invoke an interrupt to the ARM core, and a second point invokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                  |

| XTALOSC                                        | Crystal<br>Oscillator I/F                              | Clocking                              | The XTALOSC module combined with an external 24 MHz crystal with load capacitors implements a crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**Modules List**

# 3.1 Special Signal Considerations

Table 5 lists special signal considerations for the i.MX50. The signal names are listed in alphabetical order. The package contact assignments are found in Section 5, "Package Information and Contact Assignments." The signal descriptions are defined in the *MCIMX50 Applications Processor Reference Manual* (MCIMX50RM).

| Signal Name                                                   | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_MODE0,<br>BOOT_MODE1                                     | These two input pins are sampled out of reset and set the boot mode. For Internal boot, they should be set to 00. For Internal Fuse Only boot, they should be set to 10. For USB downloader, they should be set to 11. The BOOTMODE pins are in the NVCC_RESET domain and include an internal 100K pull-up resistor at start-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BOOT_CONFIG1[7:0],<br>BOOT_CONFIG2[7:0],<br>BOOT_CONFIG3[7:0] | These 24 pins are the GPIO boot override pins and may be driven at power up to select the boot mode. They are sampled 4 x CKIL clock cycles after POR is de-asserted. Consult the "System Boot" chapter of the Reference Manual for more details. Note that these are not dedicated pins: the BOOT_CONFIG pins appear over 24 pins of the EIM interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BT_LPB_FREQ[1:0]                                              | If the LOW_BATT_GPIO (UART4_TXD) is asserted at power up, the BT_LPB_FREQ[1:0] pins will<br>be sampled to determine the ARM core frequency. Consult the "System Boot" chapter of the<br>Reference Manual for more details.<br>Note that these are not dedicated pins: BT_LPB_FREQ0 appears on SSI_TXFS and<br>BT_LPB_FREQ1 appears on SSI_TXC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CHRG_DET_B                                                    | This is the USB Charger Detect pin. It is an open drain output pin that expects a 100 K pull-up. This pin is asserted low when a USB charger is detected on the OTG PHY DP and DM. This detection occurs with the application of VBUS. This pin is a raw sensor output and care must be taken to follow the system timings outlined in the USB charger specification Rev 1.1. This pin can be controlled by software control as well. If not used, this pin should be tied to ground or left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| СКІН                                                          | This is an input to the CAMPs (Clock Amplifiers), which include on-chip AC-coupling precluding<br>the need for external coupling capacitors. The CAMPs are enabled by default, but the main clocks<br>feeding the on-chip clock tree are sourced from XTAL/EXTAL by default. Optionally, the use of a<br>low jitter external oscillators to feed CKIH (while not required) can be an advantage if low jitter or<br>special frequency clock sources are required by modules sourced by CKIH. See CCM chapter in<br>the <i>MCIMX50 Applications Processor Reference Manual</i> (MCIMX50RM) for details on the<br>respective clock trees.<br>After initialization, the CAMPs may be disabled if not used by programming the CCR CAMPx_EN<br>field. If disabled, the on-chip CAMP output is low and the input is irrelevant. CKIH is on the<br>NVCC_JTAG power domain, so the input clock amplitude should not exceed NVCC_JTAG.<br>If unused, the user should tie CKIH to GND for best practice. |

| CKIL/ECKIL                                                    | The user must tie a fundamental mode 32.768 K crystal across ECKIL and CKIL. The target ESR should be 50 K or less. The bias resistor for the amplifier is integrated and approximately 14 M $\Omega$ . The target load capacitance for the crystal is approximately 10 pF. The load capacitors on the board should be slightly less than double this value after taking parasitics into account. While driving in an external 32 KHz signal into ECKIL, CKIL should be left floating so that it biases. A differential amplifier senses these two pins to propagate the clock inside the i.MX508. Care must be taken to minimize external leakages on ECKIL and CKIL. If they are significant to the 14 M $\Omega$ feedback or 1 $\mu$ A, then loss of oscillation margin or cessation of oscillation may result.                                                                                                                                                                            |

### **Table 5. Special Signal Considerations**

| Signal Name                                                      | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM_OPEN,<br>DRAM_OPENFB<br>(416MAPBGA and<br>400MAPBGA Only)   | These pins are the echo gating output and feedback pins used by the DRAM PHY to bound a window around the DQS transition. For an application using a single DRAM device, these pins should be routed so that the trace length (DRAM_OPEN + DRAM_OPENFB) = trace length (DRAM_SDCLK0 + DRAM_SDQS0). For an application using two DRAM devices, they should be routed so that the trace length (DRAM_OPEN + DRAM_OPENFB) = trace length (DRAM_OPEN + DRAM_OPENFB) = trace length (AVG(DRAM_SDCLK0+DRAM_SDCLK1) + AVG (DRAM_SDQS0_to_Device0 + DRAM_SDQS0_to_Device1)). This connection is required for mDDR, LPDDR2, and DDR2. |

| DRAM_SDODT0,<br>DRAM_SDODT1<br>(416MAPBGA and<br>400MAPBGA Only) | These pins are the On-die termination outputs from the i.MX50.<br>For DDR2, these pins should be connected to the DDR2 DRAM ODT pins. For LPDDR2 and mDDR, these pins should be left floating. Only SDODT0 exists on the 400MAPBGA package.                                                                                                                                                                                                                                                                                                                                                                                  |

| DRAM_CALIBRATION                                                 | This pin is the ZQ calibration used to calibrate DRAM Ron and ODT.<br>For LPDDR2, this pin should be connected to ground through a 240 $\Omega$ 1% resistor. For DDR2<br>and LPDDR1, this pin should be connected to ground through a 300 $\Omega$ 1% resistor.                                                                                                                                                                                                                                                                                                                                                              |

| JTAG_MOD                                                         | This input has an internal 100K pull-down. Note that JTAG_MOD is referenced as SJC_MOD in the <i>MCIMX50 Applications Processor Reference Manual</i> (MCIMX50RM) - both names refer to the same signal. JTAG_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed.                                                                                                                                                                                                                                                     |

| JTAG_TCK                                                         | This input has an internal 100K pull-down. This pin is in the NVCC_JTAG domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| JTAG_TDI                                                         | This input has an internal 47K pull-up to NVCC_JTAG. This pin is in the NVCC_JTAG domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| JTAG_TDO                                                         | This is a 3-state output with an internal gate keeper enable to prevent a floating condition. An external pull-up or pull-down resistor on JTAG_TDO is detrimental and should be avoided. This pin is in the NVCC_JTAG domain.                                                                                                                                                                                                                                                                                                                                                                                               |

| JTAG_TMS                                                         | This input has an internal 47K pull-up to NVCC_JTAG. This pin is in the NVCC_JTAG domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| JTAG_TRSTB                                                       | This input has an internal 47K pull-up to NVCC_JTAG. This pin is in the NVCC_JTAG domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |