## Low Skew CMOS PLL Clock Drivers

The MC88915 Clock Driver utilizes phase-locked loop technology to lock its low skew outputs' frequency and phase onto an input reference clock. It is designed to provide clock distribution for high performance PC's and workstations.

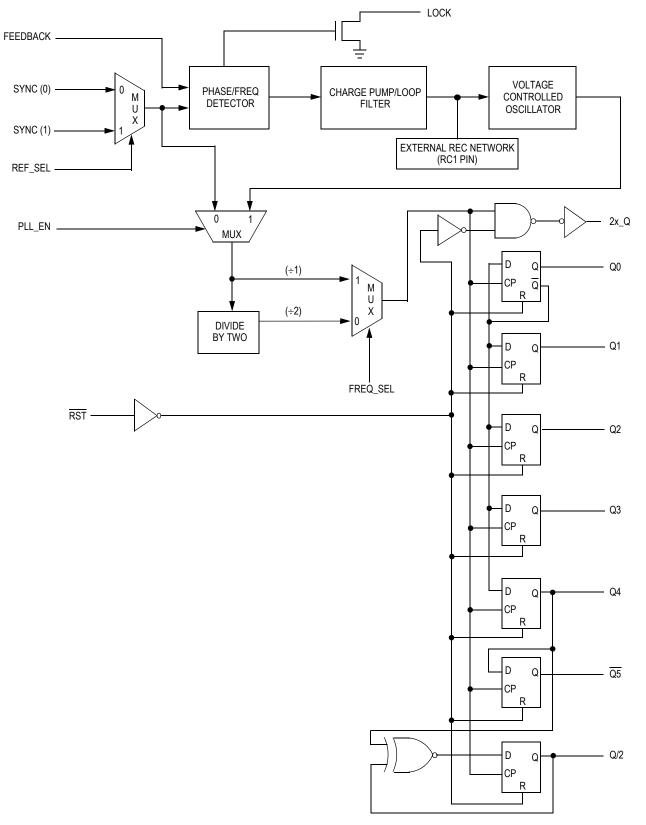

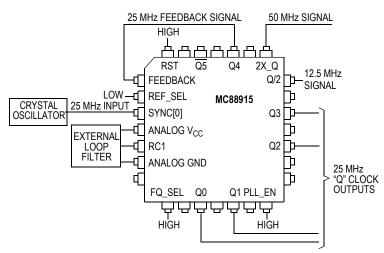

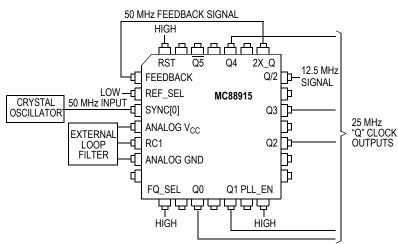

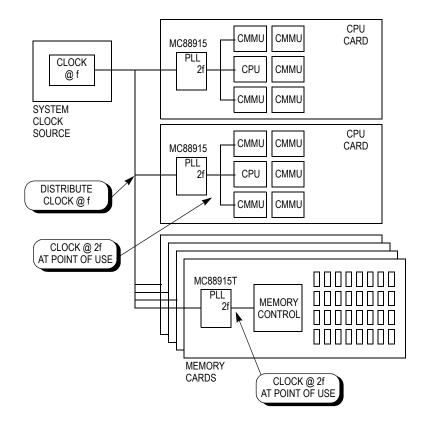

The PLL allows the high current, low skew outputs to lock onto a single clock input and distribute it to multiple components on a board. The PLL also allows the MC88915 to multiply a low frequency input clock and distribute it locally at a higher (2X) system frequency. Multiple 88915's can lock onto a single reference clock, which is ideal for applications when a central system clock must be distributed synchronously to multiple boards (see Figure 9).

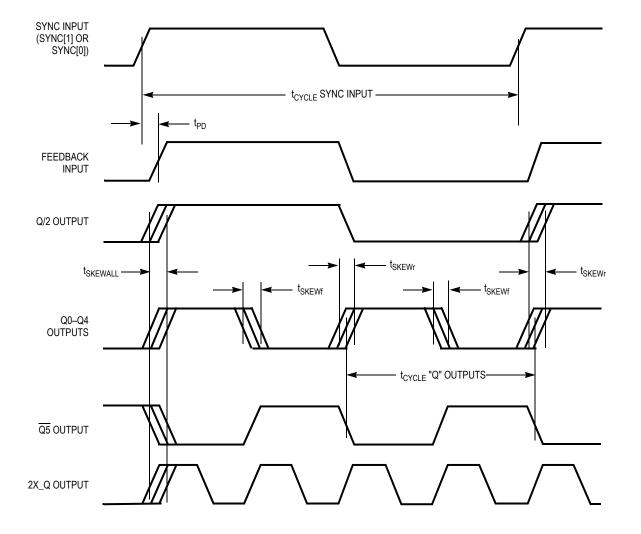

Five "Q" outputs (QO-Q4) are provided with less than 500 ps skew between their rising edges. The  $\overline{Q5}$  output is inverted (180° phase shift) from the "Q" outputs. The 2X Q output runs at twice the "Q" output frequency, while the Q/2 runs at 1/2 the "Q" frequency.

The VCO is designed to run optimally between 20 MHz and the 2X Q Fmax specification. The wiring diagrams in Figure 5 detail the different feedback configurations which create specific input/output frequency relationships. Possible frequency ratios of the "Q" outputs to the SYNC input are 2:1, 1:1, and 1:2.

The FREQ SEL pin provides one bit programmable divide-by in the feedback path of the PLL. It selects between divide-by-1 and divide-by-2 of the VCO before its signal reaches the internal clock distribution section of the chip (see the block diagram on page 2). In most applications FREQ SEL should be held high (÷1). If a low frequency reference clock input is used, holding FREQ\_SEL low (÷2) will allow the VCO to run in its optimal range (>20 MHz).

In normal phase-locked operation, the PLL\_EN pin is held high. Pulling the PLL\_EN pin low disables the VCO and puts the 88915 in a static "test mode". In this mode there is no frequency limitation on the input clock, which is necessary for a low frequency board test environment. The second SYNC input can be used as a test clock input to further simplify board-level testing (see detailed description on page 11).

A lock indicator output (LOCK) will go high when the loop is in steady-state phase and frequency lock. The LOCK output will go low if phase-lock is lost or when the PLL EN pin is low. Under certain conditions the lock output may remain low, even though the part is phase-locked. Therefore, the LOCK output signal should not be used to drive any active circuitry; it should be used for passive monitoring or evaluation purposes only.

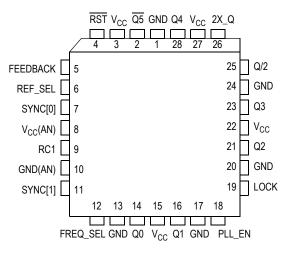

# LOW SKEW CMOS PLL **CLOCK DRIVER FN SUFFIX** 28-LEAD PLCC PACKAGE CASE 776-02 **EI SUFFIX** 28-LEAD PLCC PACKAGE **Pb-FREE PACKAGE** CASE 776-02

#### Features

- Five outputs (Q0–Q4) with output-output skew < 500 ps, each being phase and frequency locked to the SYNC input •

- The phase variation from part-to-part between the SYNC and FEEDBACK inputs is less than 550 ps (derived from the tpp specification, defining the part-to-part skew).

- Input/output phase-locked frequency ratios of 1:2, 1:1, and 2:1 are available

- Input frequency range from 5 MHz 2X\_Q f<sub>max</sub> specification

- Additional outputs available at 2X and +2 the system "Q" frequency. Also, a  $\overline{Q}$  (180° phase shift) output available •

- All outputs have ±36 mA drive (equal high and low) at CMOS levels, and can drive either CMOS or TTL inputs. All inputs are TTL-level compatible.

- Test mode pin (PLL EN) provided for low frequency testing. Two selectable CLOCK inputs for test or redundancy purposes.

- 28-lead Pb-free package available.

Figure 1. Pinout: 28-Lead PLCC (Top View)

#### Table 1. Pin Summary

| Pin Name              | Number | I/O    | Function                                                                                   |

|-----------------------|--------|--------|--------------------------------------------------------------------------------------------|

| SYNC[0]               | 1      | Input  | Reference clock input                                                                      |

| SYNC[1]               | 1      | Input  | Reference clock input                                                                      |

| REF_SEL               | 1      | Input  | Chooses reference between SYNC[0] and SYNC[1]                                              |

| FREQ_SEL              | 1      | Input  | Selects Q output frequency                                                                 |

| FEEDBACK              | 1      | Input  | Feedback input to phase detector                                                           |

| RC1                   | 1      | Input  | Input for external RC network                                                              |

| Q(0-4)                | 5      | Output | Clock output (locked to SYNC)                                                              |

| <u>Q5</u>             | 1      | Output | Inverse of clock output                                                                    |

| 2x_Q                  | 1      | Output | 2 x clock output (Q) frequency (synchronous)                                               |

| Q/2                   | 1      | Output | Clock output (Q) frequency ÷ 2 (synchronous)                                               |

| LOCK                  | 1      | Output | Indicates phase lock has been achieved (high when locked)                                  |

| RST                   | 1      | Input  | Asynchronous reset (active low)                                                            |

| PLL_EN                | 1      | Input  | Disables phase-lock for low frequency testing                                              |

| V <sub>CC</sub> , GND | 11     |        | Power and ground pins (note pins 8 and 10 are "quiet" supply pins for internal logic only) |

#### Table 2. DC Electrical Characteristics (Voltages Referenced to GND)

TA =  $0^{\circ}$ C to +70°C, VCC = 5.0 V ± 5%

| Symbol           | Parameter                                      | Test Conditions                                      | v <sub>cc</sub><br>v | Target<br>Limit    | Unit |

|------------------|------------------------------------------------|------------------------------------------------------|----------------------|--------------------|------|

| V <sub>IH</sub>  | Minimum High-Level Input Voltage               | $V_{out}$ = 0.1 V or $V_{CC}$ – 0.1 V                | 4.75                 | 2.0                | V    |

|                  |                                                |                                                      | 5.25                 | 2.0                |      |

| V <sub>IL</sub>  | Maximum Low-Level Input Voltage                | $V_{out}$ = 0.1 V or $V_{CC}$ – 0.1 V                | 4.75                 | 0.8                | V    |

|                  |                                                |                                                      | 5.25                 | 0.8                |      |

| V <sub>OH</sub>  | Minimum High-Level Output Voltage              | $V_{in} = V_{IH} \text{ or } V_{IL}$                 | 4.75                 | 4.01               | V    |

|                  |                                                | I <sub>OH</sub> = –36 mA <sup>(1)</sup>              | 5.25                 | 4.51               |      |

| V <sub>OL</sub>  | Maximum Low-Level Output Voltage               | V <sub>in</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 4.75                 | 0.44               | V    |

|                  |                                                | I <sub>OH</sub> = 36 mA <sup>(1)</sup>               | 5.25                 | 0.44               |      |

| I <sub>in</sub>  | Maximum Input Leakage Current                  | V <sub>I</sub> = V <sub>CC</sub> or GND              | 5.25                 | ± 1.0              | μA   |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input                 | $V_{\rm I} = V_{\rm CC} - 2.1  \rm V$                | 5.25                 | 1.5 <sup>(2)</sup> | mA   |

| I <sub>OLD</sub> | Minimum Dynamic Output Current <sup>(3)</sup>  | V <sub>OLD</sub> = 1.0 V Maximum                     | 5.25                 | 88                 | mA   |

| I <sub>OHD</sub> |                                                | V <sub>OHD</sub> = 3.85 V Minimum                    | 5.25                 | -88                | mA   |

| I <sub>CC</sub>  | Maximum Quiescent Supply Current (per Package) | $V_{I} = V_{CC}$ or GND                              | 5.25                 | 1.0                | mA   |

1. IOL and IOH are 12 mA and -12 mA respectively for the LOCK output.

2. The PLL\_EN input pin is not guaranteed to meet this specification.

3. Maximum test duration is 2.0ms, one output loaded at a time.

#### Table 3. Capacitance and Power Specifications

| Symbol          | Parameter                                                               | Typical Values                  | Unit | Conditions                          |

|-----------------|-------------------------------------------------------------------------|---------------------------------|------|-------------------------------------|

| C <sub>IN</sub> | Input Capacitance                                                       | 4.5                             | pF   | V <sub>CC</sub> = 5.0 V             |

| C <sub>PD</sub> | Power Dissipation Capacitance                                           | 40                              | pF   | V <sub>CC</sub> = 5.0 V             |

| PD <sub>1</sub> | Power Dissipation @ 33 MHz with 50 $\Omega$ Thevenin Termination        | 15 mW/Output<br>120 mW/Device   | mW   | V <sub>CC</sub> = 5.0 V<br>T = 25°C |

| PD <sub>2</sub> | Power Dissipation @ 33 MHz with 50 $\Omega$ Parallel Termination to GND | 37.5 mW/Output<br>300 mW/Device | mW   | V <sub>CC</sub> = 5.0 V<br>T = 25°C |

#### Table 4. SYNC Input Timing Requirements

| Symbol                 | Parameter                                                     | Minimum |           | Maximum            | Unit |

|------------------------|---------------------------------------------------------------|---------|-----------|--------------------|------|

| t <sub>RISE/FALL</sub> | Maximum Rise and Fall times, SYNC Inputs from 0.8 to 2.0 V $$ | —       |           | 3.0                | ns   |

| tCYCLE                 | Input Clock Period SYNC Inputs                                | FN55    | FN70      | 200 <sup>(1)</sup> | ns   |

|                        |                                                               | 36      | 28.5      |                    |      |

| Duty Cycle             | Input Duty Cycle SYNC Inputs                                  |         | 50% ± 25% |                    |      |

1. Information in Figure 5 and in Note 3. in the General AC Specification Notes describes this specification and its actual limits depending on application.

#### Table 5. Frequency Specifications ( $T_A = 0^{\circ}C$ to +70 °C, $V_{CC} = 5.0 \text{ V} \pm 5\%$ , $C_L = 5.0 \text{ pF}$ )

| Symbol                          | Devenuedor                                     | Guarantee   | Unit        |      |

|---------------------------------|------------------------------------------------|-------------|-------------|------|

| Symbol                          | Parameter                                      | MC88915FN55 | MC88915FN70 | Unit |

| f <sub>max</sub> <sup>(1)</sup> | Maximum Operating Frequency (2X_Q Output)      | 55          | 70          | MHz  |

|                                 | Maximum Operating Frequency (Q0–Q4, Q5 Output) | 27.5        | 35          | MHz  |

1. Maximum Operating Frequency is guaranteed with the part in a phase-locked condition, and all outputs loaded at 50 pF.

| Symbol                                                                | Parameter                                                                                                           | Min                          | Мах                         | Unit |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------|------|

| t <sub>RISE</sub> , t <sub>FALL</sub><br>(Outputs)                    | Rise and Fall Times, all Outputs Into a 50 pF, 500 $\Omega$ Load (Between 0.2 $V_{CC}$ and 0.8 $V_{CC})$            | 1.0                          | 2.5                         | ns   |

| t <sub>RISE</sub> , t <sub>FALL</sub> <sup>(1)</sup><br>(2X_Q Output) | Rise and Fall Time, 2X_Q Output Into a 20 pF Load With Termination specified in note 2 (Between 0.8 V and 2.0 V)    | 0.5                          | 1.6                         | ns   |

| t <sub>Pulse Width</sub> (1)                                          | Output Pulse Width (Q0, Q1, Q3, Q4, Q5, Q/2 @V <sub>CC</sub> /2)                                                    | 0.5t <sub>CYCLE</sub> - 0.5  | 0.5t <sub>CYCLE</sub> + 0.5 |      |

| (Q0,Q1,Q3,Q4,<br>Q5,Q/2)                                              |                                                                                                                     |                              | at which the "Q" re running | ns   |

| t <sub>Pulse Width</sub> <sup>(1)</sup><br>(Q2 only)                  | Output Pulse Width (Q2 Output @ V <sub>CC</sub> /2)                                                                 | 0.5t <sub>CYCLE</sub> - 0.6  | 0.5t <sub>CYCLE</sub> + 0.6 | ns   |

| t <sub>Pulse Width</sub> <sup>(1)</sup><br>(2X_Q Output)              | Output Pulse Width (2X_Q Output @ 1.5 V) (See General AC Specification note 2)                                      | 0.5t <sub>CYCLE</sub> - 0.5  | 0.5t <sub>CYCLE</sub> + 0.5 | ns   |

| t <sub>Pulse Width</sub> <sup>(1)</sup><br>(2X_Q Output)              | Output Pulse Width (2X_Q Output @ V <sub>CC</sub> /2)                                                               | 0.5t <sub>CYCLE</sub> - 1.0  | 0.5t <sub>CYCLE</sub> + 1.0 | ns   |

| t <sub>PD</sub> <sup>(1)</sup>                                        | SYNC input to feedback delay                                                                                        | (470 kΩ From F               |                             |      |

| (Sync-Feedback)                                                       | (meas. @ SYNC0 or 1 and FEEDBACK input pins)<br>(See General AC Specification Note 4. and Figure 4 for explanation) | -1.05                        | -0.50                       |      |

|                                                                       | (See General AC Specification Note 4, and Figure 4 for explanation)                                                 | (470 kΩ From RC1 to An. GND) |                             | ns   |

|                                                                       |                                                                                                                     | +1.25                        | +3.25                       |      |

| t <sub>SKEWr</sub> <sup>(2)</sup><br>(Rising)                         | Output-to-Output Skew Between Outputs Q0 - Q4, Q/2<br>(Rising Edges Only)                                           | _                            | 500                         | ps   |

| t <sub>SKEWf</sub> <sup>(1), (2)</sup><br>(Falling)                   | Output-to-Output Skew Between Outputs Q0 - Q4<br>(Falling Edges Only)                                               | _                            | 750                         | ps   |

| t <sub>SKEWall</sub> <sup>(1), (2)</sup>                              | Output-to-Output Skew Between Outputs 2X_Q, Q/2, Q0 - Q4<br>Rising, Q5 Falling                                      | _                            | 750                         | ps   |

| <sup>t</sup> LOCK                                                     | Time Required to acquire <sup>(3)</sup> Phase-Lock from time SYNC Input Signal is Received.                         | 1                            | 10                          | ms   |

| t <sub>PHL</sub><br>(Reset - Q)                                       | Propagation Delay, RST to Any Output (High-Low)                                                                     | 1.5                          | 13.5                        | ns   |

| Table 6. | AC Electrical | Characteristics ( | (T <sub>A</sub> =0° C to ⋅ | +70° C, V <sub>CC</sub> = 5.0 | OV ±5%, C <sub>L</sub> = 50pF) |

|----------|---------------|-------------------|----------------------------|-------------------------------|--------------------------------|

|          |               |                   |                            |                               |                                |

1. These specifications are not tested, they are guaranteed by statistical characterization. See General AC Specification note 1.

2. Under equally loaded conditions, CL  $\leq$  50 pF (±2 pF), and at a fixed temperature and voltage.

3. With  $V_{CC}$  fully powered-on and an output properly connected to the FEEDBACK pin.  $t_{LOCK}$ , Max. is with C1 = 0.1µF,  $t_{LOCK}$  Min. is with C1 = 0.01µF.

#### Table 7. Reset Timing Requirements<sup>(1)</sup>

| Symbol                            | Parameter                                                | Minimum | Unit |

|-----------------------------------|----------------------------------------------------------|---------|------|

| t <sub>REC</sub> , RST<br>to SYNC | Reset Recovery Time rising RST edge to falling SYNC edge | 9.0     | ns   |

| t <sub>W</sub> , RST<br>LOW       | Minimum Pulse Width, RST input LOW                       | 5.0     | ns   |

1. These reset specs are valid only when PLL\_EN is LOW and the part is in Test mode (not in phase-lock)

#### **GENERAL AC SPECIFICATION NOTES**

- Statistical characterization techniques were used to guarantee those specifications which cannot be measured on the ATE. MC88915 units were fabricated with key transistor properties intentionally varied to create a 14-cell designed experimental matrix. IC performance was characterized over a range of transistor properties (represented by the 14 cells) in excess of the expected process variation of the wafer fabrication area. In this way all units passing the ATE test will meet or exceed the non-tested specifications limits.

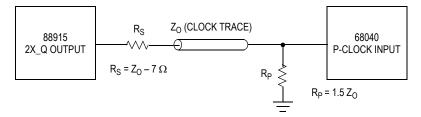

- These two specs (t<sub>RISE/FALL</sub> and t<sub>PULSE</sub> Width 2X\_Q output) guarantee the MC88915 meets the 25 MHz MC68040 P-Clock input specification (at 50 MHz). For

these two specs to be guaranteed by Freescale Semiconductor, the termination scheme shown below in Figure 3 must be used.

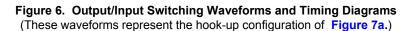

3. The wiring diagrams and explanations in Figure 7 demonstrate the input and output frequency relationships for three possible feedback configurations. The allowable SYNC input range for each case is also indicated. There are two allowable SYNC frequency ranges, depending whether FREQ\_SEL is high or low. Although not shown, it is possible to feed back the Q5 output, thus creating a 180° phase shift between the SYNC input and the "Q" outputs. Table 8 below summarizes the allowable SYNC frequency range for each possible configuration.

Figure 3. MC68040 P-Clock Input Termination Scheme

| Table O   | Allower has a White her |              |             |                |            |               |

|-----------|-------------------------|--------------|-------------|----------------|------------|---------------|

| i able 8. | Allowable SYNC In       | put Frequenc | y Ranges to | or Different i | гееараск С | onfigurations |

| FREQ_SEL<br>Level | Feedback<br>Output | Allowable SYNC Input<br>Frequency Range (MHz) | Corresponding VCO<br>Frequency Range | Phase Relationships<br>of the "Q" Outputs<br>to Rising SYNC Edge |

|-------------------|--------------------|-----------------------------------------------|--------------------------------------|------------------------------------------------------------------|

| HIGH              | Q/2                | 5 to (2X_Q FMAX Spec)/4                       | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

| HIGH              | Any "Q" (Q0–Q4)    | 10 to (2X_Q FMAX Spec)/2                      | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

| HIGH              | Q5                 | 10 to (2X_Q FMAX Spec)/2                      | 20 to (2X_Q FMAX Spec)               | 180°                                                             |

| HIGH              | 2X_Q               | 20 to (2X_Q FMAX Spec)                        | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

| LOW               | Q/2                | 2.5 to (2X_Q FMAX Spec)/8                     | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

| LOW               | Any "Q" (Q0–Q4)    | 5 to (2X_Q FMAX Spec)/4                       | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

| LOW               | Q5                 | 5 to (2X_Q FMAX Spec)/4                       | 20 to (2X_Q FMAX Spec)               | 180°                                                             |

| LOW               | 2X_Q               | 10 to (2X_Q FMAX Spec)/2                      | 20 to (2X_Q FMAX Spec)               | 0°                                                               |

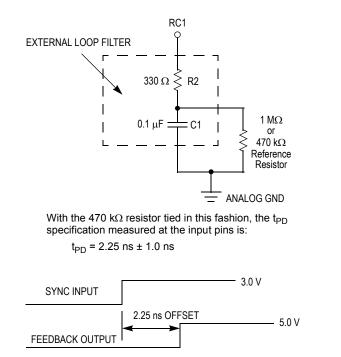

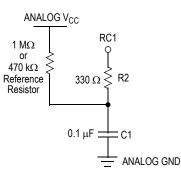

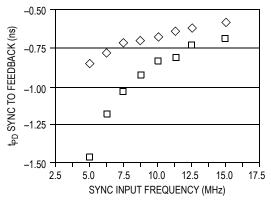

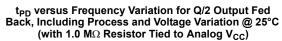

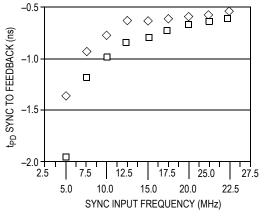

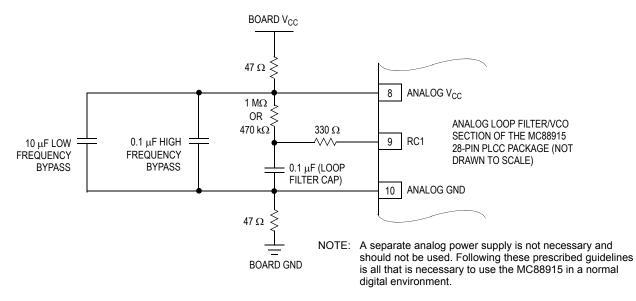

4. A 1 M $\Omega$  resistor tied to either Analog V<sub>CC</sub> or Analog GND, depicted in Figure 4, is required to ensure no jitter is present on the MC88915 outputs. This technique causes a phase offset between the SYNC input and the output connected to the FEEDBACK input, measured at the input pins. The t<sub>PD</sub> spec describes how this offset varies with process, temperature, and voltage. The specs were determined by measuring the phase

relationship for the 14 lots described in Note 1 while the part was in phase-locked operation. The actual measurements were made with a 10 MHz SYNC input (1.0 ns edge rate from 0.8 V – 2.0 V) with the Q/2 output fed back. The phase measurements were made at 1.5 V. The Q/2 output was terminated at the FEEDBACK input with 100  $\Omega$  to V<sub>CC</sub> and 100  $\Omega$  to ground.

#### MC88915 LOW SKEW CMOS PLL CLOCK DRIVERS

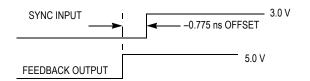

With the 470 k $\Omega$  resistor tied in this fashion, the t<sub>PD</sub> specification measured at the input pins is: t<sub>PD</sub> = -0.775 ns ± 0.275 ns

Figure 4. Depiction of the Fixed SYNC to Feedback Offset (t<sub>PD</sub>) Which is Present When a 470 k $\Omega$  Resistor is Tied to V<sub>CC</sub> or Ground

5. The t<sub>SKEWr</sub> specification guarantees the rising edges of outputs Q/2, Q0, Q1, Q2, Q3, and Q4 will always fall within a 500 ps window within one part. However, if the relative position of each output within this window is not specified, the 500 ps window must be added to each side of the t<sub>PD</sub> specification limits to calculate the total part-to-part skew. For this reason, the absolute distribution of these outputs are provided in Table 9. When taking the skew data, Q0 was used as a reference, so all measurements are relative to this output. The information in Table 9 is derived from measurements taken from the 14 process lots described in Note 1, over the temperature and voltage range.

#### 6. Calculation of Total Output-to-Skew Between Multiple Parts (Part-to-Part Skew)

By combining the  $t_{PD}$  specification and the information in Note 5, the worst case output-to-output skew between multiple 88915s connected in parallel can be calculated. This calculation assumes all parts have a common SYNC input clock with equal delay of input signal to each part. This skew value is valid at the 88915 output pins only (equally loaded), it does not include PCB trace delays due to varying loads.

With a 1.0 M $\Omega$  resistor tied to analog V<sub>CC</sub> as shown in Note 4, the t<sub>PD</sub> spec. limits between SYNC and the Q/2 output (connected to the FEEDBACK pin) are –1.05 ns and –0.5 ns. To calculate the skew of any given output between two or more parts, the absolute value of the distribution of the output given in Table 9 must be subtracted and added to the lower and upper t<sub>PD</sub> spec limits respectively. For output Q2, [276 – (–44)] = 320 ps is the absolute value of the distribution. Therefore, [–1.05 ns –

Table 9. Relative Positions of Outputs Q/2, Q0–Q4, 2X\_Q Within the 500 ps t<sub>SKEWr</sub> Spec Window

| Output | – (ps) | + (ps) |

|--------|--------|--------|

| Q0     | 0      | 0      |

| Q1     | -72    | 40     |

| Q2     | -44    | 276    |

| Q3     | -40    | 255    |

| Q4     | -274   | -34    |

| Q/2    | -16    | 250    |

| 2X_Q   | -633   | -35    |

0.32 ns] = -1.37 ns is the lower  $t_{PD}$  limit, and [-0.5 ns + 0.32 ns] = -0.18 ns is the upper limit. Therefore, the worst case skew of output Q2 between any number of parts is |(-1.37) - (-0.18)| = 1.19 ns. Q2 has the worst case skew distribution of any output, so 1.2 ns is the absolute worst case output-to-output skew between multiple parts.

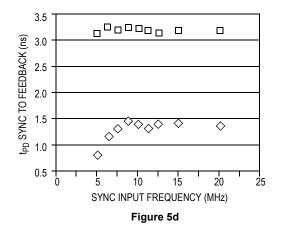

7. Note 4 explains that the  $t_{PD}$  specification was measured and is guaranteed for the configuration of the Q/2 output connected to the FEEDBACK pin and the SYNC input running at 10 MHz. The fixed offset ( $t_{PD}$ ) as described above has some dependence on the input frequency and at what frequency the VCO is running. The graphs of Figure 5 demonstrate this dependence.

The data presented in Figure 5 is from devices representing process extremes, and the measurements were also taken at the voltage extremes ( $V_{CC}$  = 5.25 V and 4.75 V). Therefore, the data in Figure 5 is a realistic representation of the variation of t<sub>PD</sub>.

#### MC88915 LOW SKEW CMOS PLL CLOCK DRIVERS

Figure 5a

Figure 5b

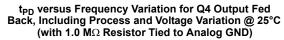

$t_{PD}$  versus Frequency Variation for Q4 Output Fed Back, Including Process and Voltage Variation @ 25°C (with 1.0 M $\Omega$  Resistor Tied to Analog V<sub>CC</sub>)

#### TIMING NOTES:

- 1. The MC88915 aligns rising edges of the FEEDBACK input and SYNC input; therefore, the SYNC input does not require a 50% duty cycle.

- All skew specs are measured between the VCC/2 crossing point of the appropriate output edges. All skews are specified as "windows," not as a ± deviation around a center point.

- If a "Q" output is connected to the FEEDBACK input (this situation is not shown), the "Q" output frequency would match the SYNC input frequency, the 2X\_Q output would run at twice the SYNC frequency, and the Q/2 output would run at half the SYNC frequency.

#### 1:2 Input to "Q" Output Frequency Relationship

In this application, the Q/2 output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of Q/2 and SYNC, thus the Q/2 frequency will equal the SYNC frequency. The "Q" outputs (Q0–Q4, Q5) will always run at 2X the Q/2 frequency, and the 2X\_Q output will run at 4X the Q/2 frequency.

#### Allowable Input Frequency Range:

5 MHz to (2X\_Q FMAX Spec)/4 (for FREQ\_SEL HIGH) 2.5 MHz to (2X\_Q FMAX Spec)/8 (for FREQ\_SEL LOW)

#### 1:1 Input to "Q" Output Frequency Relationship

In this application, the Q4 output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of Q4 and SYNC, thus the Q4 frequency (and the rest of the "Q" outputs) will equal the SYNC frequency. The Q/2 output will always rn at 1/2 the "Q" frequency, and the 2X\_Q output will run at 2X the "Q" frequency.

#### Allowable Input Frequency Range:

10 MHz to (2X\_Q FMAX Spec)/2 (for FREQ\_SEL HIGH) 5 MHz to (2X\_Q FMAX Spec)/4 (for FREQ\_SEL LOW)

#### 2:1 Input to "Q" Output Frequency Relationship

In this application, the 2X\_Q output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of 2X\_Q and SYNC, thus the 2X\_Q frequency will equal the SYNC frequency. The Q/2 output will always run at 1/4 the 2X\_Q frequency, and the "Q" outputs will run at 1/2 the 2X\_Q frequency.

#### <sup>1</sup> Allowable Input Frequency Range:

20 MHz to (2X\_Q FMAX Spec) (for FREQ\_SEL HIGH) 10 MHz to (2X\_Q FMAX Spec)/2 (for FREQ\_SEL LOW)

#### Figure 7. Wiring Diagrams

Figure 8. Recommended Loop Filter and Analog Isolation Scheme for the MC88915

#### NOTES CONCERNING LOOP FILTER AND BOARD LAYOUT ISSUES

- 1. Figure 8 shows a loop filter and analog isolation scheme which will be effective in most applications. The following guidelines should be followed to ensure stable and jitter-free operation:

- All loop filter and analog isolation components should be tied as close to the package as possible. Stray current passing through the parasitics of long traces can cause undesirable voltage transients at the RC1 pin.

- b. The 47  $\Omega$  resistors, the 10  $\mu$ F low frequency bypass capacitor, and the 0.1  $\mu$ F high frequency bypass capacitor form a wide bandwidth filter minimizing the 88915's sensitivity to voltage transients from the system digital V<sub>CC</sub> supply and ground planes. This filter will typically ensure a 100 mV step deviation on the digital V<sub>CC</sub> supply, causing no more than a 100 ps phase deviation on the 88915 outputs. A 250 mV step deviation on V<sub>CC</sub> using the recommended filter values should cause no more than 250 ps phase deviation; if a 25  $\mu$ F bypass capacitor is used (instead of 10  $\mu$ F) a 250 mV V<sub>CC</sub> step should cause no more than a 100 ps phase deviation.

If good bypass techniques are used on a board design near components potentially causing digital  $V_{CC}$  and ground noise, the above described  $V_{CC}$  step deviations should not occur at the 88915's

digital V<sub>CC</sub> supply. The purpose of the bypass filtering scheme shown in Figure 8 is to give the 88915 additional protection from the power supply and ground plane transients potentially occurring in a high frequency, high speed digital system.

- c. There are no special requirements set forth for the loop filter resistors (1 M $\Omega$  or 470 K $\Omega$  and 330  $\Omega$ ). The loop filter capacitor (0.1  $\mu$ F) can be a ceramic chip capacitor, the same as a standard bypass capacitor.

- d. The 1 M $\Omega$  or 470 K $\Omega$  reference resistor injects current into the internal charge pump of the PLL, causing a fixed offset between the outputs and the SYNC input. This also prevents excessive jitter caused by inherent PLL dead-band. If the VCO (2X\_Q output) is running above 40 MHz, the 470 K $\Omega$  resistor provides the correct amount of current injection into the charge pump (2–3  $\mu$ A). If the VCO is running below 40 MHz, a 1.0 M $\Omega$  reference resistor should be used (instead of 470 K $\Omega$ ).

- 2. In addition to the bypass capacitors used in the analog filter of Figure 8, there should be a 0.1  $\mu$ F bypass capacitor between each of the other (digital) four V<sub>CC</sub> pins and the board ground plane. This will reduce output switching noise caused by the 88915 outputs, in addition to reducing potential for noise in the "analog" section of the chip. These bypass capacitors should also be tied as close to the 88915 package as possible.

Figure 9. Representation of a Potential Multi-Processing Application Utilizing the MC88915 for Frequency Multiplication and Low Board-to-Board Skew

#### MC88915 SYSTEM LEVEL TESTING FUNCTIONALITY

When the PLL\_EN pin is low, the VCO is disabled and the 88915 is in low frequency "test mode". In test mode (with FREQ\_SEL high), the 2X\_Q output is inverted from the selected SYNC input, and the "Q" outputs are divide-by-2 (negative edge triggered) of the SYNC input, and the Q/2 output is divide-by-4. With FREQ\_SEL low the 2X\_Q output is divide-by-2 of the SYNC, the "Q" outputs divide-by-4, and the Q/2 output divide-by-8. These relationships can be seen on the block diagram. A recommended test configuration

would be to use SYNC0 as the test clock input, and tie PLL\_EN and REF\_SEL together and connect them to the test select logic. When these inputs are low, the 88915 is in test mode and the SYNC0 input is selected.

This functionality is needed since most board-level testers run at 1 MHz or below, and the 88915 cannot lock onto that low of an input frequency. In the test mode described above, any frequency test signal can be used.

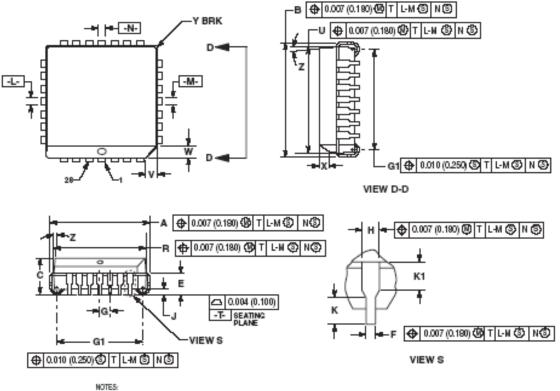

#### PACKAGE DIMENSIONS

- DATUNS -L., -N., AND -N. DETERMINED WHERE TOP OF LEAD SHOULDER EXISTS PLASTIC BODY AT MOLD PARTING LINE.

- 2. DIMENSION G1, TRUE POSITION TO BE MEASURED AT DATUM -T-, SEATING PLANE. 8. DIMENSIONS R AND U DO NOTINCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.290) PER SIDE.

- 0010/0250/PER SIDE 4. DIMENSIONING AND TOLEPAN CING PER ANSI Y145N, 1082 5. CONTROLLING DEMENSION INCH 6. THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012 (0.300), DIMENSIONS R AND U APE DETERNINED AT THE OLITERMICST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY INISINATCH BETWEEN THE TOP AND BOTTOM OF THE PLASITC BODY. 7. DIMENSION H DOES NOT INCLUDE DAMBAR

- PROTEUSION OF INTRUSION, THE DAMBAR PROTRUSION (5) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.057 (0.940). THE DAMBAR IN TRUSION (S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

|     | INCHES |       | MILLIN | IETER8 |

|-----|--------|-------|--------|--------|

| DIM | MIH    | MAX   | MIN    | MAX    |

| A   | 0.485  | 0.495 | 12.32  | 12.57  |

| в   | 0.485  | 0.495 | 12.32  | 12.57  |

| С   | 0.165  | 0.180 | 4.20   | 4.57   |

| E   | 0.090  | 0.110 | 2.29   | 2.79   |

| F   | 0.013  | 0.019 | 0.35   | 0.48   |

| G   | 0.050  | BBC   | 1.27   | BSC    |

| н   | 0.036  | 0.032 | 33.0   | 0.81   |

| 1   | 0.020  |       | 0.51   |        |

| К   | 0.025  |       | 0.64   |        |

| R   | 0.450  | 0.458 | 11.43  | 11.58  |

| U   | 0.450  | 0.458 | 11.43  | 11.58  |

| V   | 0.042  | 0.048 | 1.07   | 1.21   |

| W   | 0.042  | 0.048 | 1.07   | 1.21   |

| X   | 0.042  | 0.068 | 1.07   | 1.42   |

| Ŷ   |        | 0.020 |        | 0.50   |

| z   | 2      | 10    | 2      | 10°    |

| G1  | 0.410  | 0.430 | 10.42  | 10.92  |

| K1  | 0.040  |       | 1.02   |        |

#### CASE 776-02 **ISSUE D** PLCC PLASTIC PACKAGE

### Innovate with IDT and accelerate your future networks. Contact:

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited 321 Kingston Road Leatherhead, Surrey KT22 7TU England +44 (0) 1372 363 339 Fax: +44 (0) 1372 378851

© 2007 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA