# L64733/L64734 Tuner and Satellite Receiver Chipset

Datasheet

Downloaded from Datasheet.su

The L64733/34 chipset is designed specifically to meet the needs of satellite broadcast digital TV and is compliant with the European digital video broadcast (DVB-S) standard and the technical specifications for DSS systems. The chipset forms a complete "L-Band to bits" system.

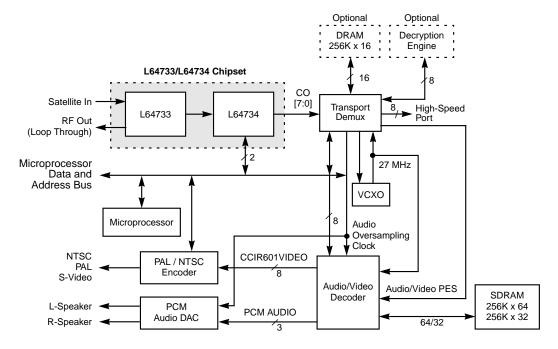

A typical application of the L64733/34 chipset is satellite digital TV reception in accordance with ETS 300 421. Figure 1 shows the L64733/34 chipset satellite receiver implemented in a typical satellite receiver set-top decoder box.

Figure 1 Block Diagram of Set-Top Decoder Box Using the L64733/34 Chipset

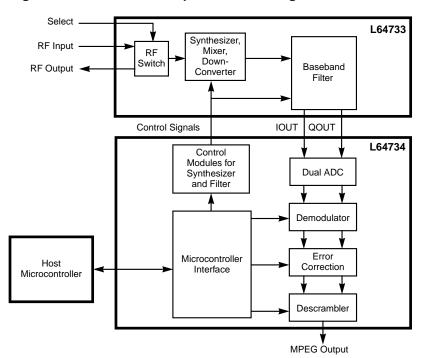

The L64733/34 chipset consists of the L64734 Satellite Receiver IC, the L64733 Tuner IC, and an on-chip synthesizer. Figure 2 shows a simplified block diagram of this chipset.

August 2000 1

Figure 2 L64733/34 Simplified Block Diagram

#### The L64734:

- generates control signals for the L64733 synthesizer, using frequency information programmed into the L64734 configuration registers

- controls the programming of the low-pass filters on the L64733

- generates dual AGC control voltages for the two-stage automatic gain control on the L64733 IC.

The L64733 Tuner IC directly down-converts the satellite signal from L-band to baseband.

Figure 3 shows a more detailed chipset block diagram.

L64733 Charge Pump Xtal Phase To External Osc by 8 Detect. Loop Filter 4-7.26 MHz Quadrature Down-Converter RF In RF Amp Switch RF Out -Tank vco Fc Circuit Dual-Modulus Prescaler PSOÚT **FDOUB** FLCLK PLLIN QOUT IOUT INSEL AGC1 AGC2 MOD CPG L64734 Filter AGC Control Module Control Synthesizer Control Module Carrier oop Control **BPSK/QPSK** Timing Loop Demodulator Control DEMI Interpolator/Decimation Dual Matched Output ADC Filter Filter DEMQ Microcontroller Data and Address Bus Clk (from L64734 on-chip PLL) External Microcontroller Interface **FEC Decoder Pipeline** Microcontroller Data and Address Bus Channel Output (MPEG-2 Reed-Reed-Viterbi Convolutional Solomon Synchronizer Solomon Descrambler Decoder Deinterleaver Transport Stream) Viterbi Synchronizer

Figure 3 **Detailed Chipset Block Diagram**

The L64733 directly accepts the RF In L-Band signal input from the satellite LNB feed. The L64733 handles a fully loaded raster of transponder signals from 925 MHz to 2175 MHz. RF In is internally matched to 75  $\Omega$ , and except for a DC-blocking capacitor, requires no matching network between the cable connector and the L64733 input pins. The L64733 uses the L64734 INSEL signal to select the appropriate RF function (Normal or Loop-Through mode).

The RF signal goes to a variable gain stage, which is controlled by the L64734 AGC1 signal. The L64734 adjusts AGC1 in conjunction with AGC2 to maximize the SNR of the RF signal while maintaining proper levels at the baseband outputs (IOUT and QOUT). The signal then goes to two mixers in the quadrature demodulator. The mixers are fed with local oscillator signals that are offset by 90 degrees from one another. The quadrature demodulator performs a direct frequency conversion of the RF signal to baseband while splitting the signal into quadrature I and Q signal paths.

The baseband signals pass through a pair of variable-gain amplifiers that are controlled by the AGC2 pin, which, in turn is controlled by the L64734. The signals are then filtered through a pair of 7th-order filters for anti-aliasing. The filter shape is 7th-order Butterworth, followed by a single-pole delay equalizer. The filter cut-off frequency, which is controlled by the L64734 FLCLK signal, is related to the baud rate. The filtered baseband output signals go to the differential output stages at IOUTp, IOUTn, QOUTp and QOUTn.

The baseband outputs of the L64733 go to the L64734, where they are digitized by the analog-to-digital converter (ADC). The outputs then go to a BPSK/QPSK demodulator, where they are filtered. The demodulator then sends them to the L64734 FEC decoder pipeline, which outputs an MPEG-2 transport stream.

The frequency synthesizer functionality is split between the L64733 and L64734. The Synthesizer Control Module resides on the L64734; it generates control signals for the L64733 Tuner IC frequency synthesizer. The Synthesizer Control Module also contains some of the programmable counters that are part of the synthesizer feedback loop.

The L64733 contains many of the analog functions of the frequency synthesizer, as well as the RF local oscillator and crystal reference oscillator. Tuning oscillator signals are generated for the mixers in the

L64733/L64734 Tuner and Satellite Receiver Chipset

range from 925–2175 MHz, with a 0.5 MHz step size when using a 4-MHz crystal reference. The on-chip VCO tuning frequency is 543 MHz to 1088 MHz. To tune channels from 925–1086 MHz, the L64734 disables the frequency doubler (X2 block) on the L64733. To tune channels from 1086 MHz to 2175 MHz, the L64734 enables the frequency doubler. The VCO requires an external resonant tank circuit, which includes varactor diodes to vary the frequency of oscillation.

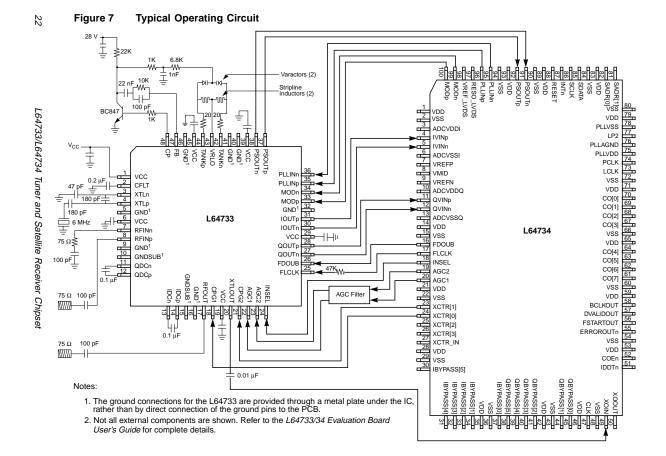

The VCO signal goes to the Prescaler block before it is passed to the L64734 differentially through the PSOUTp and PSOUTn pins. The L64734 MODp and MODn differential signals control the divider ratio for the Prescaler block. The L64734 dynamically changes the divide ratio to ensure that the tuning step size is not affected by the divider. The L64734 contains programmable counters to further divide the signal in frequency before the signal is fed back to the L64733 through the PLLINp and PLLINn pins. The crystal reference oscillator frequency is divided by eight, then fed to the phase detector. The phase detector generates a current signal proportional to the difference in phase between PLLINp, PLLINn, and the divided crystal frequency. A charge pump circuit (which controls pins CP, FB) and an external transistor (to buffer the L64733 against the tuning voltage of 28 V) generate the current. The current is filtered, fed through a discrete loop filter, and converted to a tuning voltage that drives the external varactor diodes for the VCO tank circuit. A complete frequency controlled loop is formed, and the VCO frequency can be varied by changing the frequency divider ratios in the L64734 registers. See Figure 7 on page 22 for more details regarding the external circuitry for the VCO, crystal oscillator, charge pump, tank circuitry, and entire frequency-controlled loop.

The chipset provides maximum integration and flexibility for system designers at a minimum cost. The number of external components required to build a system is minimal because the synthesizer, variable rate filters, and clock and carrier loops are all integrated into the two devices.

#### **Features and Benefits**

## **System Features**

- Direct down-conversion

- Integrated programmable cut-off low-pass filters for variable-rate operation

- Dual AGC for optimizing performance with respect to intermodulation and noise

- Integrated synthesizer

- Integrated quadrature amplitude and phase imbalance compensation

- RF loop-through

### **Chipset Features**

- Supports DVB and DSS system specifications

- BPSK/QPSK demodulation rates from 1 to 45 Mbaud

- Matched filter (square root raised cosine filter with roll-off factor of 20% or 35%)

- Anti-aliasing filters for operation from 1 to 45 Mbaud without switching external SAW filters or the need for low-pass filters

- On-chip digital clock synchronization

- On-chip digital carrier synchronization, featuring a frequency sweep capability for signal acquisition

- Auto-acquisition demodulator mode and tuner control through an on-chip microcontroller

- Integrated Phase-Locked Loop (PLL) for clock synthesis, allowing the use of a fundamental mode crystal

- Fast channel switching mode

- Power estimation for AGC control

- Programmable Viterbi decoder module for rates 1/2, 2/3, 3/4, 5/6, 6/7, 7/8

- Reed-Solomon decoder (204/188), (146/130)

- Auto-synchronization for Viterbi decoder

L64733/L64734 Tuner and Satellite Receiver Chipset

6

- Programmable synchronization for deinterleaver, Reed-Solomon decoder, and descrambler

- Bit error monitoring for channel performance measurements

- Deinterleaver (DVB and DSS)

- Serial host interface compatible with the LSI Logic Serial Control bus interface

- Power-down mode

- On-chip dual differential 6-bit ADCs

- Supports Synchronous Parallel Interface protocol for FEC data output

## **Chipset Interconnections**

Figure 4 shows the interconnections between the L64733 and L64734.

L64733 L64734 **PLLINp PLLINp** PLLINn PLLINn MODp MODp MODn MODn **FDOUB FDOUB** FLCLK **FLCLK** Control Control Signals Signals **INSEL INSEL** AGC1 AGC1 AGC2 AGC2 CPG1 XCTR[0] CPG2 XCTR[1] **XTLOUT XOIN PSOUTp PSOUTp** Prescaler Prescaler Signals Signals **PSOUTn PSOUTn IOUTp IVINp IOUT**n IVINn Channel Data Channel Data Signals Signals QOUTp QVINp QOUTn QVINn

Figure 4 Chipset Interconnection Diagram

# L64733 Signal Descriptions

This section describes the L64733 signals. Figure 5 shows the interface diagram of the L64733. Names of signals that are active-LOW are designated with an "n" suffix (for example, ERROROUTn). Names of differential signals are designated with a "p" suffix for the noninverting side (for example, QOUTp), and with an "n" suffix for the inverting side (for example, QOUTn).

RFINn AGC1 AGC2 RFINp Signals CPG1 **RFOUT** CPG2 **FDOUB** XTLn **FLCLK CFLT TANKn IDCn** Oscillator Control **TANK**p **IDCp** Signals Signals VRLO **INSEL** XTLp MODn XTLOUT MODp **IOUT**n PLLINn **IOUT**p **PLLINp** Channel Data Signals QOUTn QDCn QOUTp QDCp Prescaler **PSOUTn** CP Charge Pump Signals **PSOUT**p FΒ Signals

Figure 5 L64733 Interface Diagram

As shown in Figure 5, the L64733 has the following major interfaces:

- RF

- Oscillator

- Control

- Channel Data

- Prescaler

- Charge Pump

L64733/L64734 Tuner and Satellite Receiver Chipset

The following signal descriptions are listed according to the major interface groups. Within each group, the signals are described in alphabetic order.

## **RF Signals**

The L64733 can accept an RF input signal and loop it through to RFOUT. This is controlled by an on-chip RF switch.

#### RFINn, RFINp RF Input

Input

The RFIN differential signals form the 75  $\Omega$  input. Connect the RFINp signal through a series 100 pF capacitor to a 75  $\Omega$  F video connector and the RFINn signal through a series 75  $\Omega$  resistor and 100 pF capacitor to ground.

#### **RFOUT RF Output**

**Output**

The RFOUT signal is a 75  $\Omega$  output that is active when the INSEL input is deasserted. When active, the signal at RFOUT is a copy of the RFIN signal.

## **Oscillator Signals**

The L64733 has two internal oscillators: a crystal oscillator and a tank oscillator.

#### **CFLT Bias Voltage Bypass**

**Bidirectional**

See Figure 7 on page 22 for information on how to connect the CFLT pin.

#### TANKn, TANKp

**Oscillator Tank Port**

Input

See Figure 7 on page 22 for information on how to

connect the TANKp and TANKn pins.

**VRLO Local Oscillator Regulator Bypass** Bidirectional

See Figure 7 on page 22 for information on how to

connect the VRLO pin.

#### XTLn, XTLp **Crystal Oscillator Port**

Connect the XTLp and XTLn pins as shown in Figure 7 on page 22.

#### XTLOUT Crystal Out

Output

This signal provides a buffered clock reference frequency for driving the L64734 XOIN pin.

## **Control Signals**

The following signals, some of which are generated by the L64734 IC, control the mode of operation of the L64733 IC.

#### AGC1 Automatic Gain Control 1

Input

The AGC1 signal is a high-impedance input from the L64734; it controls the RF AGC circuitry. The AGC1 voltage range is from 0.5 V to 4.8 V.

#### AGC2 Automatic Gain Control 2

Input

The AGC2 signal is a high-impedance input from the L64734; it controls RF AGC circuitry.

#### CPG[2:1] Charge Pump Gain

Input

The CPG[2:1] signals set the charge pump gain according to the following table.

#### Charge Pump Current (typ), mA

| CPG1 | CPG2 | FB HIGH | FB LOW |

|------|------|---------|--------|

| 0    | 0    | 0.1     | -0.1   |

| 0    | 1    | 0.3     | -0.3   |

| 1    | 0    | 0.6     | -0.6   |

| 1    | 1    | 1.8     | -1.8   |

#### FDOUB Frequency Doubler

Input

When the FDOUB signal is asserted, the L64733 local oscillator frequency is internally doubled and fed to the mixers. When the FDOUB signal is deasserted, the oscillator frequency is not doubled before being fed to the mixers.

#### FLCLK Filter Clock

Input

The FLCLK signal is a low-amplitude, self-biased clock input. The frequency of the FLCLK signal multiplied by 16 is the baseband filter's –3 dB frequency.

#### IDCn, IDCp

#### **I-Channel DC Offset Correction**

Input

Connect a 0.1  $\mu\text{F}$  (or larger) capacitor between the IDCp and IDCn signals.

#### INSEL RF Port Input Select

Input

When the INSEL signal is asserted, the L64733 is in normal mode. When the INSEL signal is deasserted, the L64733 is in Loop-Through mode. In this mode, the RFIN signal is looped through to the RFOUT signal, and the L64733 local oscillator is shut off.

#### MODn, MODp Prescaler Modulus

Input

The MOD differential signals form a PECL input that sets the prescaler modulus. When the MODp signal is positive with respect to the MODn signal, the prescaler modulus is set to 32 (divide by 32). When the MODn signal is positive with respect to the MODp signal, the prescaler modulus is set to 33 (divide by 33).

#### PLLINn, PLLINp

#### **Phase Detector**

Input

The PLLIN differential signals form the phase detector input and are connected to the L64734 PLLINp and PLLINn output signals. See the L64734 PLLINp and PLLINn descriptions in the subsection entitled "Synthesizer Control Interface" on page 19.

#### QDCn, QDCp Q-Channel DC Offset Correction

Input

Connect a 0.1  $\mu F$  (or larger) capacitor between the QDCp and QDCn signals.

#### **Channel Data Signals**

This section describes the channel data signals from the L64733 to the L64734.

#### IOUTn, IOUTp I-Channel Baseband Data

Output

The IOUT differential signals form the in-phase data provided to the L64734.

#### QOUTn, QOUTp

#### **Q-Channel Baseband Data**

Output

The QOUT differential signals form the quadrature-phase data provided to the L64734.

## **Prescaler Signals**

The following signals are the prescaler outputs from the L64733 to the L64734.

#### PSOUTn, PSOUTp

Prescaler Output These differential signals are the L64733 prescaler outputs. The programmable counters on the L64734 are clocked on the rising edge of the PSOUT signal.

## **Charge Pump Signals**

The following signals are outputs from the L64733 charge pump.

| CP | Charge Pump Connect the CP signal as shown in Figure 7 on page 22.                                  |  |

|----|-----------------------------------------------------------------------------------------------------|--|

| FB | Feedback Charge Pump Transistor Drive Output Connect the FB signal as shown in Figure 7 on page 22. |  |

# L64734 Signal Descriptions

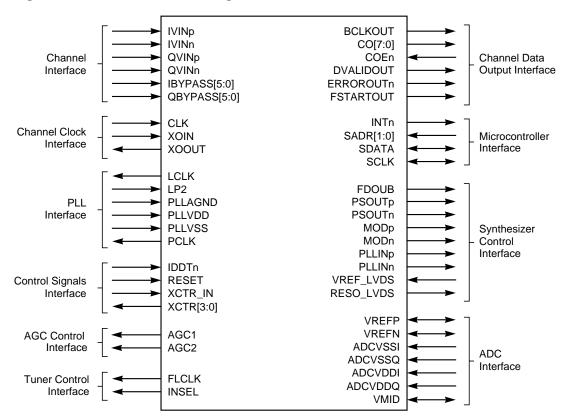

This section provides detailed information on the L64734 signals. Figure 6 shows the interface diagram of the L64734.

Figure 6 L64734 Interface Diagram

As shown in Figure 6, the L64734 has the following major interfaces:

- Channel

- Channel Clock

- PLL

- Control Signals

- ADC

- AGC Control

- Channel Data Output

- Microcontroller

- Synthesizer Control

- Tuner Control

The following signal descriptions are listed according to the major interface groups.

#### **Channel Interface**

The Channel Interface is the input path to the L64734 satellite receiver. IVIN and QVIN are the I and Q streams, respectively, from the satellite tuner circuit. The CLK signal strobes in the data signals.

#### IBYPASS[5:0] I Channel Data

Input

The IBYPASS[5:0] signals form the digital I channel data input bus, which supplies the I Stream to the L64734 when the ADC is bypassed. Bypass is controlled through the setting of particular register bits in the L64734.

#### IVINn, IVINp I Channel Data

Input

These differential signals form the analog received I channel data input bus, which supplies the I stream to the L64734.

#### QBYPASS[5:0]

#### **Q** Channel Data

Input

The QBYPASS[5:0] signals form the digital received Q channel data input bus, which supplies the Q Stream to the L64734 when the ADC is bypassed. Bypass is controlled through the setting of particular register bits in the L64734.

#### QVINn, QVINp

#### **Q** Channel Data

Input

The QVINn and QVINp differential signals form the analog received Q channel data input bus, which supplies the Q stream to the L64734.

#### **Channel Clock Interface**

The Channel Clock Interface consists of the clock and crystal oscillator signals.

CLK Input Clock Input

This functionality has been assigned to the XOIN pin.

**XOIN** Crystal Oscillator In Input

The XOIN pin is used for a crystal oscillator or external reference clock input. A 15 MHz crystal is normally connected to the XOIN pin. This pin can also be driven by the XOOUT pin from L64733. When using an external ADC to strobe bypass data into the L64734, connect the

clock input to this pin.

**XOOUT Crystal Oscillator Out** Output

This is the crystal oscillator output pin.

## Phase-Locked Loop (PLL) Interface

The internal PLL generates the signals to operate the ADC, demodulator, and FEC modules.

#### **LCLK Decimated Clock Output** Output

The L64734 internal clock generation module generates the LCLK signal. LCLK is derived by dividing CLK by the value of the CLK\_DIV2 register parameter.

LP2 Input to VCO Input

> The LP2 signal is the input to the internal voltagecontrolled oscillator. It is normally connected to the output of an external RC filter circuit.

**PCLK PLL Clock Output** Output

> The L64734 internal PLL clock synthesis module generates the PCLK signal. The PLL is driven by the reference crystal connected between the XOIN and XOOUT pins. The PLL clock synthesis module can be configured to generate a PCLK rate that is appropriate for

all data rates.

**PLLAGND PLL Analog Ground** Input

> PLLAGND is the analog ground pin for the PLL module; it is normally connected to the system ground plane.

PLLVDD PLL Power Input

PLLVDD is the power supply pin for the PLL module; it is normally connected to the system power  $(V_{DD})$  plane.

PLLVSS PLL Ground Input

PLLVSS is the ground pin for the PLL module; it is normally connected to the system ground plane.

### **Control Signals Interface**

The Control Signals interface controls the operation of the L64734; it is not associated with any particular interface.

IDDTn Test Input

The IDDTn pin is an LSI Logic internal test pin. Tie the IDDTn pin LOW for normal operation.

RESET Reset Input

This active-HIGH signal resets all internal data paths. Reset timing is asynchronous to the device clocks. Reset does not affect the configuration registers.

XCTR\_IN Control Input Input

The XCTR\_IN pin is an external input control pin. It is sensed by reading the XCTR IN register bit.

XCTR[3] Control Output/Sync Status Flag Output

This signal indicates the synchronization status for one of three synchronization modules in the L64734 or the XCTR[3] field in Group 4, APR 55. The modules are the Viterbi decoder, Reed-Solomon deinterleaver (DI/RS), and descrambler. For any of the three synchronization outputs, asserting the XCTR[3] signal indicates that synchronization has been achieved for the sync module chosen using the SSS[1:0] register bits. When deasserted, the signal indicates an out-of-synchronization condition.

XCTR[2:0] Control Output Output

The XCTR[2:0] pins are external output control pins. They are set by programming particular register bits. XCTR[2] is mapped to CPG1, and XCTR[0] is multiplexed with CPG2, when used with the L64733 Tuner IC. When the on-chip serializer is used to generate a serial 2- or 3-wire protocol on the XCTR[2:0] pins, the mapping is XCTR[2] = EN, XCTR[1] = SCL, and XCTR[0] = SDA.

## Analog-to-Digital Converter (ADC) Interface

The ADC module converts the incoming IVIN and QVIN signals into an internal 6-bit digital representation for processing. The following pins support the ADC module.

ADCVDDI/Q ADC Power Input

These are the analog power supply pins for the ADC module; they are normally connected to the system

power (V<sub>DD</sub>) plane.

ADCVSSI/Q ADC Analog Ground Input

These are the analog ground pins for the ADC module; they are normally connected to the system ground plane.

VREFP Reference Voltage, Positive Input/Output

ADC reference voltage generated by the on-chip bandgap-based generator. Bypass to GND using a

0.1 μF capacitor.

VREFN Reference Voltage, Negative Input/Output

ADC reference voltage generated by the on-chip bandgap-based generator. Bypass to GND using a

0.1 μF capacitor.

VMID Reference Voltage, Middle Input/Output

ADC reference voltage generated by the on-chip bandgap-based generator. Bypass to GND using a

0.1 μF capacitor.

#### **AGC Control Interface**

The AGC Control interface contains signals used for power control.

#### AGC1, AGC2 Power Control Signals Output

The AGC1 and AGC2 signals are the positive  $\Sigma\Delta$  modulated output used for power control. These signals can each drive an external passive RC filter that feeds a gain control stage for dual-stage AGC. For a single-stage AGC, AGC1 can be used.

## **Channel Data Output Interface**

The Channel Data Output interface is the output path from the L64734. It is typically connected to the input of the transport demultiplexer in a set-top decoder application.

#### BCLKOUT

#### **Byte Clock Out**

Output

This signal indicates valid data bytes on the CO[7:0] bus when the L64734 is in Parallel Channel Output mode. This signal cycles once every valid output data byte. It is used by the transport demultiplexer to latch output data from the L64734 at the BCLKOUT rate. Disregard the BCLKOUT signal when the L64734 is in Serial Channel Output mode.

#### CO[7:0] Channel Data Out

Output

The CO[7:0] signals form the decoded output data port. When the OF bit is 1 (Group 4, APR17), the L64734 operates in the Parallel Channel Output mode. In this mode, the L64734 outputs the channel data as eight-bit-wide parallel data on the CO[7:0] signals. In Serial Channel Output mode (OF = 0), the L64734 outputs the channel data as serial data on CO[0]. The data is latched on every bit clock cycle. The chronological ordering in Serial Channel output mode is: MSB oldest, LSB newest.

#### **COEn**

#### **Channel Output Enable**

Input

When asserted, the COEn signal enables the ERROROUTn, CO[7:0], DVALIDOUT, BCLKOUT, and FSTARTOUT signals. Operation of the receiver continues regardless of the state of the COEn signal.

#### **DVALIDOUT**

#### **Valid Data Out**

Output

The DVALIDOUT signal indicates that the CO[7:0] signals contain the corrected channel data. New data is valid on the CO[7:0] signals when the DVALIDOUT signal is asserted. DVALIDOUT is not asserted during the propagated check and GAP bytes. The DVALIDOUT signal is deasserted after the FEC\_RST register bit (Group 4, APR 55) is set to 1.

#### **ERROROUTn Error Detection Flag**

Output

The L64734 asserts the ERROROUTn signal at the beginning of any frame that contains an uncorrectable error; it deasserts ERROROUTn at the end of the frame

if the error condition is removed. The ERROROUTn signal is exactly aligned with the output data stream; it is asserted after the FEC\_RST register bit is set.

#### **FSTARTOUT** Frame Start Output

Output

The L64734 asserts the FSTARTOUT signal during the first bit of every frame with valid data in Serial Channel output mode, and during the first byte in Parallel Channel output mode. FSTARTOUT is valid only when the DVALIDOUT signal is asserted. The FSTARTOUT signal is deasserted after the FEC\_RST register bit is set.

#### Microcontroller Interface

The Microcontroller interface connects the L64734 to an external microcontroller.

INTn Interrupt Output

The L64734 asserts INTn when an internal, unmasked interrupt flag is set. The INTn signal remains asserted as long as the interrupt condition persists and the interrupt

flag is not masked.

SADR[1:0] Serial Address Input

The SADR[1:0] signals are the two programmable bits of

the serial address for the L64734.

SCLK Serial Clock Bidirectional

This is the serial clock pin for a two-wire serial protocol.

SDATA Serial Data Bidirectional

This is the serial data pin for a two-wire serial protocol.

#### **Synthesizer Control Interface**

The Synthesizer Control interface lets the L64734 control the L64733 frequency synthesizer.

#### FDOUB Frequency Doubler Output

When FDOUB is asserted, the frequency doubler on the L64733 Tuner IC is enabled. When FDOUB is deasserted, the frequency doubler is disabled. This output is set by register programming.

#### **MODn, MODp Modulus Selector**

Output

These signals are low-voltage differential signals from the L64734 modulus selector programmable counter (A). The signals are clocked by PSOUT. A positive MODp with respect to MODn selects a divide by 32 at the dual modulus prescaler on the L64733 Tuner IC. A negative MODp with respect to MODn selects a divide by 33. Counter A can be programmed to count down from a particular value by register bit programming.

#### PLLINn, PLLINp

#### **PLL Differential Counter M**

Output

These signals are low-voltage differential signals from the L64734 programmable synthesizer counter (M). The signals are clocked by PSOUT. PLLINp is positive with respect to PLLINn for one PSOUT cycle. The repetition rate is 0.5 MHz for a 4 MHz reference crystal. The counter M can be programmed to count down from a particular value by register bit programming.

#### PSOUTn, PSOUTp

#### **Prescaler Output**

Output

These signals are differential signals to the L64734 from the L64733. The programmable counters on the L64734 are clocked on the rising edge of the PSOUT signal.

#### **RESO LVDS LVDS Buffers Precision Resistor**

Output

The RESO\_LVDS output must be connected to a resistor (6.8 k $\Omega$  ±5%) that controls the swing of the LVDSOUT buffers used to drive the differential signals MODp, MODn, and PLLINp, PLLINn. Connect the other side of the resistor to ground.

#### VREF\_LVDS LVDS Buffers Reference Voltage

Input

The VREF\_LVDS input is a 1.2 V ±10% voltage level that controls the common mode voltage of the LVDSOUT buffers used to drive the differential signals MODp, MODn, and PLLINp, PLLINn.

#### **Tuner Control Interface**

The Tuner Control interface contains signals that control the L64733 Tuner IC.

FLCLK Filter Control Clock Output

FLCLK is the output of a programmable integer value divider clocked by the demodulator sampling clock, PCLK. The division ratio can be programmed with register bits. The frequency of FLCLK multiplied by 16 is the 3 dB cutoff of the programmable low-pass filters on

the L64733.

INSEL RF Input Select Output

When INSEL is asserted, the L64733 tuner selects the normal mode. When INSEL is deasserted, the L64733

selects the Loop-Through mode.

## **Typical Operating Circuit**

Figure 7 is a diagram of a typical operating circuit for the chipset, including external components. Not all external components are shown. See the *L64733/34 Evaluation Board User's Guide* for complete schematic details.

# **Specifications**

This section contains the electrical, timing, and mechanical specifications for the L64733/34 chipset.

## L64733 Electrical Specifications

This section contains the electrical parameters for the L64733. Table 1 lists the absolute maximum values. Exceeding the values listed can cause damage to the L64733. Table 2 gives the recommended operating supply voltage and temperature. Table 3 gives the DC characteristics. Table 4 gives the AC characteristics. Table 5 summarizes the pins.

Table 1 L64733 Absolute Maximum Rating (Referenced to V<sub>SS</sub>)

| Symbol          | Parameter                                           | Limits <sup>1</sup> | Units   |

|-----------------|-----------------------------------------------------|---------------------|---------|

| V <sub>CC</sub> | DC Supply Voltage                                   | -0.5 to +7.0        | V       |

| _               | Continuous power dissipation up to +70 °C           | 1.05                | W       |

| _               | Derating above +70 °C                               | 2                   | mW/°C   |

| _               | Operating temperature                               | 0 to +70            | °C      |

| _               | Junction temperature                                | +150                | °C      |

| _               | Storage Temperature                                 | -65 to +165         | °C      |

| Θ <sub>ja</sub> | Junction to Ambient Thermal Resistance <sup>2</sup> | 27.6                | °C/watt |

| _               | Lead temperature (soldering 10 sec)                 | +300                | °C      |

Note that the ratings in this table are those beyond which permanent device damage is likely to occur. Do not use these values as the limits for normal device operation.

<sup>2.</sup> The junction to ambient thermal resistance is for the ePad TQFP package, for a four-layer board.

Table 2 Recommended Operating Conditions

| Symbol         | Parameter                                        | Limits <sup>1</sup> | Units |

|----------------|--------------------------------------------------|---------------------|-------|

| $V_{DD}$       | DC Supply Voltage                                | 5 ± 5%              | ٧     |

| T <sub>A</sub> | Operating Ambient Temperature Range (Commercial) | 70                  | °C    |

For normal device operation, adhere to the limits in this table. Sustained operation of a device at conditions exceeding these values, even if they are within the absolute maximum rating limits, can result in permanent device damage or impaired device reliability. Device functionality to stated DC and AC limits is not guaranteed if recommended operating conditions are exceeded.

Table 3 DC Characteristics of the L64733<sup>1</sup>

| Parameter                                                      | Condition                                                                                           | Min  | Тур | Max  | Units |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Power Supply                                                   |                                                                                                     |      |     |      |       |

| Power Supply Voltage                                           | All DC specs met                                                                                    | 4.75 | 5.0 | 5.25 | V     |

| Power Supply Current                                           |                                                                                                     | _    | 190 | 220  | mA    |

| Digital Control Inputs - CPG                                   | 1, CPG2, INSEL, FDOUB                                                                               |      |     |      |       |

| Input Logic Level HIGH                                         |                                                                                                     | 2.4  | _   | -    | V     |

| Input Logic Level LOW                                          |                                                                                                     | 0    | _   | 0.5  | V     |

| Input Bias Current                                             | Pin at 2.4 V                                                                                        | -15  | _   | 10   | μΑ    |

| Slew-Limited Digital Clock II                                  | nputs - FLCLK                                                                                       | •    |     |      | •     |

| FLCLK Input Level LOW                                          |                                                                                                     | _    | _   | 1.45 | V     |

| FLCLK Input Level HIGH                                         |                                                                                                     | 1.85 | _   | _    | V     |

| FLCLK Input<br>Resistance/Leakage<br>Current                   | 50 K series resistor between L64734 and FLCLK pin. L64734 generates normal CMOS levels              | -1   | _   | 1    | μА    |

| Fast Digital Clock Inputs - N                                  | MODp, MODn, PLLINp, PLLINn                                                                          | •    | •   |      | '     |

| MODp, MODn, PLLINp,<br>PLLINn Common Mode Input<br>Range (VCM) |                                                                                                     | 1.08 | 1.2 | 1.32 | V     |

| MODp, MODn, PLLINp,<br>PLLINn Input Voltage LOW                | MODp, MODn, or PLLINp, PLLINn differential swing around VCM. Need external 100 $\Omega$ termination | _    | _   | -100 | mV    |

| (Sheet 1 of 3)                                                 |                                                                                                     |      |     |      |       |

Table 3 DC Characteristics of the L64733<sup>1</sup> (Cont.)

| Parameter                                             | Condition                                                                                           | Min   | Тур  | Max   | Units |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| MODp, MODn, PLLINp,<br>PLLINn Input Voltage HIGH      | MODp, MODn, or PLLINp, PLLINn differential swing around VCM. Need external 100 $\Omega$ termination | 100   | _    | -     | mV    |

| MODp, MODn, PLLINp,<br>PLLINn Input Current           | MODp, MODn, PLLINp, PLLINn                                                                          | -5    | _    | +5    | μА    |

| Digital Clock Outputs - PSC                           | UTp, PSOUTn                                                                                         |       |      |       | •     |

| PSOUTp, PSOUTn Common<br>Mode Output Range (VCM)      |                                                                                                     | 2.16  | 2.4  | 2.64  | V     |

| PSOUTp, PSOUTn Output<br>Voltage LOW                  | PSOUTp, PSOUTn differential swing around VCM. Driving LSI PECL Load (±10 µA)                        | -     | -215 | -150  | mV    |

| PSOUTp, PSOUTn Output<br>Voltage HIGH                 | PSOUTp, PSOUTn differential swing around VCM. Driving LSI PECL Load (±10 µA)                        | 150   | 215  | -     | mV    |

| Synthesizer                                           |                                                                                                     |       |      |       | •     |

| Prescaler Ratio                                       | MOD = HIGH                                                                                          | 32    | _    | 32    | _     |

|                                                       | MOD = LOW                                                                                           | 33    | _    | 33    | _     |

| Reference Divider Ratio                               |                                                                                                     | 8     | _    | 8     | _     |

| Charge Pump Output HIGH                               | CPG1, CPG2 = 0, 0                                                                                   | 0.08  | 0.1  | 0.12  | mA    |

| Current (at FB)                                       | CPG1, CPG2 = 0, 1                                                                                   | 0.24  | 0.3  | 0.36  | mA    |

|                                                       | CPG1, CPG2 = 1, 0                                                                                   | 0.48  | 0.6  | 0.72  | mA    |

|                                                       | CPG1, CPG2 = 1, 1                                                                                   | 1.44  | 1.8  | 2.16  | mA    |

| Charge Pump Output LOW                                | CPG1, CPG2 = 0, 0                                                                                   | -0.12 | -0.1 | -0.08 | mA    |

| Current (at FB)                                       | CPG1, CPG2 = 0, 1                                                                                   | -0.36 | -0.3 | -0.24 | mA    |

|                                                       | CPG1, CPG2 = 1, 0                                                                                   | -0.72 | -0.6 | -0.48 | mA    |

|                                                       | CPG1, CPG2 = 1, 1                                                                                   | -2.16 | -1.8 | -1.44 | mA    |

| Charge Pump Output<br>Leakage Current                 |                                                                                                     | -25   | -    | 25    | nA    |

| Charge Pump Positive-to-<br>Negative Current Matching | FB self-biased                                                                                      | -5    | -    | 5     | %     |

| (Sheet 2 of 3)                                        |                                                                                                     |       |      |       |       |

Table 3 DC Characteristics of the L64733<sup>1</sup> (Cont.)

| Parameter                                            | Condition                                                          | Min  | Тур | Max  | Units           |

|------------------------------------------------------|--------------------------------------------------------------------|------|-----|------|-----------------|

| Charge Pump Output<br>Transistor Base Current Drive  |                                                                    | 100  | _   | -    | μА              |

| Analog Control Inputs - AGO                          | C1, AGC2                                                           |      |     |      |                 |

| Input Bias Current                                   | 1 V < Pin < 4 V                                                    | -50  | _   | 50   | μΑ              |

| Baseband Outputs - IOUTp,                            | IOUTn, QOUTp, QOUTn                                                |      |     |      |                 |

| Output Swing                                         | Loaded with 2 K differential across IOUTp, IOUTn, and QOUTp, QOUTn | 1    | _   | -    | V <sub>PP</sub> |

| IOUTp, IOUTn, QOUTp,<br>QOUTn Common<br>Mode Voltage |                                                                    | 0.65 | _   | 0.85 | V               |

| IOUTp, IOUTn, QOUTp,<br>QOUTn DC Offset Voltage      |                                                                    | -50  | _   | 50   | mV              |

| (Sheet 3 of 3)                                       |                                                                    |      |     |      |                 |

<sup>1.</sup> For symbol rates below 15 MSymbols/s, the maximum input power might be subject to shifting down by roughly 10 \* log(15/Rs[MSymbols/s]) dB due to channel bandwidth reduction.

Table 4 AC Characteristics of the L64733

| Parameter                                                            | Condition                                                                                                                                                             |                                    | Min         | Тур               | Max              | Units             |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|-------------------|------------------|-------------------|

| RF Front End                                                         |                                                                                                                                                                       |                                    |             |                   | !                | !                 |

| RFIN Input Frequency<br>Range                                        | Meets all following AC sp                                                                                                                                             | ecs                                | 925         | _                 | 2175             | MHz               |

| RFIN Single-Carrier<br>Input Power                                   | RF level needed to produ                                                                                                                                              | ıce 0.59 V <sub>PP</sub>           | -65         | -                 | -25 <sup>1</sup> | dBm               |

| AGC1 Range                                                           | 1 V < AGC1 < 4 V                                                                                                                                                      |                                    | 50          | _                 | _                | dB                |

| AGC2 Range                                                           | 1 V < AGC2 < 4 V                                                                                                                                                      |                                    | 19          | _                 | _                | dB                |

| RFIN referred IP3 (front-end contributions)                          | AGC1 gain set for  -25 dBm input level (0.59 V <sub>PP</sub> output), and AGC2 set to maximum gain (V <sub>AGC2</sub> = 1 V). 2 signals at FLO + 32 MHz, FLO + 72 MHz | @2175 MHz<br>@1550 MHz<br>@925 MHz | _<br>_<br>_ | 3<br>7<br>8       | -<br>-<br>-      | dBm<br>dBm<br>dBm |

| Baseband 1 dB<br>Compression Point                                   | IOUTp, IOUTn, QOUTp,<br>1 signal within filter BW                                                                                                                     | QOUTn have                         | 2           | _                 | _                | V <sub>PP</sub>   |

| RFIN Referred IP2                                                    | PRFIN = $-25 \text{ dBm}, F_{LO} =$                                                                                                                                   | = 951 MHz                          | _           | 15.5              | _                | dBm               |

| Noise Figure                                                         | At maximum gain AGC1,                                                                                                                                                 | AGC2                               | _           | 11.5              | _                | dB                |

| RFIN Worst Case<br>Return Loss                                       | Complex "75 Ω source" s board, connector parasiti                                                                                                                     | •                                  | -           | 11                | _                | dB                |

| LO Leakage Power at RFIN                                             | 950 MHz to 2150 MHz, s<br>board layout                                                                                                                                | subject to                         | _           | -65               | _                | dBm               |

| Second Harmonic<br>Rejection                                         | Due to LO-generated 2nd                                                                                                                                               | d harmonic                         | 27          | -                 | _                | dB                |

| Half-Harmonic Rejection and x 1.5 Harmonic Rejection <sup>1, 2</sup> | Due to RFIN-generated 2nd harmonic                                                                                                                                    |                                    | _           | 27                | _                | dB                |

| Loop Through                                                         | •                                                                                                                                                                     |                                    | . '         |                   | •                | •                 |

| Gain                                                                 |                                                                                                                                                                       | @2175 MHz<br>@1550 MHz<br>@925 MHz | -           | 2.5<br>1.8<br>0.8 | _                | dB                |

| (Sheet 1 of 3)                                                       | 1                                                                                                                                                                     | !                                  |             |                   |                  |                   |

Table 4 AC Characteristics of the L64733 (Cont.)

| Parameter                                                          | Condition                                                                              |                                    | Min         | Тур                              | Max       | Units           |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|-------------|----------------------------------|-----------|-----------------|

| RFIN referred IP3<br>(when Loop-Through<br>enabled)                | At PRFIN = -25 dBm                                                                     | @2175 MHz<br>@1550 MHz<br>@925 MHz | _           | 5<br>7<br>9                      | _         | dBm             |

| Noise Figure                                                       |                                                                                        |                                    | _           | 12.0                             | _         | dB              |

| Worst-Case Return Loss                                             | Subject to board and corparasitics                                                     | nector                             | -           | 8                                | -         | dB              |

| Baseband                                                           |                                                                                        |                                    |             |                                  |           |                 |

| IOUTp, IOUTn, QOUTp,<br>QOUTn Differential<br>Output Voltage Swing | $2~\text{k}\Omega$ differential load, IO QOUTp, QOUTn. Expect each pin to GND          | UTp, IOUTn,<br>20 pF from          | 1           | -                                | _         | V <sub>PP</sub> |

| IOUTp, IOUTn, QOUTp,<br>QOUTn Output<br>Impedance                  | Per side, IOUTp, IOUTn,<br>QOUTn. To 200 MHz                                           | QOUTp,                             | _           | -                                | 50        | Ωs              |

| Baseband Highpass  -3 dB Point                                     | 0.22 μF caps connected IDCn, and QDCp to QDC                                           |                                    | -           | -                                | 750       | Hz              |

| LPF Nominal Cutoff Frequency Range                                 | Fc is -3 dB point of filter                                                            |                                    | 8           | -                                | 33        | MHz             |

| LPF Nominal Fc                                                     |                                                                                        |                                    | _           | 14.5 ·<br>F <sub>FLCLK</sub> + 1 | _         | _               |

| Baseband Frequency<br>Response                                     | Deviation from ideal 7th-oworth, measure to F - 3 of Include front-end tilt effective. | dB x 0.7.                          | -0.5        | -                                | 0.5       | dB              |

| LPF Cutoff Frequency<br>Accuracy                                   | Measured –3 dB point                                                                   | @8 MHz<br>@31.4 MHz                | -5.5<br>-10 | -<br>-                           | 5.5<br>10 | %<br>%          |

| Quadrature Gain Error                                              | Includes effects from bas                                                              | eband filters                      | _           | -                                | 1.2       | dB              |

| Quadrature Phase Error                                             | Measure at 125 kHz                                                                     |                                    | _           | _                                | 4         | Deg             |

| Synthesizer                                                        |                                                                                        |                                    |             |                                  | •         |                 |

| Crystal Frequency Range                                            |                                                                                        |                                    | 4           | _                                | 7.26      | MHz             |

| XTLOUT Voltage Levels                                              | Measured on 10 pF // 1                                                                 | ΜΩ                                 | 0.8         | 1.0                              | 1.3       | V <sub>PP</sub> |

| XTLOUT DC Level                                                    |                                                                                        |                                    | _           | 2.0                              | _         | V               |

| (Sheet 2 of 3)                                                     |                                                                                        |                                    |             |                                  |           |                 |

Table 4 AC Characteristics of the L64733 (Cont.)

| Parameter                                                            | Condition                                                                                                                                                               | Min | Тур             | Max  | Units      |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------|------------|

| MODp, MODn Delay                                                     | Must assert MOD level within this time period to ensure that the next PSOUT period gives correct count. Delay is with respect to rising edge of PSOUT (previous count). | _   | -               | 8.5  | ns         |

| PLLINp, PLLINn and MODp, MODn Hold Time                              | With respect to rising edge of PSOUT. This means that PSOUT need not continue to be asserted after MOD has given correct count.                                         | 0   | -               | _    | ns         |

| Local Oscillator                                                     |                                                                                                                                                                         |     |                 |      | 1          |

| LO Tuning Range                                                      |                                                                                                                                                                         | 543 | _               | 1180 | MHz        |

| LO Phase Noise, Including Doubler. Subject to                        | 1 kHz offset. Depends on PLL loop gain.                                                                                                                                 | 1   | <b>–</b> 55     | _    | dBc/<br>Hz |

| LC tank implementation.                                              | 10 kHz offset. Depends on PLL loop gain.                                                                                                                                | -   | <del>-</del> 75 | _    | dBc/<br>Hz |

|                                                                      | 100 kHz offset                                                                                                                                                          | -   | <b>-95</b>      | _    | dBc/<br>Hz |

| LO Buffer Frequency<br>Range when overdriven<br>by external LO       | FDOUB = LOW                                                                                                                                                             | 925 | -               | 2175 | MHz        |

| LO Input Port VSWR<br>Over Band, when over-<br>driven by external LO | 925 MHz < FLO < 2175 MHz. Assume series resistors to TANKp and TANKn pins                                                                                               | _   | -               | 2:1  | _          |

| Required external LO Input Power Range                               | Differential drive into TANKp, TANKn. 50 $\Omega$ source.                                                                                                               | -15 | -               | -5   | dBm        |

| (Sheet 3 of 3)                                                       |                                                                                                                                                                         |     |                 | •    |            |

x 1.5 harmonic rejection for FLO = 725 MHz.

The L63733 is available with the half-harmonic specification guaranteed to 38 dB typical. Contact your LSI Logic sales representative for further information.

Table 5 L64733 Pin Description Summary

| Mnemonic      | Description                                   | Туре          |

|---------------|-----------------------------------------------|---------------|

| AGC1          | Automatic Gain Control 1                      | Input         |

| AGC2          | Automatic Gain Control 2                      | Input         |

| CFLT          | Bias Voltage Bypass                           | Bidirectional |

| СР            | Charge Pump                                   | Output        |

| CPG[2:1]      | Charge Pump Gain                              | Input         |

| FB            | Feedback Charge Pump Transistor Drive         | Output        |

| FDOUB         | Frequency Doubler                             | Input         |

| FLCLK         | Filter Clock                                  | Input         |

| IDCp          | I-Channel DC Offset Correction (noninverting) | Input         |

| IDCn          | I-Channel DC Offset Correction (inverting)    | Input         |

| INSEL         | RF Port Input Select                          | Input         |

| IOUTp         | I-Channel Baseband Data (noninverting)        | Output        |

| IOUTn         | I-Channel Baseband Data (inverting)           | Output        |

| MODp          | Prescaler Modulus (noninverting)              | Input         |

| MODn          | Prescaler Modulus (inverting)                 | Input         |

| PLLINp        | Phase Detector (noninverting)                 | Input         |

| PLLINn        | Phase Detector (inverting)                    | Input         |

| PSOUTp        | Prescaler (noninverting)                      | Output        |

| PSOUTn        | Prescaler (inverting)                         | Output        |

| QDCp          | Q-Channel DC Offset Correction (noninverting) | Input         |

| QDCn          | Q-Channel DC Offset Correction (inverting)    | Input         |

| QOUTp         | Q-Channel Baseband Data (noninverting)        | Output        |

| QOUTn         | Q-Channel Baseband Data (inverting)           | Output        |

| RFINp         | RF Input (noninverting)                       | Input         |

| (Sheet 1 of 2 | 2)                                            |               |

Table 5 L64733 Pin Description Summary (Cont.)

| Mnemonic       | Description                            | Туре          |  |  |

|----------------|----------------------------------------|---------------|--|--|

| RFINn          | RF Input (inverting)                   | Input         |  |  |

| RFOUT          | RF Output (Loop-Through)               | Output        |  |  |

| TANKp          | Oscillator Tank Port (noninverting)    | Input         |  |  |

| TANKn          | Oscillator Tank Port (inverting)       | Input         |  |  |

| VRLO           | Local Oscillator Regulator Bypass      | Bidirectional |  |  |

| XTLp           | Crystal Oscillator Port (noninverting) | Input         |  |  |

| XTLn           | Crystal Oscillator Port (inverting)    | Input         |  |  |

| XTLOUT         | Crystal Out                            | Output        |  |  |

| (Sheet 2 of 2) |                                        |               |  |  |

## **L64734 Electrical Specifications**

This section contains the electrical parameters for the L64734. Table 6 lists the absolute maximum values. Exceeding the values listed can cause damage to the L64734. Table 7 gives the recommended operating supply voltage and temperature conditions. Table 8 shows the pin capacitance. Table 9 gives the DC characteristics. Table 10 summarizes the pins.

Table 6 L64734 Absolute Maximum Rating (Referenced to V<sub>SS</sub>)

| Symbol           | Parameter                           | Limits <sup>1</sup>          | Units |

|------------------|-------------------------------------|------------------------------|-------|

| V <sub>DD</sub>  | DC Supply Voltage                   | -0.3 to +3.9 V               | V     |

| V <sub>IN</sub>  | LVTTL Input Voltage                 | -1.0 to V <sub>DD</sub> +0.3 | V     |

| V <sub>IN</sub>  | 5 V Compatible Input Voltage        | -1.0 to 6.5                  | V     |

| I <sub>IN</sub>  | DC Input Current                    | ±10                          | mA    |

| T <sub>STG</sub> | Storage Temperature Range (Plastic) | -40 to +125                  | °C    |

Note that the ratings in this table are those beyond which permanent device damage is likely to occur. Do not use these values as the limits for normal device operation.

Table 7 L64734 Recommended Operating Conditions

| Symbol          | Parameter                                           | Limits <sup>1</sup> | Units   |

|-----------------|-----------------------------------------------------|---------------------|---------|

| V <sub>DD</sub> | DC Supply Voltage                                   | +3.14 to 3.47       | V       |

| T <sub>A</sub>  | Operating Ambient Temperature Range (Commercial)    | 0 to +70            | °C      |

| T <sub>j</sub>  | Junction Temperature                                | +125                | °C      |

| Θ <sub>ja</sub> | Junction to Ambient Thermal Resistance <sup>2</sup> | 21.7                | °C/watt |

| $\Theta_{jc}$   | Junction to Case Thermal Resistance <sup>3</sup>    | 5                   | °C/watt |

- For normal device operation, adhere to the limits in this table. Sustained operation of a device at conditions exceeding these values, even if they are within the absolute maximum rating limits, can result in permanent device damage or impaired device reliability. Device functionality to stated DC and AC limits is not guaranteed if recommended operating conditions are exceeded.

- 2. The junction to ambient thermal resistance is for the PQFPt (U4) package, for a four-layer board.

- 3. The junction to case thermal resistance is valid only for measurements in an isothermal environment including the board and package.

Table 8 L64734 Capacitance

| Symbol           | Parameter <sup>1</sup> | Max | Units |

|------------------|------------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance      | 5   | pF    |

| C <sub>OUT</sub> | Output Capacitance     | 5   | pF    |

Measurement conditions are V<sub>IN</sub> = 3.3 V, T<sub>A</sub> = 25 °C, and clock frequency = 1 MHz.

Table 9 DC Characteristics of the L64734

| Symbol               | Parameter                            | Condition <sup>1</sup>                                           | Min                        | Тур  | Max                      | Units |

|----------------------|--------------------------------------|------------------------------------------------------------------|----------------------------|------|--------------------------|-------|

| V <sub>DD</sub>      | Supply Voltage                       |                                                                  | 3.0                        | 3.3  | 3.6                      | ٧     |

| V <sub>IL</sub>      | Input Voltage LOW                    |                                                                  | V <sub>SS</sub><br>-0.5    | _    | 0.8                      | V     |

| V <sub>IH</sub>      | Input Voltage HIGH                   | LVTTL Com/Ind/Mil<br>Temp Range                                  | 2.0                        | _    | V <sub>DD</sub><br>+ 0.3 | V     |

|                      |                                      | 5 V compatible                                                   | 2.0                        | _    | 5.5                      | V     |

| V <sub>T</sub>       | Switching Threshold                  |                                                                  | _                          | 1.4  | 2.0                      | V     |

| I <sub>IL</sub>      | Input Current Leakage                | $V_{DD} = Max,$<br>$V_{IN} = V_{DD} \text{ or } V_{SS}$          | -10                        | ±1   | 10                       | μА    |

| I <sub>IPU</sub>     | Input Current Leakage with Pull-up   | V <sub>IN</sub> = V <sub>SS</sub>                                | -62                        | -215 | -384                     | μА    |

| I <sub>IPD</sub>     | Input Current Leakage with Pull-down | $V_{IN} = V_{DD}$                                                | -62                        | -215 | -384                     | μА    |

| V <sub>OH</sub>      | Output Voltage HIGH                  | I <sub>OH</sub> = -1.0, -2.0, -4.0,<br>-6.0, -8.0, -12.0 mA      | 2.4                        | _    | V <sub>DD</sub>          | V     |

| V <sub>OL</sub>      | Output Voltage LOW                   | I <sub>OH</sub> = 1.0, 2.0, 4.0, 6.0,<br>8.0, 12.0 mA            | _                          | 0.2  | 0.4                      | V     |

| I <sub>OZ</sub>      | 3-State Output Leakage<br>Current    | $V_{DD} = Max,$<br>$V_{OUT} = V_{SS} \text{ or } 3.5 \text{ V}$  | -10                        | ±1   | 10                       | μА    |

| I <sub>DD</sub>      | Quiescent Supply<br>Current          | $V_{IN} = V_{DD}$ or $V_{SS}$                                    | – 2 mA                     |      | mA                       |       |

| Icc                  | Dynamic Supply Current               | 20 Mbaud, rate = 3/4,<br>V <sub>DD</sub> = 3.3 V, Fs =<br>75 MHz | -                          | 290  | _                        | mA    |

| V <sub>CM</sub>      | Midpoint of PSOUTp,<br>PSOUTn inputs |                                                                  | _                          | 2.4  | -                        | V     |

| V <sub>IH_PECL</sub> | Input Voltage HIGH level (DC)        | PSOUTp - PSOUTn = 50 mV                                          | V <sub>CM</sub><br>+ 50 mV | -    | _                        | V     |

| (Sheet 1 of 2)       |                                      |                                                                  |                            |      |                          |       |

Table 9 DC Characteristics of the L64734 (Cont.)

| Symbol                 | Parameter                       | Condition <sup>1</sup>                 | Min   | Тур   | Max                       | Units |

|------------------------|---------------------------------|----------------------------------------|-------|-------|---------------------------|-------|

| V <sub>IL_PECL</sub>   | Input Voltage LOW level (DC)    | PSOUTp - PSOUTn = 50 mV                | -     | _     | V <sub>CM</sub><br>–50 mV | V     |

| I <sub>IL_PECL</sub>   | Input LOW current               | V <sub>IN</sub> = V <sub>SS</sub>      | -10   | _     | _                         | μΑ    |

| I <sub>IH_PECL</sub>   | Input HIGH current              | $V_{IN} = V_{DD}$                      | -     | _     | +10                       | μΑ    |

| V <sub>RESO_LVDS</sub> | Output Voltage on pin RESO_LVDS |                                        | _     | 1.2   | _                         | V     |

| V <sub>OH_LVDS</sub>   | Output Voltage HIGH level (DC)  | On PLLINp/PLLINn,<br>MODp/MODn signals | 1.253 | 1.373 | 1.437                     | V     |

| V <sub>OL_LVDS</sub>   | Output Voltage LOW level (DC)   | On PLLINp/PLLINn,<br>MODp/MODn signals | 1.030 | 1.032 | 1.059                     | V     |

| (Sheet 2 of 2          | (Sheet 2 of 2)                  |                                        |       |       |                           | 1     |

<sup>1.</sup> Specified at  $V_{DD}$  = 3.3 V  $\pm$  5% at ambient temperature over the specified range.

Table 10 L64734 Pin Description Summary

| Mnemonic       | Description           | Туре    |  |

|----------------|-----------------------|---------|--|

| ADCVDDI/Q      | ADC Power             | Input   |  |

| ADCVSSI/Q      | ADC Analog Ground     | Input   |  |

| AGC1, AGC2     | Power Control         | Outputs |  |

| BCLKOUT        | Byte Clock Out        | Output  |  |

| CLK            | Input Clock           | Input   |  |

| CO[7:0]        | Channel Data Out      | Output  |  |

| COEn           | Channel Output Enable | Input   |  |

| DVALIDOUT      | Valid Data Out        | Output  |  |

| ERROROUTn      | Error Detection Flag  | Output  |  |

| FDOUB          | Frequency Doubler     | Output  |  |

| (Sheet 1 of 3) |                       |         |  |

Table 10 L64734 Pin Description Summary (Cont.)

| Mnemonic       | Description                     | Туре          |

|----------------|---------------------------------|---------------|

| FLCLK          | Filter Control Clock            | Output        |

| FSTARTOUT      | Frame Start Output              | Output        |

| IBYPASS[5:0]   | I Channel Data (ADC bypassed)   | Input         |

| IDDTn          | Test                            | Input         |

| INSEL          | RF Input Select                 | Output        |

| INTn           | Interrupt                       | Output        |

| IVINn, IVINp   | I Channel Data                  | Input         |

| LCLK           | Decimated Clock Output          | Output        |

| LP2            | Input to VCO                    | Input         |

| MODp, MODn     | Modulus Selector                | Outputs       |

| PCLK           | PLL Clock Output                | Output        |

| PLLAGND        | PLL Analog Ground               | Input         |

| PLLINp, PLLINn | PLL Differential Counter M      | Outputs       |

| PLLVDD         | PLL Power                       | Input         |

| PLLVSS         | PLL Ground                      | Input         |

| PSOUTp, PSOUTn | Prescaler Output                | Outputs       |

| QBYPASS[5:0]   | Q Channel Data (ADC bypassed)   | Input         |

| QVINn, QVINp   | Q Channel Data                  | Input         |

| RESET          | Reset                           | Input         |

| RESO_LVDS      | LVDS Buffers Precision Resistor | Output        |

| SADR[1:0]      | Serial Address                  | Input         |

| SCLK           | Serial Clock                    | Bidirectional |

| SDATA          | Serial Data                     | Bidirectional |

| VREF_LVDS      | LVDS Buffers Reference Voltage  | Input         |

| (Sheet 2 of 3) |                                 |               |

Table 10 L64734 Pin Description Summary (Cont.)

| Mnemonic       | Description                     | Туре         |

|----------------|---------------------------------|--------------|

| VREFP          | Reference Voltage, Positive     | Input/Output |

| VREFN          | Reference Voltage, Negative     | Input/Output |

| VMID           | Reference Voltage, Middle       | Input/Output |

| XCTR_IN        | Control Input                   | Input        |

| XCTR[3:0]      | Control Output/Sync Status Flag | Output       |

| XOIN           | Crystal Oscillator In           | Input        |

| XOOUT          | Crystal Oscillator Out          | Output       |

| (Sheet 3 of 3) |                                 |              |

## L64734 AC Timing

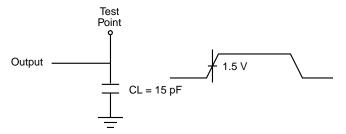

This section includes AC timing information for the L64734. During AC testing, HIGH inputs are driven to 3.0 V, and LOW inputs are driven to 0 V. For transitions between HIGH, LOW, and invalid states, timing measurements are made at 1.5 V, as shown in Figure 8.

Figure 8 AC Test Load and Waveform for Standard Outputs

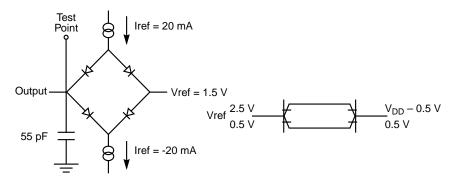

For 3-state outputs, timing measurements are made from the point at which the output turns ON or OFF. An output is ON when its voltage is greater than 2.5 V or less than 0.5 V. An output is OFF when its voltage is less than  $V_{DD}-0.5$  V or greater than 0.5 V, as shown in Figure 9.

Figure 9 AC Test Load and Waveforms for 3-State Outputs

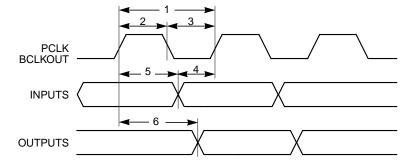

Synchronous timing is shown in Figure 10. Synchronous inputs must have a setup and hold relationship with respect to the clock signal that samples them. Synchronous outputs have a delay from the clock edge that asserts them.

Figure 10 L64734 Synchronous AC Timing

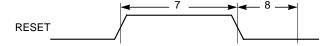

The reset pulse requirements are shown in Figure 11.

Figure 11 L64734 RESET Timing Diagram

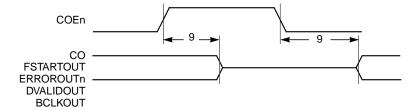

Figure 12 shows the relationship of the L64734 3-state signals to the COEn signal.

Figure 12 L64734 Bus 3-State Delay Timing

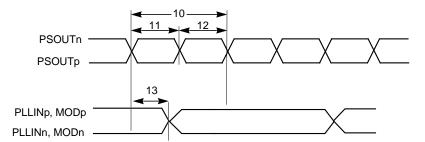

Figure 13 shows the relationship of the L64733 PSOUTp and PSOUTn prescaler signals to the signals fed back to the L64733 from the L64734 to control the synthesizer.

Figure 13 L64734 Synchronous AC Timing - Synthesizer Control

The numbers in the first column of Table 11 refer to the timing parameters shown in the preceding figures. All parameters in the timing tables apply for  $T_A = 0$  °C to 70 °C and a capacitive load of 15 pF.

Table 11 L64734 AC Timing Parameters

| Parameter |                       | Description                              | Min  | Max               | Units         |

|-----------|-----------------------|------------------------------------------|------|-------------------|---------------|

| 1         | t <sub>CYCLE</sub>    | Clock Cycle for PCLK                     | 11.1 | 33.3 <sup>1</sup> | ns            |

| 2         | t <sub>PWH</sub>      | Clock Pulse Width HIGH                   | 6    | _                 | ns            |

| 3         | t <sub>PWL</sub>      | Clock Pulse Width LOW                    | 5    | _                 | ns            |

| 4         | t <sub>S</sub>        | Input Setup Time to CLK                  | 4    | _                 | ns            |

| 5         | t <sub>H</sub>        | Input Hold to CLK                        | 4    | _                 | ns            |

| 6s        | t <sub>ODS</sub>      | Output Delay from PCLK, serial mode      | 3    | 8                 | ns            |

| 6р        | t <sub>ODP</sub>      | Output Delay from BCLKOUT, parallel mode | 3    | _                 | PCLK cycles   |

| 7         | t <sub>RWH</sub>      | Reset Pulse Width HIGH                   | 3    | _                 | CLK<br>cycles |

| 8         | t <sub>WK</sub>       | Wake-Up Time                             | 280  | _                 | CLK<br>cycles |

| 9         | t <sub>DLY</sub>      | Delay from COEn                          | _    | 6                 | ns            |

| 10        | t <sub>CYCLE_PS</sub> | Clock Cycle for PSOUTp, PSOUTn clock     | 14   | 35                | ns            |

| 11        | t <sub>PWH_PS</sub>   | PSOUT Clock Pulse Width HIGH             | 6    | _                 | ns            |

| 12        | t <sub>PWL_PS</sub>   | PSOUT Clock Pulse Width LOW              | 6    | _                 | ns            |

| 13        | t <sub>OD_PS</sub>    | Output Delay from PSOUT                  | 4    | 8.5               | ns            |

<sup>1.</sup> Minimum Fs (sampling clock = 30 MHz).

# L64733/34 Chipset Ordering and Part Marking Information

The L64733 and the L64734 are ordered as a set. Table 12 gives ordering information for the chipset.

Table 12 L64733/34 Chipset Ordering Information

| Order Number | Package Type  | Operating Range |  |

|--------------|---------------|-----------------|--|

| L64733B      | 48-pin TQFP   | Commercial      |  |

| L64734C-45   | 100-pin PQFPt | Commercial      |  |

Table 13 gives part marking information for the two chips.

Table 13 L64733 and L64734 Part Marking Information

| Part          | Production Chip Marking                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------|

| L64733 rev. B | LSI 64733<br>MAX2104<br>YYWW+ESD<br>MAXIM                                                                      |

| L64734 rev. C | LSI<br>L64734C-45<br>DBS Receiver<br>FMA YYWW+ESD<br>Assy Lot #<br>65060A1<br>OAS515U4FAA<br>Country of Origin |

The tables and figures that follow provide pinouts and mechanical drawings for each package in the chipset.

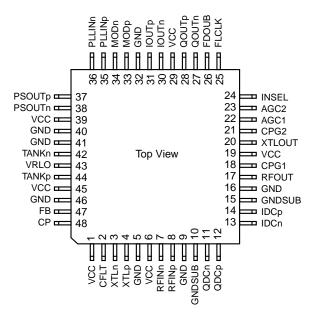

# L64733 Pinout and Packaging Information

### **Pinouts**

Figure 14 gives the pinout for the 48-pin TQFP L64733 package.

Figure 14 L64733 48-Pin TQFP Pinout

### **Mechanical Drawing**

Figure 15 is a mechanical drawing for the 48-pin TQFP L64733 package.

Figure 15 L64733 48-Pin TQFP Mechanical Drawing

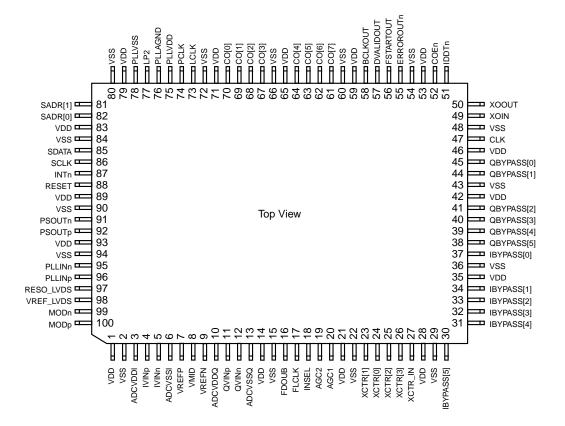

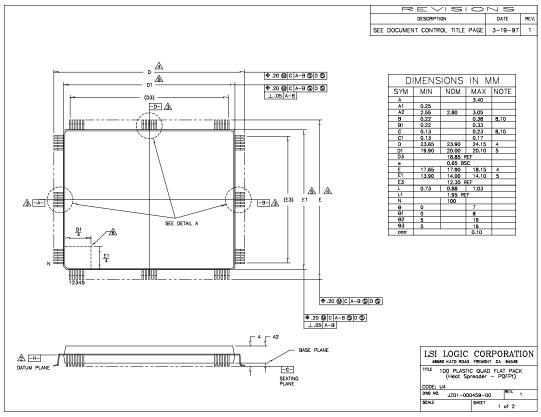

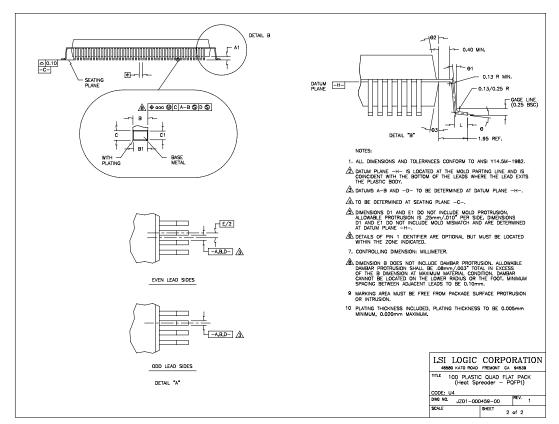

## L64734 Pinout and Packaging Information

### **Pinouts**

Figure 16 gives the pinout for the 100-pin PQFPt L64734 package.

Figure 16 L64734 100-Pin PQFPt Pinout

## **Mechanical Drawings**

Figure 17 is a mechanical drawing for the 100-pin PQFPt L64734 package.

Figure 17 100-Pin PQFPt (U4) Mechanical Drawing