March 2000

LM2765 Switched Capacitor Voltage Converter

# LM2765 Switched Capacitor Voltage Converter General Description Features

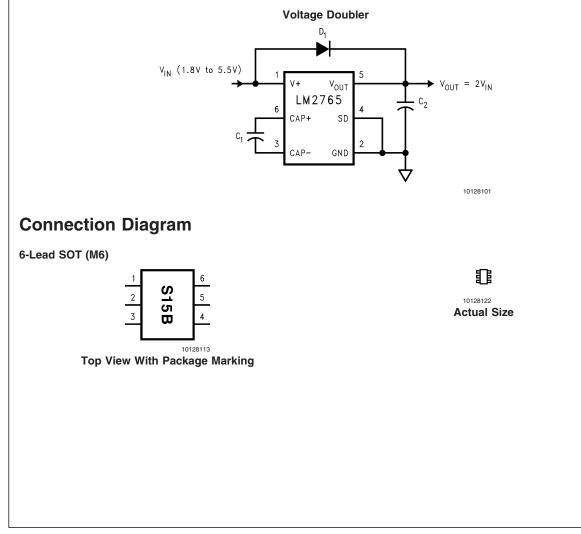

The LM2765 CMOS charge-pump voltage converter operates as a voltage doubler for an input voltage in the range of +1.8V to +5.5V. Two low cost capacitors and a diode are used in this circuit to provide up to 20 mA of output current.

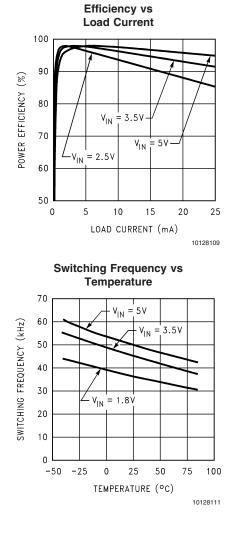

The LM2765 operates at 50 kHz switching frequency to reduce output resistance and voltage ripple. With an operating current of only 130  $\mu$ A (operating efficiency greater than 90% with most loads) and 0.1 $\mu$ A typical shutdown current, the LM2765 provides ideal performance for battery powered systems. The device is manufactured in a SOT-23-6 package.

- Doubles Input Supply Voltage

- SOT23-6 Package

- 20Ω Typical Output Impedance

- 90% Typical Conversion Efficiency at 20 mA

- 0.1µA Typical Shutdown Current

## **Applications**

- Cellular Phones

- Pagers

- PDAs

- Operational Amplifier Power Supplies

- Interface Power Supplies

- Handheld Instruments

## **Basic Application Circuits**

# Ordering Information

| Order Number | Package Number | Package Marking | Supplied as                     |

|--------------|----------------|-----------------|---------------------------------|

| LM2765M6     | MA06A          | S15B (Note 1)   | Tape and Reel (1000 units/reel) |

| LM2765M6X    | MA06A          | S15B (Note 1)   | Tape and Reel (3000 units/reel) |

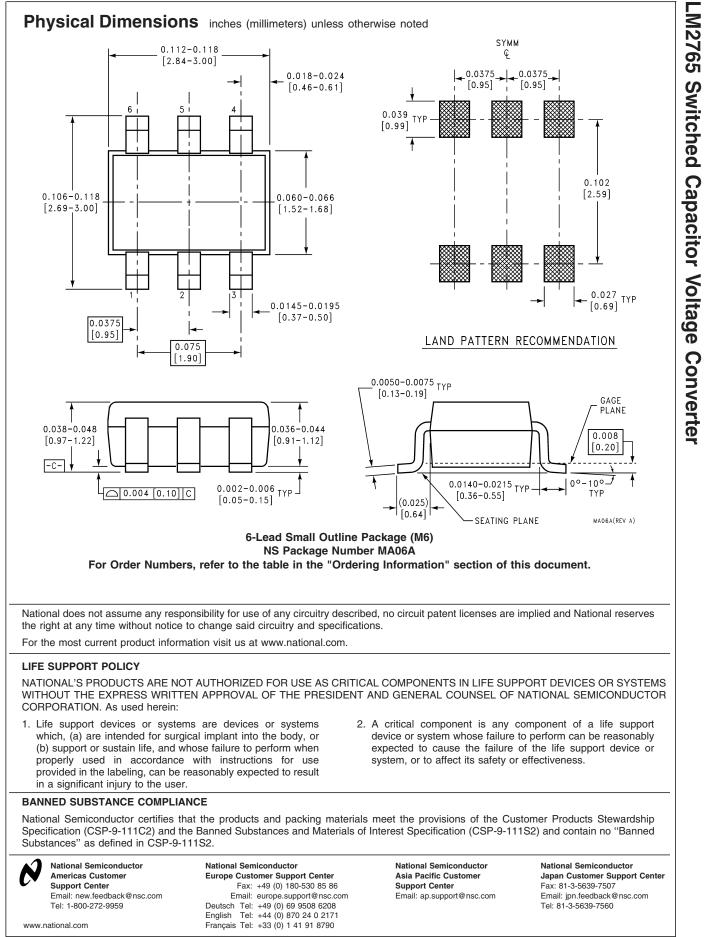

Note 1: The small physical size of the SOT-23 package does not allow for the full part number marking. Devices will be marked with the designation shown in the column Package Marking.

# **Pin Description**

| Pin | Name             | Function                                                          |  |

|-----|------------------|-------------------------------------------------------------------|--|

| 1   | V+               | Power supply positive voltage input.                              |  |

| 2   | GND              | Power supply ground input.                                        |  |

| 3   | CAP-             | Connect this pin to the negative terminal of the charge-pump      |  |

|     | CAP-             | capacitor.                                                        |  |

| 4   | SD               | Shutdown control pin, tie this pin to ground in normal operation. |  |

| 5   | V <sub>OUT</sub> | Positive voltage output.                                          |  |

| 6   | CAP+             | Connect this pin to the positive terminal of the charge-pump      |  |

| 0   | CAF+             | capacitor.                                                        |  |

www.national.com

## Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V+ to GND, or V+ to $V_{OUT}$ ) | 5.8V         |

|-------------------------------------------------|--------------|

| SD (GND – 0.3                                   | SV) to (V+ + |

|                                                 | 0.3V)        |

| VOUT Continuous Output Current                  | 40 mA        |

| Output Short-Circuit Duration to GND (Note 3)   | 1 sec.       |

| Continuous Power                                | 600 mW       |

| Dissipation $(T_A = 25^{\circ}C)(Note 4)$       |              |

| T <sub>JMax</sub> (Note 4)                      | 150°C        |

## **Operating Ratings**

| $\theta_{14}$ (Note 4)     | 210°C/W        |

|----------------------------|----------------|

| OJA (NOTE 4)               | 210 0/00       |

| Junction Temperature Range | –40° to 100°C  |

| Ambient Temperature Range  | –40° to 85°C   |

| Storage Temperature Range  | –65°C to 150°C |

| Lead Temp. (Soldering, 10  |                |

| seconds)                   | 240°C          |

| ESD Rating (Note 5)        |                |

| Human body model           | 2kV            |

| Machine model              | 200V           |

## **Electrical Characteristics**

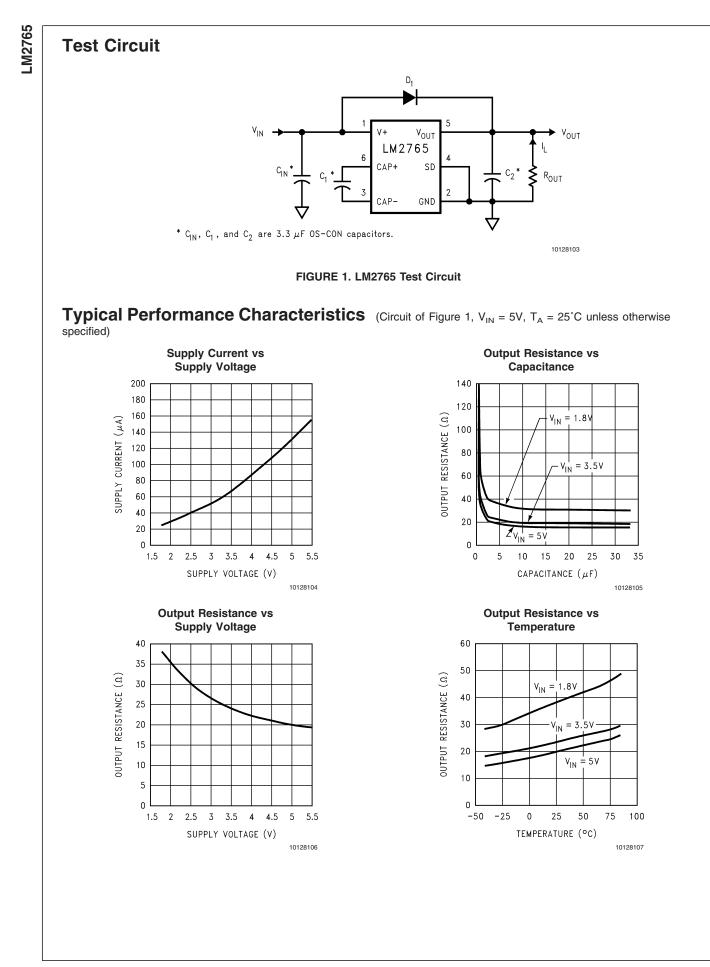

Limits in standard typeface are for  $T_J = 25$ °C, and limits in **boldface** type apply over the full operating temperature range. Unless otherwise specified: V+ = 5V,  $C_1 = C_2 = 3.3 \ \mu$ F. (Note 6)

| Symbol            | Parameter                     | Condition                    | Min | Тур   | Max | Units |

|-------------------|-------------------------------|------------------------------|-----|-------|-----|-------|

| V+                | Supply Voltage                |                              | 1.8 |       | 5.5 | V     |

| l <sub>Q</sub>    | Supply Current                | No Load                      |     | 130   | 450 | μA    |

| I <sub>SD</sub>   | Shutdown Supply Current       |                              |     | 0.1   | 0.5 | μA    |

|                   |                               | T <sub>A</sub> = 85°C        |     | 0.2   |     |       |

| V <sub>SD</sub>   | Shutdown Pin Input Voltage    | Shutdown Mode                | 2.0 |       |     | v     |

|                   |                               | Normal Operation             |     |       | 0.6 | v     |

| IL                | Output Current                | $2.5V \le V_{IN} \le 5.5V$   | 20  |       |     |       |

|                   |                               | $1.8V \le V_{IN} \le 2.5V$   | 10  |       |     | - mA  |

| R <sub>OUT</sub>  | Output Resistance (Note 7)    | I <sub>L</sub> = 20 mA       |     | 20    | 40  | Ω     |

| f <sub>osc</sub>  | Oscillator Frequency          | (Note 8)                     | 40  | 100   | 200 | kHz   |

| f <sub>sw</sub>   | Switching Frequency           | (Note 8)                     | 20  | 50    | 100 | kHz   |

| P <sub>EFF</sub>  | Power Efficiency              | $I_L = 20 \text{ mA to GND}$ |     | 92    |     | %     |

| V <sub>OEFF</sub> | Voltage Conversion Efficiency | No Load                      |     | 99.96 |     | %     |

Note 2: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 3: V<sub>OUT</sub> may be shorted to GND for one second without damage. However, shorting V<sub>OUT</sub> to V+ may damage the device and should be avoided. Also, for temperatures above 85°C, OUT must not be shorted to GND or V+, or device may be damaged.

Note 4: The maximum allowable power dissipation is calculated by using  $P_{DMax} = (T_{JMax} - T_A)/\theta_{JA}$ , where  $T_{JMax}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance of the specified package.

Note 5: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

Note 6: In the test circuit, capacitors  $C_1$  and  $C_2$  are 3.3  $\mu$ F, 0.3 $\Omega$  maximum ESR capacitors. Capacitors with higher ESR will increase output resistance, reduce output voltage and efficiency.

**Note 7:** Specified output resistance includes internal switch resistance and capacitor ESR. See the details in the application information for positive voltage doubler. **Note 8:** The output switches operate at one half of the oscillator frequency,  $f_{OSC} = 2f_{SW}$ . LM2765

www.national.com

Downloaded from Datasheet.su

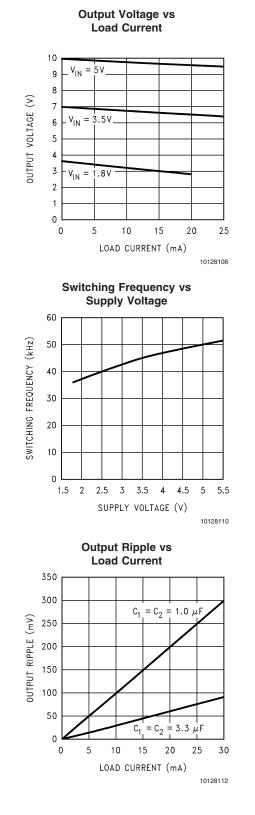

**Typical Performance Characteristics** (Circuit of Figure 1,  $V_{IN} = 5V$ ,  $T_A = 25^{\circ}C$  unless otherwise specified) (Continued)

LM2765

### **Circuit Description**

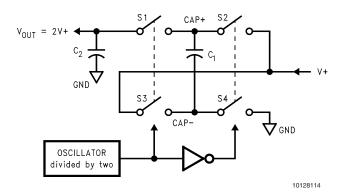

The LM2765 contains four large CMOS switches which are switched in a sequence to double the input supply voltage. Energy transfer and storage are provided by external capacitors. Figure 2 illustrates the voltage conversion scheme. When  $S_2$  and  $S_4$  are closed,  $C_1$  charges to the supply voltage V+. During this time interval, switches  $S_1$  and  $S_3$  are open. In the next time interval,  $S_2$  and  $S_4$  are open; at the same time,  $S_1$  and  $S_3$  are closed, the sum of the input voltage V+ and the voltage across  $C_1$  gives the 2V+ output voltage when there is no load. The output voltage drop when a load is added is determined by the parasitic resistance ( $R_{ds(on)}$  of the MOSFET switches and the ESR of the capacitors) and the charge transfer loss between capacitors. Details will be discussed in the following application information section.

FIGURE 2. Voltage Doubling Principle

## **Application Information**

#### POSITIVE VOLTAGE DOUBLER

The main application of the LM2765 is to double the input voltage. The range of the input supply voltage is 1.8V to 5.5V.

The output characteristics of this circuit can be approximated by an ideal voltage source in series with a resistance. The voltage source equals 2V+. The output resistance  $R_{out}$  is a function of the ON resistance of the internal MOSFET switches, the oscillator frequency, and the capacitance and ESR of C<sub>1</sub> and C<sub>2</sub>. Since the switching current charging and discharging C<sub>1</sub> is approximately twice as the output current, the effect of the ESR of the pumping capacitor C<sub>1</sub> will be multiplied by four in the output resistance. The output capacitor C<sub>2</sub> is charging and discharging at a current approximately equal to the output current, therefore, its ESR only counts once in the output resistance. A good approximation of R<sub>out</sub> is:

$$R_{OUT} \simeq 2R_{SW} + \frac{2}{f_{OSC} \times C_1} + 4ESR_{C1} + ESR_{C2}$$

where  ${\sf R}_{SW}$  is the sum of the ON resistance of the internal MOSFET switches shown in Figure 2.  ${\sf R}_{SW}$  is typically  $8\Omega$  for the LM2765.

The peak-to-peak output voltage ripple is determined by the oscillator frequency as well as the capacitance and ESR of the output capacitor  $C_2$ :

$$V_{RIPPLE} = \frac{I_L}{f_{OSC} \times C_2} + 2 \times I_L \times ESR_{C2}$$

High capacitance, low ESR capacitors can reduce both the output resistance and the voltage ripple.

The Schottky diode  $D_1$  is only needed to protect the device from turning-on its own parasitic diode and potentially latching-up. During start-up,  $D_1$  will also quickly charge up the output capacitor to  $V_{IN}$  minus the diode drop thereby decreasing the start-up time. Therefore, the Schottky diode  $D_1$  should have enough current carrying capability to charge the output capacitor at start-up, as well as a low forward voltage to prevent the internal parasitic diode from turningon. A Schottky diode like 1N5817 can be used for most applications. If the input voltage ramp is less than 10V/ms, a smaller Schottky diode like MBR0520LT1 can be used to reduce the circuit size.

#### SHUTDOWN MODE

A shutdown (SD) pin is available to disable the device and reduce the quiescent current to 0.1  $\mu$ A. In normal operating mode, the SD pin is connected to ground. The device can be brought into the shutdown mode by applying to the SD pin a voltage greater than 40% of the V+ pin voltage.

#### CAPACITOR SELECTION

As discussed in the *Positive Voltage Doubler* section, the output resistance and ripple voltage are dependent on the capacitance and ESR values of the external capacitors. The output voltage drop is the load current times the output resistance, and the power efficiency is

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{I_{L}^{2}R_{L}}{I_{L}^{2}R_{L} + I_{L}^{2}R_{OUT} + I_{Q}(V+)}$$

Where  $I_Q(V+)$  is the quiescent power loss of the IC device, and  $I_L^2 R_{out}$  is the conversion loss associated with the switch on-resistance, the two external capacitors and their ESRs.

The selection of capacitors is based on the specifications of the dropout voltage (which equals  $I_{out}$ ,  $R_{out}$ ), the output voltage ripple, and the converter efficiency. Low ESR capacitors (*Table 1*) are recommended to maximize efficiency, reduce the output voltage drop and voltage ripple.

www.national.com

## Application Information (Continued)

**TABLE 1. Low ESR Capacitor Manufacturers**

|  |  | _ |

|--|--|---|

|  |  |   |

LM2765

| Manufacturer   | Phone          | Website            | Capacitor Type                                     |

|----------------|----------------|--------------------|----------------------------------------------------|

| Nichicon Corp. | (847)-843-7500 | www.nichicon.com   | PL & PF series, through-hole aluminum electrolytic |

| AVX Corp.      | (843)-448-9411 | www.avxcorp.com    | TPS series, surface-mount tantalum                 |

| Sprague        | (207)-324-4140 | www.vishay.com     | 593D, 594D, 595D series, surface-mount tantalum    |

| Sanyo          | (619)-661-6835 | www.sanyovideo.com | OS-CON series, through-hole aluminum electrolytic  |

| Murata         | (800)-831-9172 | www.murata.com     | Ceramic chip capacitors                            |

| Taiyo Yuden    | (800)-348-2496 | www.t-yuden.com    | Ceramic chip capacitors                            |

| Tokin          | (408)-432-8020 | www.tokin.com      | Ceramic chip capacitors                            |

## **Other Applications**

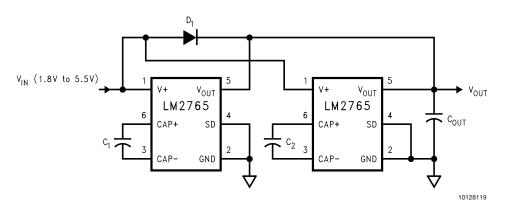

#### PARALLELING DEVICES

Any number of LM2765s can be paralleled to reduce the output resistance. Each device must have its own pumping capacitor  $C_1$ , while only one output capacitor  $C_{out}$  is needed as shown in Figure 3. The composite output resistance is:

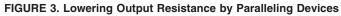

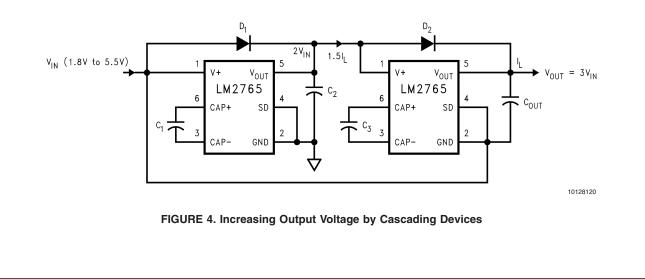

#### CASCADING DEVICES

$R_{out} = 1.5R_{out 1} + R_{out 2}$

Cascading the LM2765s is an easy way to produce a greater voltage (A two-stage cascade circuit is shown in Figure 4). The effective output resistance is equal to the weighted sum of each individual device:

Note that increasing the number of cascading stages is pracitically limited since it significantly reduces the efficiency, increases the output resistance and output voltage ripple.

# $R_{OUT} = \frac{R_{OUT} \text{ of each LM2765}}{\text{Number of Devices}}$

## Other Applications (Continued)

#### **REGULATING VOUT**

It is possible to regulate the output of the LM2765 by use of a low dropout regulator (such as LP2980-5.0). The whole converter is depicted in Figure 5.

A different output voltage is possible by use of LP2980-3.3, LP2980-3.0, or LP2980-adj.

Note that the following conditions must be satisfied simultaneously for worst case design:

$2V_{in\_min} > V_{out\_min} + V_{drop\_max} (LP2980) + I_{out\_max} x R_{out}$ \_max (LM2765)

$2V_{in\_max} \le V_{out\_max} + V_{drop\_min} (LP2980) + I_{out\_min} x R_{out}$ \_min (LM2765)

D<sub>1</sub> 5  $V_{IN}$ ٧+ VOUT 5V, 20 mA = 3V V<sub>OUT</sub> VIN LP2980-5.0 LM2765  $C_2$ C.3 2 6 GND CAP+ 3.3 μF 2.2 μF SD ON/OFF N/C GND CAP-

10128121

FIGURE 5. Generate a Regulated +5V from +3V Input Voltage

www.national.com