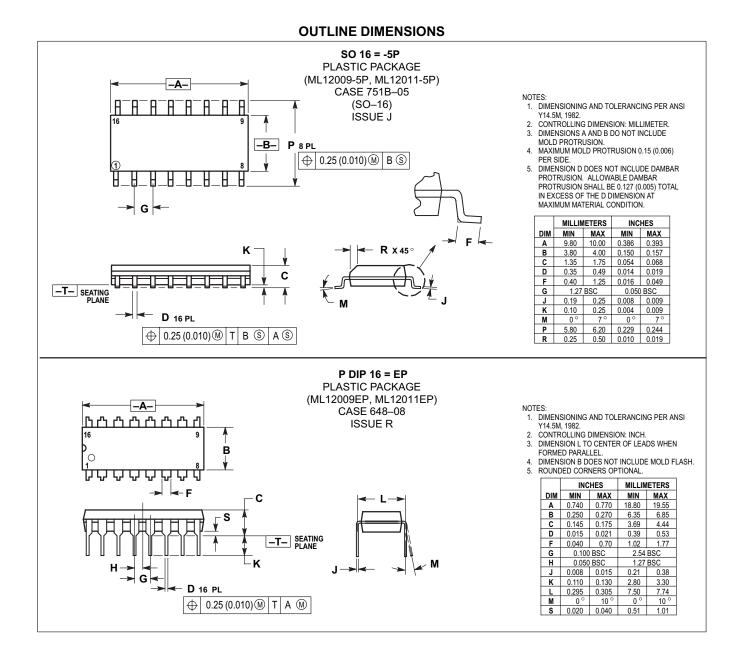

# ML12009 ML12011 MECL PLL Components Dual Modulus Prescaler

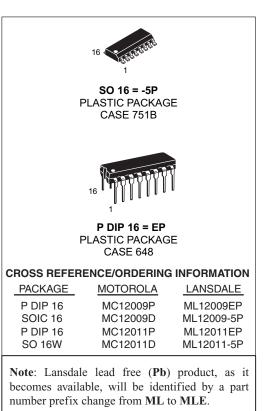

Legacy Device: Motorola MC12009, MC12011

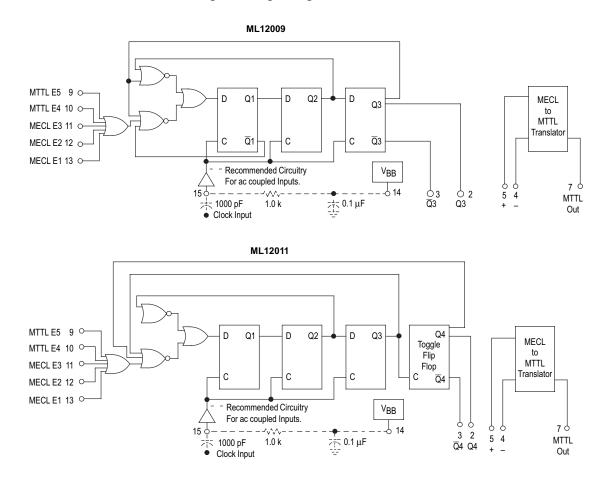

These devices are two-modulus prescalers which will divide by 5 and 6, 8 and 9, respectively. A MECL-to-MTTL translator is provided to interface directly with the Motorola MC12014 Counter Control Logic. In addition, there is a buffered clock input and MECL bias voltage source.

- ML12009 480 MHz (÷5/6), ML12011 550 MHz (÷8/9)

- MECL to MTTL Translator on Chip

- MECL and MTTL Enable Inputs

- 5.0 or -5.2 V Operation\*

- Buffered Clock Input Series Input RC Typ, 20  $\Omega$  and 4.0 pF

- VBB Reference Voltage

- 310 mW (Typ)

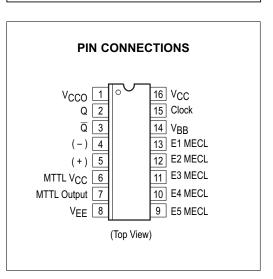

\* When using a 5.0 V supply, apply 5.0 V to Pin 1 (V<sub>CCO</sub>), Pin 6 (MTTL V<sub>CC</sub>), Pin 16 (V<sub>CC</sub>), and ground Pin 8 (V<sub>EE</sub>). When using -5.2 V supply, ground Pin 1 (V<sub>CCO</sub>), Pin 6 (MTTL V<sub>CC</sub>), and Pin 16 (V<sub>CC</sub>) and apply -5.2 V to Pin 8 (V<sub>EE</sub>). If the translator is not required, Pin 6 may be left open to conserve DC power drain.

### MAXIMUM RATINGS

| Characteristic                                | Symbol           | Rating               | Unit |

|-----------------------------------------------|------------------|----------------------|------|

| (Ratings above which device life ma           | ay be impaired   | (t                   |      |

| Power Supply Voltage<br>(V <sub>CC</sub> = 0) | V <sub>EE</sub>  | -8.0                 | Vdc  |

| Input Voltage<br>(V <sub>CC</sub> = 0)        | V <sub>in</sub>  | 0 to V <sub>EE</sub> | Vdc  |

| Output Source Current<br>Continuous<br>Surge  | lO               | <50<br><100          | mAdc |

| Storage Temperature Range                     | T <sub>stg</sub> | -65 to 175           | °C   |

| (Peacempended Maximum Patinga                 | ahaya which      | oorformonoo ma       | w ha |

(Recommended Maximum Ratings above which performance may be degraded)

| Operating Temperature Range<br>ML12009, ML12011 | Т <sub>А</sub> | -30 to 85 | °C |

|-------------------------------------------------|----------------|-----------|----|

| DC Fan–Out (Note 1)<br>(Gates and Flip–Flops)   | n              | 70        | —  |

NOTES: 1. AC fan-out is limited by desired system performance.

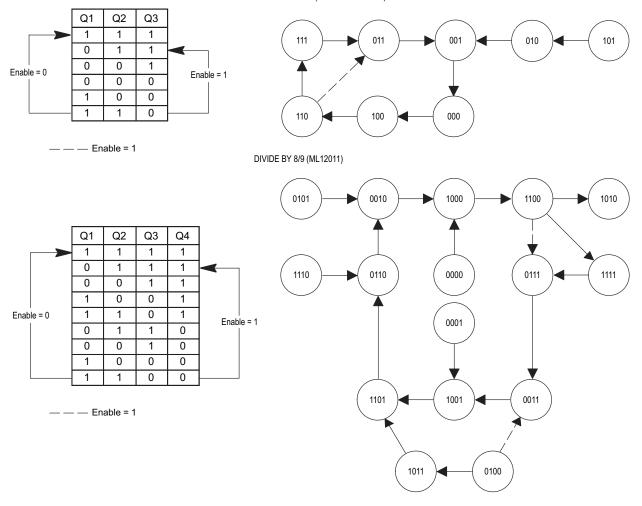

#### Figure 1. Logic Diagrams

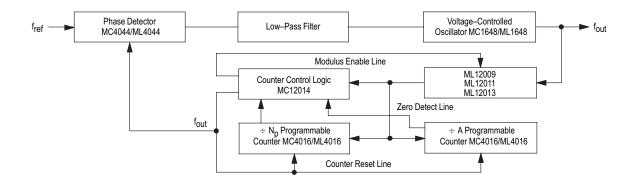

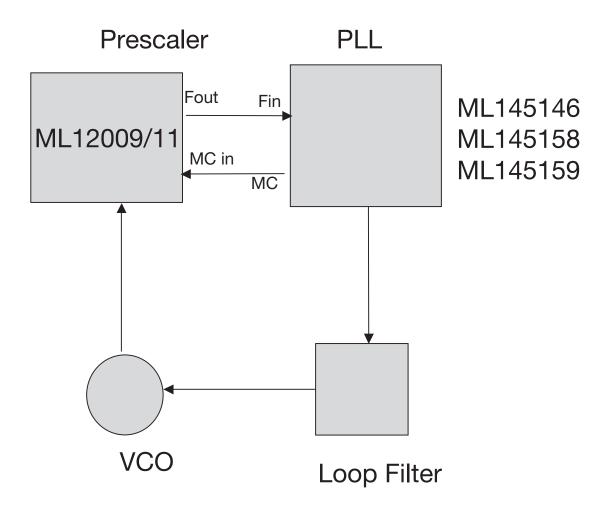

Figure 2. Typical Frequency Synthesizer Application

# Figure 2b Generic block diagram showing prescaler connection to PLL Device

Figure 2b shows a generic block diagram of connecting a prescaler to a PLL device that supports dual modulus controls. Applicataion not AN535 describes using a two–modulus prescaler technique. By using prescaler higher frequencies can be achieved than by a single CMOS PLL device.

#### ELECTRICAL CHARACTERISTICS (Supply Voltage = -5.2 V, unless otherwise noted.)

|                             |                              |                      |                          |                          | Test L                   | imits                    |                          |                          |      |

|-----------------------------|------------------------------|----------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|

|                             |                              | Pin<br>Under         | -30                      | D∘C                      | 25                       | °C                       | 85                       | o°C                      | ]    |

| Characteristic              | Symbol                       | Test                 | Min                      | Max                      | Min                      | Max                      | Min                      | Max                      | Unit |

| Power Supply Drain Current  | ICC1                         | 8                    | -88                      |                          | -80                      |                          | -80                      |                          | mAdc |

|                             | ICC2                         | 6                    |                          | 5.2                      |                          | 5.2                      |                          | 5.2                      | mAdc |

| Input Current               | linH1                        | 15<br>11<br>12<br>13 |                          | 375<br>375<br>375<br>375 |                          | 250<br>250<br>250<br>250 |                          | 250<br>250<br>250<br>250 | μAdc |

|                             | linH2                        | 4<br>5               | 1.7<br>1.7               | 6.0<br>6.0               | 2.0<br>2.0               | 6.0<br>6.0               | 2.0<br>2.0               | 6.4<br>6.4               | mAdc |

|                             | l <sub>inH3</sub>            | 5                    | 0.7                      | 3.0                      | 1.0                      | 3.0                      | 1.0                      | 3.6                      |      |

|                             | linH4                        | 9<br>10              |                          | 100<br>100               |                          | 100<br>100               |                          | 100<br>100               | μAdc |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13 | -10<br>-10<br>-10<br>-10 |                          | -10<br>-10<br>-10<br>-10 |                          | -10<br>-10<br>-10<br>-10 |                          | µAdc |

|                             | linL2                        | 9<br>10              | -1.6<br>-1.6             |                          | -1.6<br>-1.6             |                          | -1.6<br>-1.6             |                          | mAdc |

| Reference Voltage           | V <sub>BB</sub>              | 14                   |                          |                          | -1.360                   | -1.160                   |                          |                          | Vdc  |

| Logic '1' Output Voltage    | VOH1<br>(Note 1)             | 2<br>3               | -1.100<br>-1.100         | -0.890<br>-0.890         | -1.000<br>-1.000         | -0.810<br>-0.810         | -0.930<br>-0.930         | -0.700<br>-0.700         | Vdc  |

|                             | V <sub>OH2</sub>             | 7                    | -2.8                     |                          | -2.6                     |                          | -2.4                     |                          | ]    |

| Logic '0' Output Voltage    | VOL1<br>(Note 1)             | 2<br>3               | -1.990<br>-1.990         | -1.675<br>-1.675         | -1.950<br>-1.950         | -1.650<br>-1.650         | -1.925<br>-1.925         | -1.615<br>-1.615         | Vdc  |

|                             | V <sub>OL2</sub>             | 7                    |                          | -4.26                    |                          | -4.40                    |                          | -4.48                    | 1    |

| Logic '1' Threshold Voltage | V <sub>OHA</sub><br>(Note 2) | 2<br>3               | -1.120<br>-1.120         |                          | -1.020<br>-1.020         |                          | -0.950<br>-0.950         |                          | Vdc  |

| Logic '0' Threshold Voltage | V <sub>OLA</sub><br>(Note 3) | 2<br>3               |                          | -1.655<br>-1.655         |                          | -1.630<br>-1.630         |                          | -1.595<br>-1.595         | Vdc  |

| Short Circuit Current       | IOS                          | 7                    | -65                      | -20                      | -65                      | -20                      | -65                      | -20                      | mAdc |

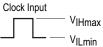

ground voltages must be maintained between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock

VIHmax

VILmin

input is the waveform shown.

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50 Ω resistor to -2.0 V. Test procedures are shown for only one gate. The other gates are tested in the same manner.

|                             | •                            | , , , , ,            |                      | TEST V               |                      |                      | UES      |              |                                      |

|-----------------------------|------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------|--------------|--------------------------------------|

|                             |                              |                      |                      |                      | Volt                 |                      |          |              |                                      |

|                             | @ Test Temp                  | perature             | V <sub>IHmax</sub>   | V <sub>ILmin</sub>   | V <sub>IHAmin</sub>  | V <sub>ILAmax</sub>  | VIH      | VILH         |                                      |

|                             |                              | –30°C                | -0.890               | -1.990               | -1.205               | -1.500               | -2.8     | -4.7         |                                      |

|                             |                              | 25°C                 | -0.810               | -1.950               | -1.105               | -1.475               | -2.8     | -4.7         |                                      |

|                             |                              | 85°C                 | -0.700               | -1.925               | -1.035               | -1.440               | -2.8     | -4.7         |                                      |

|                             |                              | Pin                  | TE                   | ST VOLTAGE           | APPLIED              | TO PINS LIS          | TED BELC | w            |                                      |

| Characteristic              | Symbol                       | Under<br>Test        | V <sub>IHmax</sub>   | V <sub>ILmin</sub>   | VIHAmin              | VILAmax              | VIH      | VIL          | Gnd                                  |

| Power Supply Drain Current  | ICC1                         | 8                    |                      |                      |                      |                      |          |              | 1,16                                 |

|                             | ICC2                         | 6                    | 4                    | 5                    |                      |                      |          |              | 6                                    |

| Input Current               | linH1                        | 15<br>11<br>12<br>13 | 15<br>11<br>12<br>13 |                      |                      |                      |          |              | 1,16<br>1,16<br>1,16<br>1,16         |

|                             | linH2                        | 4<br>5               | 5<br>5               | 4<br>4               |                      |                      |          |              | 6<br>6                               |

|                             | l <sub>inH3</sub>            | 5                    | 4                    | 5                    |                      |                      |          |              | 6                                    |

|                             | linH4                        | 9<br>10              |                      |                      |                      |                      | 9<br>10  |              | 1,16<br>1,16                         |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13 |                      |                      |                      |                      |          |              | 1,16<br>1,16<br>1,16<br>1,16<br>1,16 |

|                             | linL2                        | 9<br>10              |                      |                      |                      |                      |          | 9<br>10      | 1,16<br>1,16                         |

| Reference Voltage           | V <sub>BB</sub>              | 14                   |                      |                      |                      |                      |          |              | 1,16                                 |

| Logic '1' Output Voltage    | V <sub>OH1</sub><br>(Note 1) | 2<br>3               |                      | 11,12,13<br>11,12,13 |                      |                      |          | 9,10<br>9,10 | 1,16<br>1,16                         |

|                             | V <sub>OH2</sub>             | 7                    | 5                    | 4                    |                      |                      |          |              | 6                                    |

| Logic '0' Output Voltage    | VOL1<br>(Note 1)             | 2<br>3               |                      | 11,12,13<br>11,12,13 |                      |                      |          | 9,10<br>9,10 | 1,16<br>1,16                         |

|                             | V <sub>OL2</sub>             | 7                    | 4                    | 5                    |                      |                      |          |              | 6                                    |

| Logic '1' Threshold Voltage | V <sub>OHA</sub><br>(Note 2) | 2<br>3               |                      |                      | 11,12,13<br>11,12,13 |                      |          |              | 1,16<br>1,16                         |

| Logic '0' Threshold Voltage | VOLA<br>(Note 3)             | 2<br>3               |                      |                      |                      | 11,12,13<br>11,12,13 |          |              | 1,16<br>1,16                         |

| Short Circuit Current       | IOS                          | 7                    | 5                    | 4                    |                      |                      |          | 7            | 6                                    |

# ELECTRICAL CHARACTERISTICS (continued) (Supply Voltage = -5.2 V, unless otherwise noted.)

NOTES: 1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and ground voltages must be maintained between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock

input is the waveform shown.

Clock Input VIHmax VILmin

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

|                             |                              |                                |                                           | TEST V       | OLTAGE/CU                    | JRRENT VA | LUES |       |                                      |  |  |

|-----------------------------|------------------------------|--------------------------------|-------------------------------------------|--------------|------------------------------|-----------|------|-------|--------------------------------------|--|--|

|                             |                              |                                |                                           | Volts        |                              |           | mA   |       | 1                                    |  |  |

|                             | @ Test Temp                  | Test Temperature VIHT VILT VEE |                                           |              |                              | ١L        | ЮН   | ]     |                                      |  |  |

|                             |                              | –30°C                          | -3.2                                      | -4.4         | -5.2                         | -0.25     | 16   | -0.40 | 1                                    |  |  |

|                             |                              | 25°C                           | -3.2                                      | -4.4         | -5.2                         | -0.25     | 16   | -0.40 | ]                                    |  |  |

|                             |                              | 85°C                           | -3.2                                      | -4.4         | -5.2                         | -0.25     | 16   | -0.40 | ]                                    |  |  |

|                             |                              | Pin                            | TEST VOLTAGE APPLIED TO PINS LISTED BELOW |              |                              |           |      |       |                                      |  |  |

| Characteristic              | Symbol                       | Under<br>Test                  | VIHT                                      | VILT         | VEE                          | ١L        | IOL  | Іон   | Gnd                                  |  |  |

| Power Supply Drain Current  | ICC1                         | 8                              |                                           |              | 8                            |           |      |       | 1,16                                 |  |  |

|                             | ICC2                         | 6                              |                                           |              | 8                            |           |      |       | 6                                    |  |  |

| Input Current               | linH1                        | 15<br>11<br>12<br>13           | 9,10<br>9,10<br>9,10                      |              | 8<br>8<br>8<br>8             |           |      |       | 1,16<br>1,16<br>1,16<br>1,16<br>1,16 |  |  |

|                             | linH2                        | 4<br>5                         |                                           |              | 8<br>8                       |           |      |       | 6<br>6                               |  |  |

|                             | l <sub>inH3</sub>            | 5                              |                                           |              | 8                            |           |      |       | 6                                    |  |  |

|                             | linH4                        | 9<br>10                        |                                           |              | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13           |                                           |              | 8,15<br>8,11<br>8,12<br>8,13 |           |      |       | 1,16<br>1,16<br>1,16<br>1,16<br>1,16 |  |  |

|                             | linL2                        | 9<br>10                        |                                           |              | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

| Reference Voltage           | V <sub>BB</sub>              | 14                             |                                           |              | 8                            | 14        |      |       | 1,16                                 |  |  |

| Logic '1' Output Voltage    | VOH1<br>(Note 1)             | 2<br>3                         |                                           |              | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

|                             | VOH2                         | 7                              |                                           |              | 8                            |           |      | 7     | 6                                    |  |  |

| Logic '0' Output Voltage    | VOL1<br>(Note 1)             | 2<br>3                         |                                           |              | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

|                             | V <sub>OL2</sub>             | 7                              |                                           |              | 8                            |           | 7    |       | 6                                    |  |  |

| Logic '1' Threshold Voltage | VOHA<br>(Note 2)             | 2<br>3                         | 9,10<br>9,10                              |              | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

| Logic '0' Threshold Voltage | V <sub>OLA</sub><br>(Note 2) | 2<br>3                         |                                           | 9,10<br>9,10 | 8<br>8                       |           |      |       | 1,16<br>1,16                         |  |  |

| Short Circuit Current       | los                          | 7                              |                                           |              | 8                            |           |      |       | 6                                    |  |  |

|                             |                              |                                |                                           | •            |                              |           |      |       |                                      |  |  |

# ELECTRICAL CHARACTERISTICS (continued) (Supply Voltage = -5.2 V, unless otherwise noted.)

NOTES: 1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and ground voltages must be maintained between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock

input is the waveform shown.

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

#### ELECTRICAL CHARACTERISTICS (Supply Voltage = 5.0 V, unless otherwise noted.)

|                             |                              |                      |                          |                                 | Test I                   | .imits                   |                          |                          |      |

|-----------------------------|------------------------------|----------------------|--------------------------|---------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|

|                             |                              | Pin<br>Under         | -30                      | 0°C                             | 25                       | °C                       | 85                       | °C                       | 1    |

| Characteristic              | Symbol                       | Test                 | Min                      | Max                             | Min                      | Max                      | Min                      | Мах                      | Unit |

| Power Supply Drain Current  | ICC1                         | 8                    | -88                      |                                 | -80                      |                          | -80                      |                          | mAdc |

|                             | I <sub>CC2</sub>             | 6                    |                          | 5.2                             |                          | 5.2                      |                          | 5.2                      | mAdc |

| Input Current               | linH1                        | 15<br>11<br>12<br>13 |                          | 375<br>375<br>375<br>375<br>375 |                          | 250<br>250<br>250<br>250 |                          | 250<br>250<br>250<br>250 | μAdc |

|                             | linH2                        | 4<br>5               | 1.7<br>1.7               | 6.0<br>6.0                      | 2.0<br>2.0               | 6.0<br>6.0               | 2.0<br>2.0               | 6.4<br>6.4               | mAdc |

|                             | l <sub>inH3</sub>            | 5                    | 0.7                      | 3.0                             | 1.0                      | 3.0                      | 1.0                      | 3.6                      |      |

|                             | linH4                        | 9<br>10              |                          |                                 | 100<br>100               | 100<br>100               |                          | 100<br>100               | μAdc |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13 | -10<br>-10<br>-10<br>-10 |                                 | -10<br>-10<br>-10<br>-10 |                          | -10<br>-10<br>-10<br>-10 |                          | μAdc |

|                             | linL2                        | 9<br>10              | -1.6<br>-1.6             |                                 | -1.6<br>-1.6             |                          | -1.6<br>-1.6             |                          | mAdc |

| Reference Voltage           | V <sub>BB</sub>              | 14                   |                          |                                 | 3.67                     | 3.87                     |                          |                          | Vdc  |

| Logic '1' Output Voltage    | VOH1<br>(Note 1)             | 2<br>3               | 3.900<br>3.900           | 4.110<br>4.110                  | 4.000<br>4.000           | 4.190<br>4.190           | 4.070<br>4.070           | 4.300<br>4.300           | Vdc  |

|                             | VOH2                         | 7                    | 2.4                      |                                 | 2.6                      |                          | 2.8                      |                          | 1    |

| Logic '0' Output Voltage    | V <sub>OL1</sub><br>(Note 1) | 2<br>3               | 3.070<br>3.070           | 3.385<br>3.385                  | 3.110<br>3.110           | 3.410<br>3.410           | 3.135<br>3.135           | 3.445<br>3.445           | Vdc  |

|                             | V <sub>OL2</sub>             | 7                    |                          | 0.94                            |                          | 0.80                     |                          | 0.72                     | 1    |

| Logic '1' Threshold Voltage | V <sub>OHA</sub><br>(Note 2) | 2<br>3               | 3.880<br>3.880           |                                 | 3.980<br>3.980           |                          | 4.050<br>4.050           |                          | Vdc  |

| Logic '0' Threshold Voltage | V <sub>OLA</sub><br>(Note 3) | 2<br>3               |                          | 3.405<br>3.405                  |                          | 3.430<br>3.430           |                          | 3.465<br>3.465           | Vdc  |

| Short Circuit Current       | I <sub>OS</sub>              | 7                    | -65                      | -20                             | -65                      | -20                      | -65                      | -20                      | mAdc |

ground voltages must be maintained tested by sequencing an object in the during and between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock

VIHmax

VILmin

input is the waveform shown.

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50 Ω resistor to -2.0 V. Test procedures are shown for only one gate. The other gates are tested in the same manner.

|                             |                              |                      |                      | TEST V               | OLTAGE/CU            | JRRENT VAL           | UES     |              |                              |

|-----------------------------|------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------|--------------|------------------------------|

|                             |                              |                      |                      |                      | Volt                 | s                    |         |              | ]                            |

|                             | @ Test Temp                  | erature              | VIHmax               | VILmin               | VIHAmin              | V <sub>ILAmax</sub>  | VIH     | VILH         | ]                            |

|                             |                              | <b>−30°C</b>         | 4.110                | 3.070                | 3.795                | 3.500                | 2.4     | 0.5          | ]                            |

|                             |                              | 25°C                 | 4.190                | 3.110                | 3.895                | 3.525                | 2.4     | 0.5          | ]                            |

|                             |                              | 85°C                 | 4.300                | 3.135                | 3.965                | 3.560                | 2.4     | 0.5          | 1                            |

|                             |                              | Pin                  | TE                   | ST VOLTAGE           | APPLIED              | TO PINS LIS          | TED BEL | w            | ]                            |

| Characteristic              | Symbol                       | Under<br>Test        | V <sub>IHmax</sub>   | V <sub>ILmin</sub>   | V <sub>IHAmin</sub>  | V <sub>ILAmax</sub>  | VIH     | VIL          | (V <sub>EE</sub> )<br>Gnd    |

| Power Supply Drain Current  | ICC1                         | 8                    |                      |                      |                      |                      |         |              | 8                            |

|                             | ICC2                         | 6                    | 4                    | 5                    |                      |                      |         |              | 8                            |

| Input Current               | linH1                        | 15<br>11<br>12<br>13 | 15<br>11<br>12<br>13 |                      |                      |                      |         |              | 8<br>8<br>8<br>8             |

|                             | linH2                        | 4<br>5               | 5<br>5               | 4<br>4               |                      |                      |         |              | 8<br>8                       |

|                             | l <sub>inH3</sub>            | 5                    | 4                    | 5                    |                      |                      |         |              | 8                            |

|                             | linH4                        | 9<br>10              |                      |                      |                      |                      | 9<br>10 |              | 8<br>8                       |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13 |                      |                      |                      |                      |         |              | 8,15<br>8,11<br>8,12<br>8,13 |

|                             | linL2                        | 9<br>10              |                      |                      |                      |                      |         | 9<br>10      | 8<br>8                       |

| Reference Voltage           | V <sub>BB</sub>              | 14                   |                      |                      |                      |                      |         |              | 8                            |

| Logic '1' Output Voltage    | V <sub>OH1</sub><br>(Note 1) | 2<br>3               |                      | 11,12,13<br>11,12,13 |                      |                      |         | 9,10<br>9,10 | 8<br>8                       |

|                             | VOH2                         | 7                    | 5                    | 4                    |                      |                      |         |              | 8                            |

| Logic '0' Output Voltage    | VOL1<br>(Note 1)             | 2<br>3               |                      | 11,12,13<br>11,12,13 |                      |                      |         | 9,10<br>9,10 | 8<br>8                       |

|                             | V <sub>OL2</sub>             | 7                    | 4                    | 5                    |                      |                      |         |              | 8                            |

| Logic '1' Threshold Voltage | VOHA<br>(Note 2)             | 2<br>3               |                      |                      | 11,12,13<br>11,12,13 |                      |         |              | 8<br>8                       |

| Logic '0' Threshold Voltage | V <sub>OLA</sub><br>(Note 3) | 2<br>3               |                      |                      |                      | 11,12,13<br>11,12,13 |         |              | 8<br>8                       |

| Short Circuit Current       | los                          | 7                    | 5                    | 4                    |                      |                      |         | 7            | 8                            |

|                             |                              |                      |                      |                      |                      |                      |         |              |                              |

#### ELECTRICAL CHARACTERISTICS (continued) (Supply Voltage = 5.0 V, unless otherwise noted.)

NOTES: 1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and ground voltages must be maintained between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock

input is the waveform shown.

Clock Input VIHmax VILmin

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

|                             |                              |                      |                      | TEST V       | OLTAGE/Cl                            | JRRENT VA   | LUES     |       |                              |

|-----------------------------|------------------------------|----------------------|----------------------|--------------|--------------------------------------|-------------|----------|-------|------------------------------|

|                             |                              |                      |                      | Volts        |                                      |             | mA       |       | 1                            |

|                             | @ Test Temp                  | perature             | VIHT                 | VILT         | Vcc                                  | ١L          | IOL      | Іон   | 1                            |

|                             |                              | –30°C                | 2.0                  | 0.8          | 5.0                                  | -0.25       | 16       | -0.40 | 1                            |

|                             |                              | 25°C                 | 2.0                  | 0.8          | 5.0                                  | -0.25       | 16       | -0.40 | 1                            |

|                             |                              | 85°C                 | 2.0                  | 0.8          | 5.0                                  | -0.25       | 16       | -0.40 | 1                            |

|                             |                              | Pin                  | TE                   | ST VOLTAGE   |                                      | TO PINS LIS | STED BEL | ow    | 1                            |

| Characteristic              | Symbol                       | Under<br>Test        | VIHT                 | VILT         | V <sub>CC</sub>                      | ١L          | IOL      | ЮН    | (V <sub>EE</sub><br>Gnd      |

| Power Supply Drain Current  | ICC1                         | 8                    |                      |              | 1,16                                 |             |          |       | 8                            |

|                             | I <sub>CC2</sub>             | 6                    |                      |              | 6                                    |             |          |       | 8                            |

| Input Current               | linH1                        | 15<br>11<br>12<br>13 | 9,10<br>9,10<br>9,10 |              | 1,16<br>1,16<br>1,16<br>1,16<br>1,16 |             |          |       | 8<br>8<br>8<br>8             |

|                             | linH2                        | 4<br>5               |                      |              | 6<br>6                               |             |          |       | 8<br>8                       |

|                             | l <sub>inH3</sub>            | 5                    |                      |              | 6                                    |             |          |       | 8                            |

|                             | linH4                        | 9<br>10              |                      |              | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

| Leakage Current             | linL1                        | 15<br>11<br>12<br>13 |                      |              | 1,16<br>1,16<br>1,16<br>1,16<br>1,16 |             |          |       | 8,15<br>8,11<br>8,12<br>8,13 |

|                             | linL2                        | 9<br>10              |                      |              | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

| Reference Voltage           | V <sub>BB</sub>              | 14                   |                      |              | 1,16                                 | 14          |          |       | 8                            |

| Logic '1' Output Voltage    | VOH1<br>(Note 1)             | 2<br>3               |                      |              | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

|                             | V <sub>OH2</sub>             | 7                    |                      |              | 6                                    |             |          | 7     | 8                            |

| Logic '0' Output Voltage    | VOL1<br>(Note 1)             | 2<br>3               |                      |              | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

|                             | V <sub>OL2</sub>             | 7                    |                      |              | 6                                    |             | 7        |       | 8                            |

| Logic '1' Threshold Voltage | VOHA<br>(Note 2)             | 2<br>3               | 9,10<br>9,10         |              | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

| Logic '0' Threshold Voltage | V <sub>OLA</sub><br>(Note 3) | 2<br>3               |                      | 9,10<br>9,10 | 1,16<br>1,16                         |             |          |       | 8<br>8                       |

| Short Circuit Current       | los                          | 7                    |                      |              | 6                                    |             |          | 1     | 8                            |

#### ELECTRICAL CHARACTERISTICS (continued) (Supply Voltage = 5.0 V, unless otherwise noted.)

NOTES: 1. Test outputs of the device must be tested by sequencing through the truth table. All input, power supply and

ground voltages must be maintained between tests. The clock input is the waveform shown. 2. In addition to meeting the output levels specified, the device must divide by 5 or 8 during this test. The clock input is the waveform shown. Clock Input

VIHmax

VILmin

3. In addition to meeting the output levels specified, the device must divide by 6 or 9 during this test. The clock input is the waveform shown.

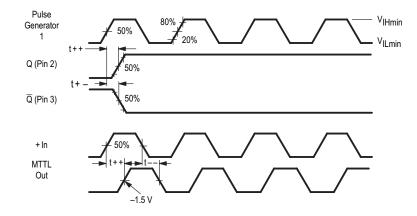

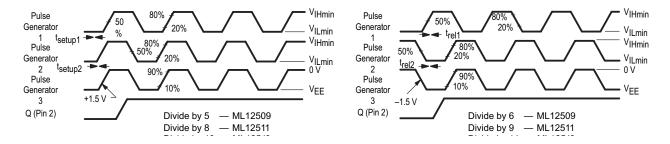

#### SWITCHING CHARACTERISTICS

|                                                                      |                                                                                        | Pin              |             | ML12509, ML12511, ML12513 |                          |            |      |                          |            |      |                          | TEST VOLTAGES/WAVEFORMS APPLIED TO PINS LISTED E |                    |        |       |          |                                | BELOW:            |             |                                      |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|-------------|---------------------------|--------------------------|------------|------|--------------------------|------------|------|--------------------------|--------------------------------------------------|--------------------|--------|-------|----------|--------------------------------|-------------------|-------------|--------------------------------------|

|                                                                      |                                                                                        | Under            |             | –30°C                     |                          |            | 25°C |                          |            | 85°C |                          |                                                  | Pulse              | Pulse  | Pulse | VIHmin   | VILmin                         | VF                | VEE         | Vcc                                  |

| Characteristic                                                       | Symbol                                                                                 | Test             | Min         | Тур                       | Max                      | Min        | Тур  | Max                      | Min        | Тур  | Max                      | Unit                                             | Gen.1              | Gen.2  | Gen.3 | †        | †                              | -3.0 V            | -3.0 V      | +2.0                                 |

| Propagation Delay<br>(See Figures 3 and 5)                           | t <sub>15+ 2+</sub><br>t <sub>15+ 2-</sub><br>t <sub>5+ 7+</sub><br>t <sub>5- 7-</sub> | 2<br>2<br>7<br>7 | -<br>-<br>- |                           | 8.1<br>7.5<br>8.4<br>6.5 |            |      | 8.1<br>7.5<br>8.1<br>6.5 |            |      | 8.9<br>8 2<br>8.9<br>7.1 | ns<br>                                           | 15<br>15<br>A<br>A | <br>   | <br>  |          | 11,12,13<br>11,12,13<br>—<br>— | 9,10<br>9,10<br>— | 8<br>8<br>8 | 1,6,16<br>1,6,16<br>1,6,16<br>1,6,16 |

| Setup Time<br>(See Figures 4 and 5)                                  | t <sub>setup1</sub><br>t <sub>setup2</sub>                                             | 11<br>9          | 5.0<br>5.0  | _                         | _                        | 5.0<br>5.0 | _    | _                        | 5.0<br>5.0 | _    | _                        | ns<br>ns                                         | 15<br>15           | *<br>_ | -     | =        | *<br>11,12,13                  | 9,10<br>*         | 8<br>8      | 1,6,16<br>1,6,16                     |

| Release Time<br>(See Figures 4 and 5)                                | t <sub>rel1</sub><br>t <sub>rel2</sub>                                                 | 11<br>9          | 5.0<br>5.0  | _                         | _                        | 5.0<br>5.0 | _    | _                        | 5.0<br>5.0 | _    | _                        | ns<br>ns                                         | 15<br>15           | *<br>_ | •     | _        | *<br>11,12,13                  | 9.10<br>*         | 8<br>8      | 1,6,16<br>1,6,16                     |

| Toggle Frequency<br>(See Figure 6)<br>ML12509 : 5/6<br>ML12511 : 8/9 | f <sub>max</sub>                                                                       | 2                | 440<br>500  | _                         | _                        | 480<br>550 |      |                          | 440<br>500 |      |                          | MHz                                              |                    |        |       | 11<br>11 |                                |                   | 8<br>8      | 16<br>16                             |

\*Test inputs sequentially, with Pulse Generator 2 or 3 as indicated connected to input under test, and the voltage indicated applied to the other input(s) of the same type (i.e., MECL or MTTL).

|                     | -30°C | 25°C  | 85°C  |     |

|---------------------|-------|-------|-------|-----|

| †V <sub>IHmin</sub> | 1.03  | 1.115 | 1.20  | Vdc |

| †V <sub>ILmin</sub> | 0.175 | 0.200 | 0.235 | Vdc |

#### Figure 3. AC Voltage Waveforms

# Figure 4. Setup and Release Time Waveforms

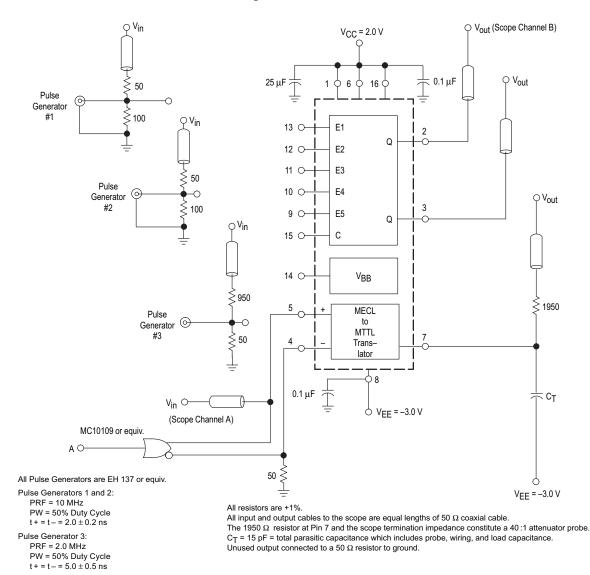

#### Figure 5. AC Test Circuit

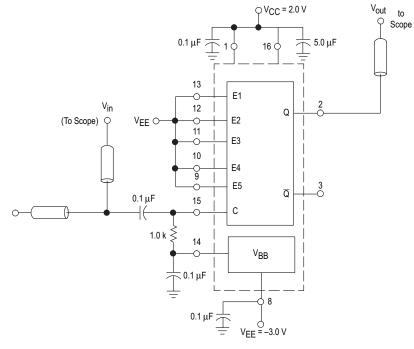

# Figure 6. Maximum Frequency Test Circuit

Unused output connected to a 50  $\Omega$  resistor to ground

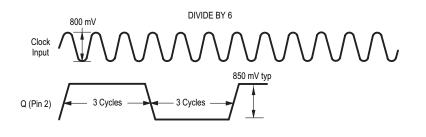

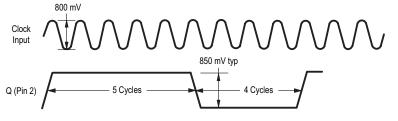

DIVIDE BY 9

#### Figure 7. State Diagram

DIVIDE BY 5/6 (ML12009/ML12509)

#### **APPLICATIONS INFORMATION**

The primary application of these devices is as a high–speed variable modulus prescaler in the divide by N section of a phase–locked loop synthesizer used as the local oscillator of two–way radios.

Proper VHF termination techniques should be followed when the clock is separated from the prescaler by any appreciable distance. In their basic form, these devices will divide by 5/6 or 8/9. Division by 5, or 8 occurs when any one or all of the five gate inputs E1 through E5 are high. Division by 6, or 9 occurs when all inputs E1 through E5 are low. (Unconnected MTTL inputs are normally high, unconnected MECL inputs are normally low). With the addition of extra parts, many different division configurations may be obtained.

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.

www.lansdale.com