July 2007

# FHP3392 — Fixed-Gain, ±5V, Triple 2:1, High-Speed Video Multiplexer

## **Features**

- 0.1dB gain flatness to 102MHz at 2V<sub>PP</sub>

- 9ns channel switching time

- <0.02%/0.03° differential gain/phase error</p>

- 750MHz large signal -3dB bandwidth

- 2,600V/µs slew rate

- 60mA output current (easily drives two video loads)

- 70dB channel to channel isolation

- 25mA supply current

- 7mA supply current when disabled

- Fully specified at ±5V supplies

- Lead-free TSSOP-24 package

## **Applications**

- RGB video switchers and routers

- Multiple input HDTV switching

- Picture-in-picture video switch

- Multi-channel ADC Driver

## **Description**

The FHP3392 (G=2) is a triple 2:1 analog multiplexer designed for high-speed video applications. The output amplifiers offer a fixed gain of 6dB and stellar large signal performance of 335MHz -3dB bandwidth and 80MHz 0.1dB bandwidth. The  $2V_{PP}$  bandwidth performance and 1,600V/ $\mu s$  slew rate exceed the requirements of high-definition television (HDTV) and other multimedia applications. The output amplifier provides ample output current to drive multiple video loads.

The FHP3392 may be operated with dual power supplies from  $\pm 2.5 \text{V}$  to  $\pm 6 \text{V}$ .

The FHP3392 consumes only 25mA of supply current and offer disable capability. While disabled, it consumes only 7mA and the outputs become high impedance, allowing multiplexer expansion with multiple FHP3392s.

# **Ordering Information**

| Part Number    | Pb-<br>Free | Gain | Operating Temperature Range | Package                                                             | Packing<br>Method |

|----------------|-------------|------|-----------------------------|---------------------------------------------------------------------|-------------------|

| FHP3392IMTC24X | Yes         | 6dB  | -40°C to +85°C              | 24-Lead,Thin Shrink Outline<br>Package, JEDEC MO-153, 4.4mm<br>Wide | Tape and Reel     |

Moisture sensitivity level for all parts is MSL-1.

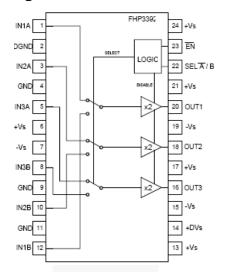

# **Block Diagram and Pin Configuration**

Figure 1. Block Diagram and Pin Configuration

## **Pin Definitions**

| Pin# | Name            | Description                                                                   |

|------|-----------------|-------------------------------------------------------------------------------|

| 1    | IN1A            | 1st Input Channel A                                                           |

| 2    | DGND            | Digital Ground, must be connected to ground                                   |

| 3    | IN2A            | 2nd Input Channel A                                                           |

| 4    | GND             | Must be connected to ground                                                   |

| 5    | 1N3A            | 3rd Input Channel A                                                           |

| 6    | +Vs             | Positive supply                                                               |

| 7    | -Vs             | Negative supply                                                               |

| 8    | IN3B            | 3rd Input Channel B                                                           |

| 9    | GND             | Must be connected to ground                                                   |

| 10   | IN2B            | 2nd Input Channel B                                                           |

| 11   | GND             | Must be connected to ground                                                   |

| 12   | IN1B            | 1st Input Channel B                                                           |

| 13   | +V <sub>S</sub> | Positive supply                                                               |

| 14   | +DVs            | Digital positive supply                                                       |

| 15   | -V <sub>S</sub> | Negative supply                                                               |

| 16   | OUT3            | 3rd output                                                                    |

| 17   | +Vs             | Positive supply                                                               |

| 18   | OUT3            | 2nd output                                                                    |

| 19   | -Vs             | Negative supply                                                               |

| 20   | OUT1            | 1st Output                                                                    |

| 21   | +V <sub>S</sub> | Logic input; "0" = Channel A, "1" = Channel B                                 |

| 22   | SEL A/B         | Enable pin; "0" = Enable, "1" = Disable; Enabled if left floating or grounded |

| 23   | EN              | Enable Pin: "0" = Channel A, "1" = Channel B                                  |

| 24   | +V <sub>S</sub> | Positive supply                                                               |

# **Truth Table**

| SELĀ/B | EN | OUT       |

|--------|----|-----------|

| 0      | 0  | Channel A |

| 1      | 0  | Channel B |

| X      | 1  | Disable   |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol          | Parameter           | Min.                  | Max.                   | Unit |

|-----------------|---------------------|-----------------------|------------------------|------|

| V <sub>CC</sub> | Supply Voltage      | 0                     | 13.3                   | V    |

| V <sub>IN</sub> | Input Voltage Range | -V <sub>S</sub> – 0.5 | +V <sub>S</sub> + 0.5V | V    |

## **Electrostatic Discharge Protection**

| Symbol                        | Parameter              | Min. | Max. | Unit |

|-------------------------------|------------------------|------|------|------|

| ESD                           | Human Body Model (HBM) |      | 3    | kV   |

| Charged Device Model (CDM) 12 |                        | 12   | kV   |      |

# **Reliability Information**

| Symbol            | Parameter            | Min. | Тур. | Max. | Unit |

|-------------------|----------------------|------|------|------|------|

| $T_J$             | Junction Temperature |      |      | 150  | °C   |

| T <sub>STG</sub>  | Storage Temperature  | -65  |      | 150  | °C   |

| T <sub>RF</sub>   | Reflow Temperature   |      |      | 260  | °C   |

| $\theta_{\sf JA}$ | Thermal Resistance   |      | 87   |      | °C/W |

## Note:

1. Thermal Resistance ( $\theta_{JA}$ ) JEDEC standard, multi-layer test boards, in still air.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                   | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------------|------|------|------|------|

| T <sub>A</sub>  | Operating Temperature Range | -40  |      | +85  | °C   |

| V <sub>CC</sub> | Supply Voltage Range        | ±2.5 | ±5.0 | ±6.0 | V    |

## Electrical Characteristics at ±5V

$T_A$  = 25°C,  $V_S$  = ± 5V,  $R_L$  = 150 $\Omega$ ; unless otherwise noted.

| Symbol                | Parameter                                      | Conditions                                                | Min. | Тур. | Max. | Units     |  |

|-----------------------|------------------------------------------------|-----------------------------------------------------------|------|------|------|-----------|--|

| Frequency             | Domain Response                                |                                                           |      |      |      |           |  |

| BWss                  | -3dB Bandwidth                                 | V <sub>OUT</sub> = 0.2V <sub>PP</sub>                     |      | 750  |      | MHz       |  |

| BW <sub>LS</sub>      | Large Signal Bandwidth                         | $V_{OUT} = 2.0V_{PP}$                                     |      | 560  |      | MHz       |  |

| BW <sub>0.1dBSS</sub> | 0.1dB Gain Flatness                            | $V_{OUT} = 0.2V_{PP}$                                     |      | 117  |      | MHz       |  |

| BW <sub>0.1dBLS</sub> | 0.1dB Gain Flatness                            | V <sub>OUT</sub> = 2.0V <sub>PP</sub>                     |      | 102  |      | MHz       |  |

| Time Doma             | nin Response                                   |                                                           |      |      |      |           |  |

| ts                    | Settling Time to 0.1%                          | V <sub>OUT</sub> = 2V step                                |      | 4    |      | ns        |  |

| SR                    | Slew Rate                                      | 4V step                                                   |      | 2600 |      | V/µs      |  |

| Distortion /          | Noise Response                                 |                                                           |      |      | •    | •         |  |

| HD2                   | Second Harmonic Distortion                     | 2V <sub>PP</sub> , 5MHz                                   |      | -85  |      | dBc       |  |

| HD3                   | Third Harmonic Distortion                      | 2V <sub>PP,</sub> 5MHz                                    |      | -90  |      | dBc       |  |

| TUD                   | Total Harmania Distantian                      | 2V <sub>PP</sub> , 5MHz                                   |      | -84  |      | dB        |  |

| THD                   | Total Harmonic Distortion                      | 2V <sub>PP</sub> , 22MHz                                  |      | -72  |      | dB        |  |

| DG                    | Differential Gain                              | NTSC (3.58MHz)                                            |      | 0.04 |      | %         |  |

| DP                    | Differential Phase                             | NTSC (3.58MHz)                                            |      | 0.01 |      | 0         |  |

| e <sub>n</sub>        | Input Voltage Noise                            | >1MHz                                                     |      | 6.75 |      | nV/Hz     |  |

| i <sub>n</sub>        | Input Current Noise                            | >1MHz                                                     |      | 22   |      | pA/Hz     |  |

| SNR                   | Signal-to-Noise Ratio                          | NTC-7 weighting,<br>4.2MHz LP filter,<br>100kHz PH filter |      | 90   |      | dB        |  |

| $X_{talk}$            | All Hostile Crosstalk                          | V <sub>OUT</sub> = 2V <sub>PP</sub> , ch-to-ch,<br>5MHz   |      | -59  |      | dB        |  |

| ∧talk                 | All Hostile Glosstalk                          | V <sub>OUT</sub> = 2V <sub>PP</sub> , ch-to-ch, 30MHz     |      | -56  |      | UB        |  |

| DC Perforn            | nance                                          |                                                           |      |      |      |           |  |

| Vos                   | Output Offset Voltage <sup>(2)</sup>           | V <sub>IN</sub> = 0                                       | -18  | 2    | 18   | mV        |  |

| I <sub>b</sub>        | Input Bias Current <sup>(2)</sup>              |                                                           | -30  | 4    | 30   | μA        |  |

| G                     | Gain <sup>(2)</sup>                            | DC                                                        | 1.9  | 2.0  | 2.1  | V/V       |  |

| GM                    | Gain Matching                                  | Channel-to-channel, DC                                    |      | 0.05 | /    | %         |  |

| PSRR                  | Power Supply Rejection Ratio <sup>(2)</sup>    | DC, V <sub>CM</sub> = 0, input referred, SEL = X          | 54   | 62   |      | dB        |  |

| $I_S$                 | Supply Current <sup>(2)</sup>                  | No load, $\overline{EN} = 0$                              |      | 25   | 30   | mA        |  |

| I <sub>EN</sub>       | Disable Supply Current <sup>(2)</sup>          | EN = 1                                                    |      | 7    | 10   | mA        |  |

| Switching             | Characteristics                                |                                                           |      |      |      |           |  |

|                       | Switching Time 50% Logic to:                   | Channel-to channel                                        |      |      |      |           |  |

| Ts                    | 90% Output (10% Output Setting) <sup>(3)</sup> | Ch A inputs = +0.5V<br>Ch B inputs = -0.5V                |      | 17.3 |      | ns        |  |

|                       | 99% Output (1% Output Setting) <sup>(3)</sup>  | Ch A inputs = +0.5V<br>Ch B inputs = -0.5V                |      | 36   |      | ns        |  |

| $V_{SW}$              | Channel Switching Transient (Glitch)           | All inputs grounded                                       |      | 34   |      | $mV_{PP}$ |  |

## Notes:

- 100% tested at 25°.

- 2. 3. EN pin is grounded, channel A inputs = 0.5V, channel B inputs = -0.5V. Switching time is the transition time from 50% of SEL input value (+2.5V) to the time at which the switched channel is at 90% (or 99%) of its final value.

# Electrical Characteristics at ±5V (Continued)

$T_A$  = 25°C,  $V_S$  = ± 5V,  $R_L$  = 150 $\Omega$ ; unless otherwise noted.

| Symbol             | Parameter Conditions           |                                             | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------|---------------------------------------------|------|------|------|-------|

| Digital Inpu       | uts                            | <u>.</u>                                    |      | •    |      |       |

| V <sub>IH</sub>    | Logic HIGH Threshold           | SEL and EN pins <sup>(4)</sup>              | 2.0  |      |      | V     |

| V <sub>IL</sub>    | Logic LOW Threshold            | SEL and EN pins <sup>(4)</sup>              |      |      | 0.8  | V     |

| I <sub>IH</sub>    | Logic Pin Input Current HIGH   | SEL and EN pins;<br>Logic Input = 2V        |      | 27   |      | μΑ    |

| I <sub>IL</sub>    | Logic Pin Input Current LOW    | SEL and EN pins;<br>Logic Input = 0V        |      | 0    |      | μA    |

| Disable Ch         | aracteristics                  |                                             |      |      |      |       |

| <b>⊏N</b> I        | Disable legistics              | $\frac{5MHz, V_{IN} = 1V_{PP},}{EN = 1}$    |      | -81  |      | dB    |

| EN <sub>ISO</sub>  | Disable Isolation              | $30MHz$ , $V_{IN} = 1V_{PP}$ , $EN = 1$     |      | -66  |      | dB    |

| CH <sub>ISO</sub>  | Channel-to-Channel Isolation   | 5MHz                                        |      | -71  |      | dB    |

| ENT <sub>ON</sub>  | Turn-on-Time (Disable to ON)   | V <sub>IN</sub> = 0.5V                      |      | 30   |      | ns    |

| ENT <sub>OFF</sub> | Turn-off-Time (ON to Disable)  | V <sub>IN</sub> = 0.5V                      |      | 65   |      | ns    |

| Input Char         | acteristics                    |                                             |      |      |      |       |

| R <sub>IN</sub>    | Input Resistance               |                                             |      | 115  |      | kΩ    |

| C <sub>IN</sub>    | Input Capacitance              |                                             |      | 10   |      | pF    |

| V <sub>IN</sub>    | Input Voltage Range            |                                             |      | ±2   |      | V     |

| Output Cha         | aracteristics                  |                                             |      |      |      |       |

| .,,                | 0.10.13/18/19/19               | $R_L = 2k\Omega$                            |      | ±4   |      | V     |

| Vo                 | Output Voltage Swing           | $R_L = 150\Omega^{(4)}$                     | ±3.2 | ±3.7 |      | V     |

| l <sub>out</sub>   | Linear Output Current          |                                             |      | ±95  |      | mA    |

| I <sub>SC</sub>    | Short Circuit Output Current   | V <sub>O</sub> = GND                        |      | ±100 |      | mA    |

| D                  | Output Desistance Classed Lean | Enabled, $\overline{\text{EN}}$ = 1, 100kHz |      | 0.17 |      | Ω     |

| R <sub>out</sub>   | Output Resistance, Closed Loop | Disabled, EN = 1,<br>100kHz                 |      | 675  |      | Ω     |

| C <sub>OUT</sub>   | Output Capacitance             | Disabled, EN = 1,<br>100kHz                 |      | 2.7  |      | pF    |

## Note:

4. 100% tested at 25°.

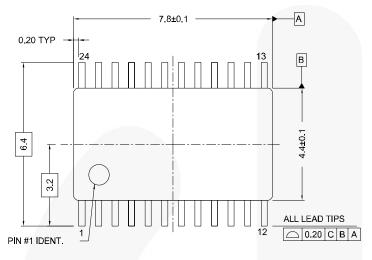

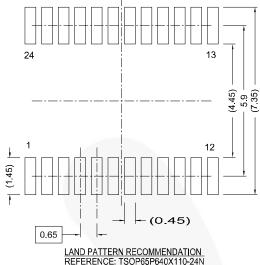

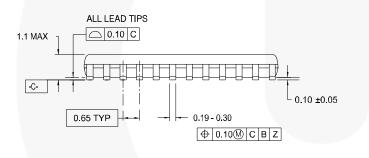

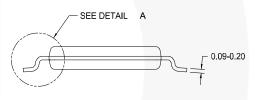

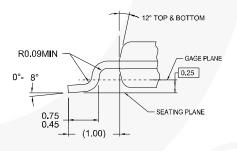

# **Physical Dimensions**

Dimensions are in millimeters unless otherwise noted.

**DIMENSIONS ARE IN MILLIMETERS**

## NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AD, DATE 10/97.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1994

- E. DRAWING FILE NAME: MTC24REV4

## MTC24REV4

DETAIL A

Figure 2. 24-Lead, Thin Shrink Outline Package, JEDEC MO-153, 4.4mm Wide

#### TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx® Build it Now™ CorePLUS™ CROSSVOLT™ CTL™

Current Transfer Logic™ EcoSPARK®

Fairchild<sup>®</sup>

Fairchild Semiconductor® FACT Quiet Series™ FACT®

FAST® FastvCore™ FPS™ FRFET®

Global Power Resource<sup>SM</sup>

Green FPS™

Green FPS™ e-Series™

GTO™ i-Lo™ IntelliMAX™ ISOPLANAR™ MegaBuck™

MICROCOUPLER™ MicroFET™ MicroPak™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

PDP-SPM™ Power220®

Power247® POWEREDGE® Power-SPM™

PowerTrench® Programmable Active Droop™

QT Optoelectronics™

QFET® QSTM

> Quiet Series™ RapidConfigure ™ SMART START™ SPM® STEALTH™ SuperFET™

SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SyncFET™

The Power Franchise®

p wer TinyBoost™ TinyBuck™ TinyLogic<sup>®</sup> TINYOPTO™ TinvPower™ TinyPWM™ TinyWire™

µSerDes™ UHC® UniFET™ VCX™

## DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS **Definition of Terms**

| Datasheet Identification Product Status |                        | Definition                                                                                                                                                                                               |  |  |

|-----------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                     | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary                             | First Production       | This datasheet contains preliminary data, supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

|                                         |                        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |  |  |

| Obsolete                                | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                      |  |  |

Rev. 130