March 2006 Advance Information

# FHP3194 4:1 High Speed Multiplexer

### Features at ±5V

- 0.1dB gain flatness to 155MHz

- 7.5ns channel switching time

- 0.02%/0.03° differential gain/phase error

- 335MHz full power -3dB bandwidth at G=2

- 1600V/µs slew rate

- 60mA output current (easily drives three video loads)

- 70dB channel to channel isolation

- 13mA supply current

- 4mA supply current in disable mode

- 3mA supply current in shutdown mode

- Fully specified at ±5V supplies

- Lead (Pb) free SOIC-14 and TSSOP-14 packages

## Applications

- Video switchers and routers

- Multiple Input HDTV switching

- Picture in picture video switch

- Multi-channel ADC Driver

## Description

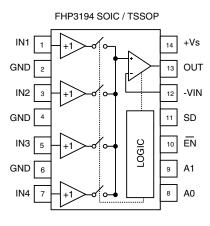

The FHP3194 is a 4:1 analog multiplexer designed for high speed video applications. The output amplifier is a high-speed current feedback amplifier that offers stellar large signal performance of 335MHz -3dB bandwidth and 80MHz 0.1dB bandwidth. The gain of the output amplifier is selectable thru 2 external resistors (R<sub>f</sub> and R<sub>q</sub>), allowing further flexibility. The  $2V_{\text{pp}}$  bandwidth performance, 1600V/µs slew rate, and 0.02% / 0.03° differential gain and phase exceed the requirements of high definition television (HDTV) and other multimedia applications. The output amplifier also provides ample output current to drive multiple video loads.

Two address bits (A0 and A1) are used to select one of the four buffered inputs. The FHP3194 offers excellent 7.5ns switching times and better than 70dB channel isolation.

The FHP3194 offers both shutdown and disable capability. During shutdown, the FHP3194 consumes only 3mA of supply current and provides maximum input to output isolation. During disable mode, only the output amplifier is disabled reducing output glitches and allowing for multiplexer expansion.

### **Functional Block Diagram**

### **Ordering Information**

| Part Number    | Package  | Pb-Free | Operating Temperature<br>Range | Packing<br>Method |

|----------------|----------|---------|--------------------------------|-------------------|

| FHP3194IM14X   | SOIC-14  | Yes     | -40°C to +85°C                 | Reel              |

| FHP3194IMTC14X | TSSOP-14 | Yes     | -40°C to +85°C                 | Reel              |

Moisture sensitivity level for all parts is MSL-1.

FHP3194 Rev. 1.0.6

#### www.fairchildsemi.com ©2005 Fairchild Semiconductor Corporation

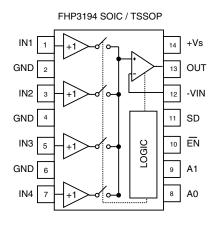

## **Pin Configurations**

### **Pin Assignments**

| Pin# | Pin  | Description                                |

|------|------|--------------------------------------------|

| 1    | IN1  | Input, Channel 1                           |

| 2    | GND  | Must be connected to ground                |

| 3    | IN2  | Input, Channel 2                           |

| 4    | GND  | Must be connected to ground                |

| 5    | IN3  | Input, Channel 3                           |

| 6    | -Vs  | Negative Supply                            |

| 7    | IN4  | Input, Channel 4                           |

| 8    | A0   | Logic Input A0                             |

| 9    | A1   | Logic Input A1                             |

| 10   | EN   | Enable pin, "1" = Disable, "0" = Enable    |

| 11   | SD   | Shutdown pin, "1" = Shutdown, "0" = Active |

| 12   | -VIN | Inverting Input of output amplifier        |

| 13   | OUT  | Output                                     |

| 14   | +Vs  | Positive Supply                            |

### **Truth Table**

| A0 | A1 | EN | SD | OUT      |

|----|----|----|----|----------|

| 1  | 1  | 0  | 0  | CH4      |

| 0  | 1  | 0  | 0  | CH3      |

| 1  | 0  | 0  | 0  | CH2      |

| 0  | 0  | 0  | 0  | CH1      |

| Х  | Х  | 1  | 0  | Disable  |

| Х  | Х  | Х  | 1  | Shutdown |

## **Absolute Maximum Ratings**

The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

| Symbol         | Parameter           | Min                    | Max             | Unit |

|----------------|---------------------|------------------------|-----------------|------|

| V <sub>s</sub> | Supply Voltage      | 0                      | 12.6            | V    |

| CMIR           | Input Voltage Range | -V <sub>s</sub> - 0.5V | $+V_{s} + 0.5V$ | V    |

### **Recommended Operating Conditions**

| Symbol         | Parameter                   | Min | Тур | Мах | Unit |

|----------------|-----------------------------|-----|-----|-----|------|

| T <sub>c</sub> | Operating Temperature Range | -40 |     | +85 | °C   |

| Vs             | Supply Voltage Range        | 5   |     | 12  | V    |

### **Reliability Information**

| Parameter                         | Min | Тур | Max | Unit |

|-----------------------------------|-----|-----|-----|------|

| Junction Temperature              |     |     | 150 | °C   |

| Storage Temperature Range         | -65 |     | 150 | °C   |

| Lead Temperature (Soldering, 10s) |     |     | 300 | °C   |

| 14-Lead SOIC <sup>1</sup>         |     | 128 |     | °C/W |

| 14-Lead TSSOP <sup>1</sup>        |     | 130 |     | °C/W |

Note:

1. Package thermal resistance ( $\Theta$ JA), JDEC standard, multi-layer test boards, still air.

## **ESD** Protection

| Package                   | SOIC-14 | TSSOP-14 |

|---------------------------|---------|----------|

| Human Body Model (HBM)    | TBD     | TBD      |

| Charge Device Model (CDM) | TBD     | TBD      |

### Electrical Characteristics at ±5V

$T_c$  = 25°C,  $V_s$  =  $\pm$  5V,  $R_f$  = 499 $\Omega,$   $R_L$  = 150 $\Omega,$  G = 2; unless otherwise noted.

| Symbol                          | Parameter                                     | Conditions                                | Min | Тур       | Max | Units            |

|---------------------------------|-----------------------------------------------|-------------------------------------------|-----|-----------|-----|------------------|

|                                 | Frequency Domain Response                     |                                           |     |           |     |                  |

| UGBW                            | -3dB Bandwidth                                | $G = +1, V_{OUT} = 0.2V_{pp}$             |     | TBD       |     | MHz              |

| BW <sub>ss</sub>                | -3dB Bandwidth                                | No Peaking, G = +2, $V_{OUT} = 0.2V_{pp}$ |     | 380       |     | MHz              |

| BW <sub>Ls</sub>                | Full Power Bandwidth                          | No Peaking, G = +2, $V_{OUT} = 2V_{pp}$   |     | 335       |     | MHz              |

| BW <sub>0.1dBSS</sub>           | 0.1dB Gain Flatness                           | $G = +2, V_{OUT} = 0.2V_{pp}$             |     | 155       |     | MHz              |

| BW <sub>0.1dBLS</sub>           | 0.1dB Gain Flatness                           | $G = +2, V_{OUT} = 2V_{pp}$               |     | 80        |     | MHz              |

|                                 | Time Domain Response                          |                                           |     |           |     |                  |

| t <sub>R</sub> , t <sub>F</sub> | Rise and Fall Time                            | V <sub>OUT</sub> = 2V step; (10% to 90%)  |     | 1         |     | ns               |

| t <sub>S</sub>                  | Settling Time to 0.1%                         | V <sub>OUT</sub> = 2V step                |     | 15        |     | ns               |

| OS                              | Overshoot                                     | V <sub>OUT</sub> = 0.2V step              |     | 5.7       |     | %                |

| SR                              | Slew Rate                                     | 4V step. G = -1                           |     | 1600      |     | V/µs             |

|                                 | Distortion / Noise Response                   |                                           |     |           |     |                  |

| HD2                             | 2nd Harmonic Distortion                       | 2V <sub>pp</sub> , 5MHz                   |     | -70       |     | dBc              |

| HD3                             | 3rd Harmonic Distortion                       | 2V <sub>pp</sub> , 5MHz                   |     | -79       |     | dBc              |

| THD                             | Total Harmonic Distortion                     | 2V <sub>pp</sub> , 5MHz                   |     | -81       |     | dB               |

| DG                              | Differential Gain                             | NTSC (3.58MHz)                            |     | 0.02      |     | %                |

| DP                              | Differenital Phase                            | NTSC (3.58MHz)                            |     | 0.03      |     | 0                |

| e <sub>n</sub>                  | Input Voltage Noise                           | > 1MHz                                    |     | 7         |     | nV/Hz            |

| i <sub>n+</sub>                 | Input Current Noise (+)                       | > 1MHz                                    |     | 22        |     | pA/Hz            |

| i <sub>n-</sub>                 | Input Current Noise (-)                       | > 1MHz                                    |     | 16        |     | pA/Hz            |

| X <sub>TALK</sub>               | All Hostile Crosstalk                         | Channel-to-channel 5MHz/30MHz             |     | -85 / -65 |     | dB               |

|                                 | DC Performance                                |                                           |     |           |     |                  |

| V <sub>IO</sub>                 | Input Offset Voltage <sup>1</sup>             |                                           | -9  | 1         | +9  | mV               |

| dV <sub>IO</sub>                | Average Drift                                 |                                           |     | 8.5       |     | μV/°C            |

| V <sub>IOM</sub>                | Input Offset Voltage Matching <sup>1</sup>    | Channel to channel                        | -5  | TBD       | 5   | mV               |

| I <sub>bn</sub>                 | Input Bias Current non-inverting <sup>1</sup> | Pins 1,3,5,7                              | -16 | 4         | 16  | μA               |

| dl <sub>bn</sub>                | Average Drift                                 |                                           |     | 16        |     | nA/°C            |

| I <sub>bi</sub>                 | Input Bias Current inverting <sup>1</sup>     | Pin 12                                    | -20 | 13        | 20  | μA               |

| dl <sub>bn</sub>                | Average Drift                                 |                                           |     | 85        |     | nA/°C            |

| GM                              | Gain Matching                                 | Channel-to-channel                        |     | 0.05      |     | %                |

| PSRR                            | Power Supply Rejection Ratio <sup>1</sup>     | DC                                        | 54  | 60        |     | dB               |

| I <sub>S</sub>                  | Supply Current <sup>1</sup>                   |                                           |     | 13        | 18  | mA               |

| I <sub>EN</sub>                 | Disable Supply Current <sup>1</sup>           | Disable Mode                              |     | 4         | 6   | mA               |

| I <sub>SD</sub>                 | Shutdown Supply Current <sup>1</sup>          | Shutdown Mode                             |     | 3         | 5   | mA               |

|                                 | Switching Characteristics                     |                                           |     |           |     |                  |

|                                 | Switching Time                                | Channel-to-Channel                        |     |           |     |                  |

|                                 | 50% Logic to 10% Output Settling              | IN0, IN2 = +0.5V; IN1, IN3 = -0.5V        |     | 7.5       |     | ns               |

|                                 | 50% Logic to 10% Output Settling              | IN0, IN2 = +0.5V; IN1, IN3 = -0.5V        |     | 9.1       |     | ns               |

|                                 | 50% Logic to 10% Output Settling              | IN0, IN2 = +0.5V; IN1, IN3 = -0.5V        |     | 25        |     | ns               |

|                                 | Channel Switching Transient (Glitch)          | All inputs grounded                       |     | 104       |     | mV <sub>pp</sub> |

### Notes:

1. 100% tested at 25°C

### Electrical Characteristics at ±5V continued

| Symbol             | Parameter                                | Conditions                                  | Min  | Тур       | Max  | Units |

|--------------------|------------------------------------------|---------------------------------------------|------|-----------|------|-------|

|                    | Digital Inputs                           |                                             |      |           |      |       |

| V <sub>IH</sub>    | Logic High Threshold                     | A0, A1, EN, and SD pins                     | 2.0  |           |      | V     |

| V <sub>IL</sub>    | Logic Low Threshold                      | A0, A1, EN, and SD pins                     |      |           | 0.08 | V     |

| I <sub>IH</sub>    | Logic Pin Input Current High             | A0, A1, EN, and SD pins; Logic Input = 2.0V |      | TBD       |      | μA    |

| IIL                | Logic Pin Input Current Low              | A0, A1, EN, and SD pins; Logic Input = 0V   |      | TBD       |      | μΑ    |

|                    | Disable Characteristics                  |                                             |      |           |      |       |

| ENISO              | Disable Isolation                        | 5MHz / 30MHz                                |      | -88 / -72 |      | dB    |

| SD <sub>ISO</sub>  | Shutdown Isolation                       | 5MHz / 30MHz                                |      | -92 /-77  |      | dB    |

| CH <sub>ISO</sub>  | Channel-to-Channel Isolation             | 5MHz                                        |      | -70       |      | dB    |

| ENT <sub>ON</sub>  | Turn on time (Disable to ON)             |                                             |      | 17        |      | ns    |

| ENT <sub>OFF</sub> | Turn off time (ON to Disable)            |                                             |      | 120       |      | ns    |

| SDT <sub>ON</sub>  | Turn on time (Shutdown to ON)            |                                             |      | 20        |      | ns    |

| SDT <sub>OFF</sub> | Turn off time (On to Shutdown)           |                                             |      | 115       |      | ns    |

|                    | Input Characteristics                    |                                             |      |           |      |       |

| R <sub>IN</sub>    | Input Resistance                         |                                             |      | TBD       |      | MΩ    |

| C <sub>IN</sub>    | Input Capacitance                        |                                             |      | TBD       |      | pF    |

| CMIR               | Input Common Mode Voltage Range          |                                             |      | ±2.8      |      | V     |

| CMRR               | Common Mode Rejection Ratio <sup>1</sup> | DC, $V_{CM} = \pm 1V$                       | 50   | 52        |      | dB    |

|                    | Output Characteristics                   |                                             |      |           |      |       |

| V                  | Output Voltage Swing <sup>1</sup>        | $R_L = 2k\Omega$                            |      | ±3.8      |      | V     |

| Vo                 | Output voltage Swing                     | R <sub>L</sub> = 150Ω                       | ±3.2 | ±3.7      |      | V     |

| I <sub>OUT</sub>   | Linear Output Current                    |                                             |      | ±60       |      | mA    |

| I <sub>SC</sub>    | Short Circuit Output Current             | V <sub>O</sub> = GND                        |      | ±100      |      | mA    |

| P                  | Output Resistance                        | enabled                                     |      | TBD       |      | mΩ    |

| R <sub>OUT</sub>   |                                          | disabled                                    |      | TBD       |      | MΩ    |

| C <sub>OUT</sub>   | Output Capacitance                       |                                             |      | TBD       |      | pF    |

### Notes:

1. 100% tested at 25°C

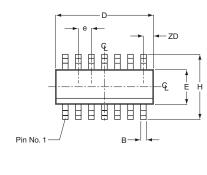

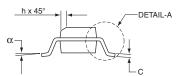

### **Mechanical Dimensions**

### 14-Lead Small Outline Package (SOIC)

∕₅∖

b

C

|        | SOIC-14 |       |

|--------|---------|-------|

| SYMBOL | MIN     | MAX   |

| A1     | .0040   | .0098 |

| В      | .014    | .018  |

| С      | .0075   | .0098 |

| D      | .337    | .344  |

| E      | .150    | .157  |

| е      | .050    | BSC   |

| Н      | .2284   | .2440 |

| h      | .0099   | .0196 |

| L      | .016    | .050  |

| А      | .060    | .068  |

|        | 0°      | 8°    |

| ZD     | 0.2     | 0 ref |

| A2     | .054    | .062  |

#### NOTE:

1. All dimensions are in inches.

2. Lead coplanarity should be 0 to 0.10mm (.004") max.

- 2. Lead coplarantly should be 0 to 0.10mm (.004 ) ma.

3. Package surface finishing: (2.1) Top: matte (charmilles #18~30).

(2.2) All sides: matte (charmilles #18~30).

(2.3) Bottom: smooth or matte (charmilles #18~30).

- 4. All dimensions excluding mold flashes and end flash from the package body shall not exceed 0.152mm (.006) per side (d).

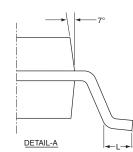

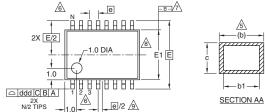

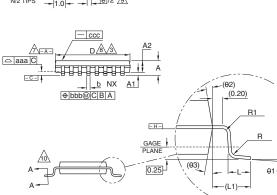

### 14-Lead Outline Package (TSSOP)

A2

|                | TSSC     | OP-14    |      |

|----------------|----------|----------|------|

| SYMBOL         | MIN      | NOM      | MAX  |

| А              | -        | -        | 1.10 |

| A1             | 0.05     | -        | 0.15 |

| A2             | 0.85     | 0.90     | 0.95 |

| L              | 0.50     | 0.60     | 0.75 |

| R              | 0.09     | -        | -    |

| R1             | 0.09     | -        | -    |

| b              | 0.19     | _        | 0.30 |

| b1             | 0.19     | 0.22     | 0.25 |

| С              | 0.09     | -        | 0.20 |

| c1             | 0.09     | -        | 0.16 |

| <del>0</del> 1 | 0°       | _        | 8°   |

| L1             |          | 1.0 REF  |      |

| aaa            |          | 0.10     |      |

| bbb            |          | 0.10     |      |

| CCC            |          | 0.05     |      |

| ddd            |          | 0.20     |      |

| е              |          | 0.65 BSC |      |

| <del>0</del> 2 |          | 12° REF  |      |

| <del>0</del> 3 |          | 12° REF  |      |

| D              | 4.90     | 5.00     | 5.10 |

| E1             | 4.30     | 4.40     | 4.50 |

| E              | 6.4 BSC  |          |      |

| е              | 0.65 BSC |          |      |

| Ν              |          | 14       |      |

|                |          |          |      |

#### NOTES:

- 1 All dimensions are in millimeters (angle in degrees).

- 2 Dimensioning and tolerancing per ASME Y14.5-1994.

- 🖄 Dimensions "D" does not include mold flash, protusions or gate burrs. Mold flash protusions or gate burrs shall not exceed 0.15 per side .

- A Dimension "E1" does not include interlead flash or protusion. Interlead flash or protusion shall not exceed 0.25 per side.

- A Dimension "b" does not include dambar protusion. Allowable dambar protusion shall be 0.08mm total in excess of the "b" dimension at maximum material condition. Dambar connot be located on the lower radius of the foot. Minimum space between protusion and adjacent lead is 0.07mm for 0.5mm pitch packages.

- Terminal numbers are shown for reference only.

- $\triangle$  Datums -A- and -B- to be determined at datum plane -H-.

- & Dimensions "D" and "E1" to be determined at datum plane -H-

- A This dimensions applies only to variations with an even number of leads per side. For variation with an odd number of leads per side, the "center" lead must be coincident with the package centerline, Datum A.

- A Cross sections A A to be determined at 0.10 to 0.25mm from the leadtip.

Downloaded from Datasheet.su

6

SuperSOT<sup>™</sup>-6

SuperSOT<sup>™</sup>-8

SyncFET™

TINYOPTO™

TruTranslation™

TCM™ TinyLogic<sup>®</sup>

UHC™

VCX™

Wire™

UltraFET<sup>®</sup>

UniFET™

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

MICROCOUPLER™

**ISOPLANAR™**

LittleFET™

MicroFET™

MicroPak™

MSXPro™

OCXPro™ **OPTOLOGIC**<sup>®</sup>

PACMAN™

Power247™

PowerEdge™

**POP™**

MSX™

OCX™

MICROWIRE™

**OPTOPLANAR™**

PowerSaver™

PowerTrench<sup>®</sup>

Quiet Series<sup>™</sup> RapidConfigure™

μSerDes™ ScalarPump™

SPM™

Stealth™

SuperFET™

SuperSOT™-3

RapidConnect™

SMART START™

QT Optoelectronics<sup>™</sup>

SILENT SWITCHER®

**QFET<sup>®</sup>**

QS™

| ACEx™                                | FAST <sup>®</sup>              |  |

|--------------------------------------|--------------------------------|--|

| ActiveArray™                         | FASTr™                         |  |

| Bottomless™                          | FPS™                           |  |

| Build it Now™                        | FRFET™                         |  |

| CoolFET™                             | GlobalOptoisolator™            |  |

| CROSSVOLT™                           | GTO™                           |  |

| DOME™                                | HiSeC™                         |  |

| EcoSPARK™                            | I <sup>2</sup> C <sup>™</sup>  |  |

| E <sup>2</sup> CMOS™                 | <i>i-Lo</i> ™                  |  |

| EnSigna™                             | ImpliedDisconnect <sup>™</sup> |  |

| FACT™                                | IntelliMAX™                    |  |

| FACT Quiet Series                    | S <sup>TM</sup>                |  |

| Across the board. Around the world.™ |                                |  |

тм The Power Franchise<sup>®</sup> Programmable Active Droop™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS. NOR THE RIGHTS OF OTHERS.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **PRODUCT STATUS DEFINITIONS**

#### Definition of Terms

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

| Rev. 118                 |                           |                                                                                                                                                                                                                                   |