# COP8SBR9/COP8SCR9/COP8SDR9 8-Bit CMOS Flash Based Microcontroller with 32k Memory, Virtual EEPROM and Brownout

## **1.0 General Description**

The COP8SBR9/SCR9/SDR9 Flash based microcontrollers are highly integrated COP8<sup>™</sup> Feature core devices, with 32k Flash memory and advanced features including Virtual EE-PROM, High Speed Timers, USART, and Brownout Reset. This single-chip CMOS device is suited for applications requiring a full featured, in-system reprogrammable controller with large memory and low EMI. The same device is used for development, pre-production and volume production with a range of COP8 software and hardware development tools.

Devices included in this datasheet:

| Device   | Flash Program<br>Memory<br>(bytes) | RAM<br>(bytes) | Brownout<br>Voltage | I/O<br>Pins     | Packages                              | Temperature                       |

|----------|------------------------------------|----------------|---------------------|-----------------|---------------------------------------|-----------------------------------|

| COP8SBR9 | 32k                                | 1k             | 2.7V to 2.9V        | 37,39,49,<br>59 | 44 LLP,<br>44/68 PLCC,<br>48/56 TSSOP | –40°C to +85°C                    |

| COP8SCR9 | 32k                                | 1k             | 4.17V to 4.5V       | 37,39,49,<br>59 | 44 LLP,<br>44/68 PLCC,<br>48/56 TSSOP | –40°C to +85°C<br>–40°C to +125°C |

| COP8SDR9 | 32k                                | 1k             | No Brownout         | 37,39,49,<br>59 | 44 LLP,<br>44/68 PLCC,<br>48/56 TSSOP | –40°C to +85°C<br>–40°C to +125°C |

### 2.0 Features

#### **KEY FEATURES**

- 32 kbytes Flash Program Memory with Security Feature

- Virtual EEPROM using Flash Program Memory

- 1 kbyte volatile RAM

- USART with on chip baud generator

- 2.7V–5.5V In-System Programmability of Flash

- High endurance 100k Read/Write Cycles

- Superior data retention 100 years

- Dual Clock Operation with HALT/IDLE Power Save Modes

- Three 16-bit timers:

- Timers T2 and T3 can operate at high speed (50 ns resolution)

- Processor Independent PWM mode

- External Event counter mode

- Input Capture mode

- Brown-out Reset (COP8SBR9/SCR9)

#### **OTHER FEATURES**

- Single supply operation: 2.7V-5.5V

- Quiet Design (low radiated emissions)

- Multi-Input Wake-up with optional interrupts

- MICROWIRE/PLUS (Serial Peripheral Interface Compatible)

- Clock Doubler for 20 MHz operation from 10 MHz Oscillator, with 0.5

µs Instruction Cycle

- Thirteen multi-source vectored interrupts servicing:

External Interrupt

- USART (2)

- Idle Timer T0

- Three Timers (each with 2 interrupts)

- MICROWIRE/PLUS Serial peripheral interface

- Multi-Input Wake-Up

- Software Trap

- Idle Timer with programmable interrupt interval

- 8-bit Stack Pointer SP (stack in RAM)

- Two 8-bit Register Indirect Data Memory Pointers

- True bit manipulation

- WATCHDOG and Clock Monitor logic

- Software selectable I/O options

- TRI-STATE<sup>®</sup> Output/High Impedance Input

Push-Pull Output

- Weak Pull Up Input

- Schmitt trigger inputs on I/O ports

- High Current I/Os

- Temperature range: -40°C to +85°C and -40°C to +125°C (COP8SCR9/SDR9)

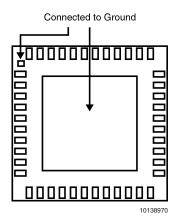

- Packaging: 44 and 68 PLCC, 44 LLP, 48 and 56 TSSOP

- True In-System, Real time emulation and debug offered by MetaLink's Development Systemstools available

$\mathsf{COP8}^{{\scriptscriptstyle\mathsf{T}}{\scriptscriptstyle\mathsf{M}}}$  is a trademark of National Semiconductor Corporation.

## 4.0 Ordering Information

#### Part Numbering Scheme

| COP8 | SB                                                                          | R                         | 9                         | н                                                    | VA                                  | 8                                     |

|------|-----------------------------------------------------------------------------|---------------------------|---------------------------|------------------------------------------------------|-------------------------------------|---------------------------------------|

|      | Family and<br>Feature Set<br>Indicator                                      | Program<br>Memory<br>Size | Program<br>Memory<br>Type | No. Of Pins                                          | Package<br>Type                     | Temperature                           |

|      | SB = Low Brownout Voltage<br>SC = High Brownout Voltage<br>SD = No Brownout | R = 32k                   | 9 = Flash                 | H = 44 Pin<br>I = 48 Pin<br>k = 56 Pin<br>L = 68 Pin | LQ = LLP<br>MT = TSSOP<br>VA = PLCC | 7 = -40 to +125°C<br>8 = -40 to +85°C |

| Table of Contents                                                              |    |

|--------------------------------------------------------------------------------|----|

| 1.0 General Description                                                        |    |

| 2.0 Features                                                                   |    |

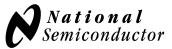

| 3.0 Block Diagram                                                              |    |

| 4.0 Ordering Information                                                       |    |

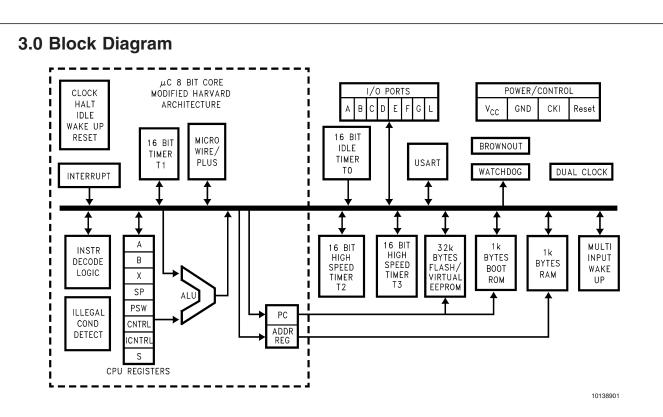

| 5.0 Connection Diagrams                                                        |    |

| 6.0 Architectural Overview                                                     |    |

|                                                                                |    |

| 6.2 IN-SYSTEM PROGRAMMING AND VIRTUAL EEPROM                                   |    |

| 6.3 DUAL CLOCK AND CLOCK DOUBLER                                               | 10 |

| 6.5 ARCHITECTURE                                                               | 10 |

| 6.6 INSTRUCTION SET                                                            |    |

| 6.6.1 Key Instruction Set Features                                             |    |

| 6.6.2 Single Byte/Single Cycle Code Execution                                  | 10 |

| 6.6.3 Many Single-Byte, Multi-Function Instructions                            | 10 |

| 6.6.3 Many Single-Byte, Multi-Function Instructions<br>6.6.4 Bit-Level Control | 11 |

| 6.6.5 Register Set                                                             | 11 |

| 6.7 PACKAGING/PIN EFFICIENCY                                                   | 11 |

| 7.0 Absolute Maximum Ratings                                                   |    |

| 8.0 Electrical Characteristics                                                 |    |

| 9.0 Pin Descriptions                                                           |    |

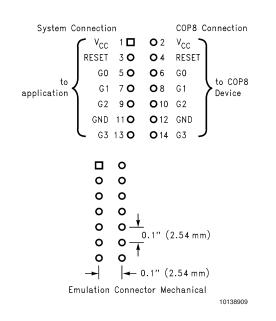

| 9.1 EMULATION CONNECTION                                                       |    |

| 10.0 Functional Description                                                    |    |

| 10.1 CPU REGISTERS                                                             | 19 |

| 10.2 PROGRAM MEMORY                                                            | 19 |

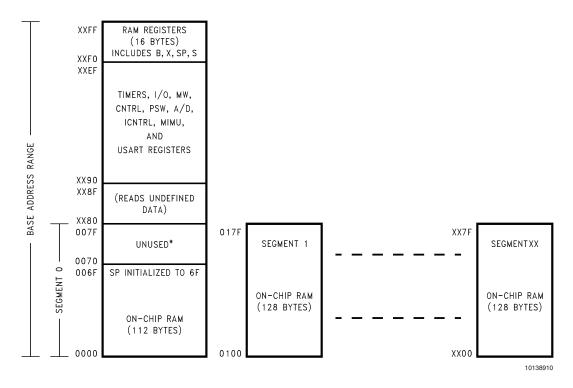

| 10.3 DATA MEMORY                                                               | 19 |

| 10.4 DATA MEMORY SEGMENT RAM EXTENSION                                         | 19 |

| 10.4.1 Virtual EEPROM                                                          |    |

| 10.5 OPTION REGISTER                                                           | 20 |

| 10.6 SECURITY                                                                  | 21 |

| 10.7 RESET                                                                     |    |

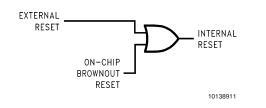

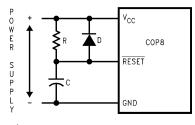

| 10.7.1 External Reset                                                          |    |

| 10.7.2 On-Chip Brownout Reset                                                  | 22 |

| 10.8 OSCILLATOR CIRCUITS                                                       | 24 |

| 10.8.1 Oscillator                                                              |    |

| 10.8.2 Clock Doubler                                                           |    |

|                                                                                |    |

| 10.9 CONTROL REGISTERS                                                         |    |

| 10.9.1 CNTRL Register (Address X'00EE)                                         |    |

| 10.9.2 PSW Register (Address X'00EF)                                           | 25 |

| 10.9.3 ICNTRL Register (Address X'00E8)                                        |    |

| 10.9.4 T2CNTRL Register (Address X'00C6)                                       |    |

| 10.9.5 T3CNTRL Register (Address X'00B6)                                       |    |

| 10.9.7 ITMR Register (Address X'00CF)                                          |    |

| 11.0 In-System Programming                                                     |    |

| 11.1 INTRODUCTION                                                              |    |

| 11.2 FUNCTIONAL DESCRIPTION                                                    |    |

| 11.3 REGISTERS                                                                 |    |

| 11.3.1 ISP Address Registers                                                   |    |

| 11.3.2 ISP Read Data Register                                                  |    |

| 11.3.3 ISP Write Data Register                                                 |    |

| 11.3.4 ISP Write Timing Register                                               |    |

| 11.4 MANEUVERING BACK AND FORTH BETWEEN FLASH MEMORY AND BOOT ROM              | 29 |

| 11.5 FORCED EXECUTION FROM BOOT ROM                                            |    |

| 11.6 RETURN TO FLASH MEMORY WITHOUT HARDWARE RESET                             | 30 |

| 11.7 MICROWIRE/PLUS ISP                                                        |    |

| 11.8 USER ISP AND VIRTUAL E <sup>2</sup>                                       |    |

| 11.9 RESTRICTIONS ON SOFTWARE WHEN CALLING ISP ROUTINES IN BOOT ROM            |    |

| 11.10 FLASH MEMORY DURABILITY CONSIDERATIONS                                   | 32 |

| 12.0 Timers                                                                    |    |

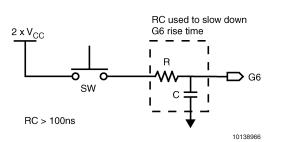

| 12.1 TIMER T0 (IDLE TIMER)                                                     | 34 |

# Table of Contents (Continued)

| 12.1.1 ITMR Register                                                           | 34 |

|--------------------------------------------------------------------------------|----|

| 12.2 TIMER T1, TIMER T2, AND TIMER T3                                          | 35 |

| 12.2.1 Timer Operating Speeds                                                  | 35 |

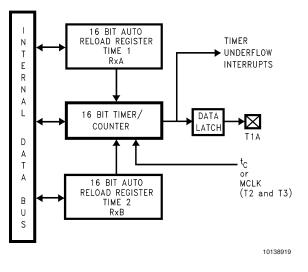

| 12.2.2 Mode 1. Processor Independent PWM Mode                                  | 35 |

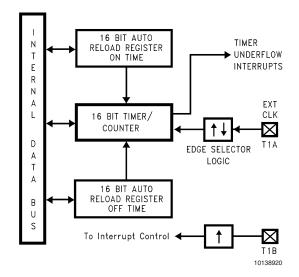

| 12.2.3 Mode 2. External Event Counter Mode                                     | 36 |

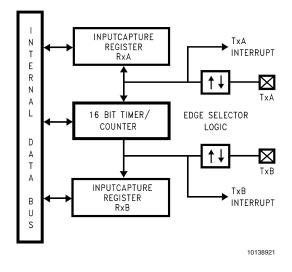

| 12.2.4 Mode 3. Input Capture Mode                                              | 36 |

| 12.3 TIMER CONTROL FLAGS                                                       | 36 |

| 13.0 Power Saving Features                                                     |    |

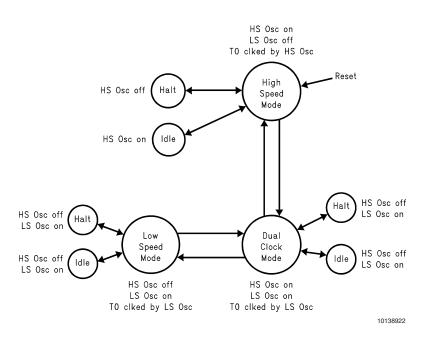

| 13.1 POWER SAVE MODE CONTROL REGISTER                                          |    |

| 13.2 OSCILLATOR STABILIZATION                                                  |    |

| 13.3 HIGH SPEED MODE OPERATION                                                 |    |

| 13.3.1 High Speed Halt Mode                                                    |    |

| 13.3.1.1 Entering The High Speed Halt Mode                                     |    |

| 13.3.1.2 Exiting The High Speed Halt Mode                                      |    |

| 13.3.1.3 HALT Exit Using Reset                                                 | 39 |

| 13.3.1.4 HALT Exit Using Multi-Input Wake-up                                   |    |

| 13.3.1.5 Options                                                               | 39 |

| 13.3.2 High Speed Idle Mode                                                    |    |

| 13.4 DUAL CLOCK MODE OPERATION                                                 |    |

| 13.4.1 Dual Clock HALT Mode                                                    |    |

| 13.4.1.1 Entering The Dual Clock Halt Mode                                     |    |

| 13.4.1.2 Exiting The Dual Clock Halt Mode                                      |    |

| 13.4.1.3 HALT Exit Using Reset<br>13.4.1.4 HALT Exit Using Multi-Input Wake-up |    |

| 13.4.1.5 Options                                                               | 41 |

| 13.4.2 Dual Clock Idle Mode                                                    |    |

| 13.5 LOW SPEED MODE OPERATION                                                  | 42 |

| 13.5.1 Low Speed HALT Mode                                                     |    |

| 13.5.1.1 Entering The Low Speed Halt Mode                                      | 42 |

| 13.5.1.2 Exiting The Low Speed Halt Mode                                       |    |

| 13.5.1.3 HALT Exit Using Reset                                                 | 42 |

| 13.5.1.4 HALT Exit Using Multi-Input Wake-up                                   |    |

| 13.5.1.5 Options                                                               | 42 |

| 13.5.2 Low Speed Idle Mode                                                     | 42 |

| 13.6 MULTI-INPUT WAKE-UP                                                       |    |

| 14.0 USART                                                                     |    |

| 14.1 USART CONTROL AND STATUS REGISTERS                                        |    |

| 14.2 DESCRIPTION OF USART REGISTER BITS                                        | 45 |

| 14.3 ASSOCIATED I/O PINS                                                       |    |

| 14.4 USART OPERATION                                                           |    |

| 14.4.0 Surphysical Mode                                                        |    |

| 14.4.2 Synchronous Mode                                                        |    |

| 14.5 FRAMING FORMATS                                                           |    |

| 14.7 BAUD CLOCK GENERATION                                                     |    |

| 14.8 EFFECT OF HALT/IDLE                                                       |    |

| 14.9 DIAGNOSTIC                                                                |    |

| 14.10 ATTENTION MODE                                                           |    |

| 14.11 BREAK GENERATION                                                         |    |

| 15.0 Interrupts                                                                |    |

| 15.1 INTRODUCTION                                                              |    |

| 15.2 MASKABLE INTERRUPTS                                                       | 51 |

| 15.3 VIS INSTRUCTION                                                           | 52 |

| 15.3.1 VIS Execution                                                           |    |

| 15.4 NON-MASKABLE INTERRUPT                                                    |    |

| 15.4.1 Pending Flag                                                            |    |

| 15.4.2 Software Trap                                                           | 54 |

| 15.4.2.1 Programming Example: External Interrupt                               | 56 |

| 15.5 PORT L INTERRUPTS                                                         |    |

| 15.6 INTERRUPT SUMMARY                                                         |    |

| 16.0 WATCHDOG/Clock Monitor                                                    | 57 |

# COP8SBR9/COP8SCR9/COP8SDR9

# Table of Contents (Continued)

| 16.1 CLOCK MONITOR                                            |    |

|---------------------------------------------------------------|----|

| 16.2 WATCHDOG/CLOCK MONITOR OPERATION                         |    |

| 16.3 WATCHDOG AND CLOCK MONITOR SUMMARY                       |    |

| 16.4 DETECTION OF ILLEGAL CONDITIONS                          |    |

| 17.0 MICROWIRE/PLUS                                           |    |

| 17.1 MICROWIRE/PLUS OPERATION                                 |    |

| 17.1.1 MICROWIRE/PLUS Master Mode Operation                   | 59 |

| 17.1.2 MICROWIRE/PLUS Slave Mode Operation                    |    |

| 17.1.2.1 Alternate SK Phase Operation and SK Idle Polarity    |    |

| 18.0 Memory Map                                               |    |

| 19.0 Instruction Set                                          |    |

| 19.1 INTRODUCTION                                             |    |

| 19.2 INSTRUCTION FEATURES                                     |    |

| 19.3 ADDRESSING MODES                                         |    |

| 19.3.1 Operand Addressing Modes                               | 64 |

| 19.3.2 Tranfer-of-Control Addressing Modes                    | 65 |

| 19.4 INSTRUCTION TYPES                                        |    |

| 19.4.1 Arithmetic Instructions                                | 66 |

| 19.4.2 Transfer-of-Control Instructions                       | 66 |

| 19.4.3 Load and Exchange Instructions                         | 66 |

| 19.4.4 Logical Instructions                                   | 66 |

| 19.4.5 Accumulator Bit Manipulation Instructions              | 66 |

| 19.4.6 Stack Control Instructions                             |    |

| 19.4.7 Memory Bit Manipulation Instructions                   | 66 |

| 19.4.8 Conditional Instructions                               | 66 |

| 19.4.9 No-Operation Instruction                               | 66 |

| 19.5 REGISTER AND SYMBOL DEFINITION                           | 67 |

| 19.6 INSTRUCTION SET SUMMARY                                  | 67 |

| 19.7 INSTRUCTION EXECUTION TIME                               |    |

| 20.0 Development Support                                      | 71 |

| 20.1 TOOLS ORDERING NUMBERS FOR THE COP8 FLASH FAMILY DEVICES | 71 |

| 20.2 COP8 TOOLS OVERVIEW                                      | 73 |

| 20.3 WHERE TO GET TOOLS                                       | 74 |

| 21.0 Revision History                                         | 76 |

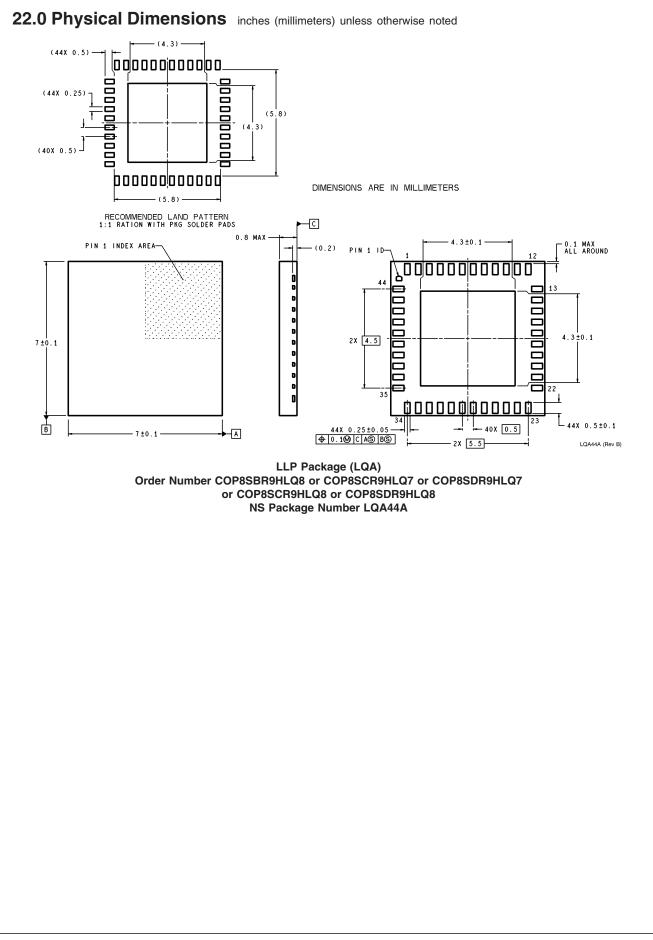

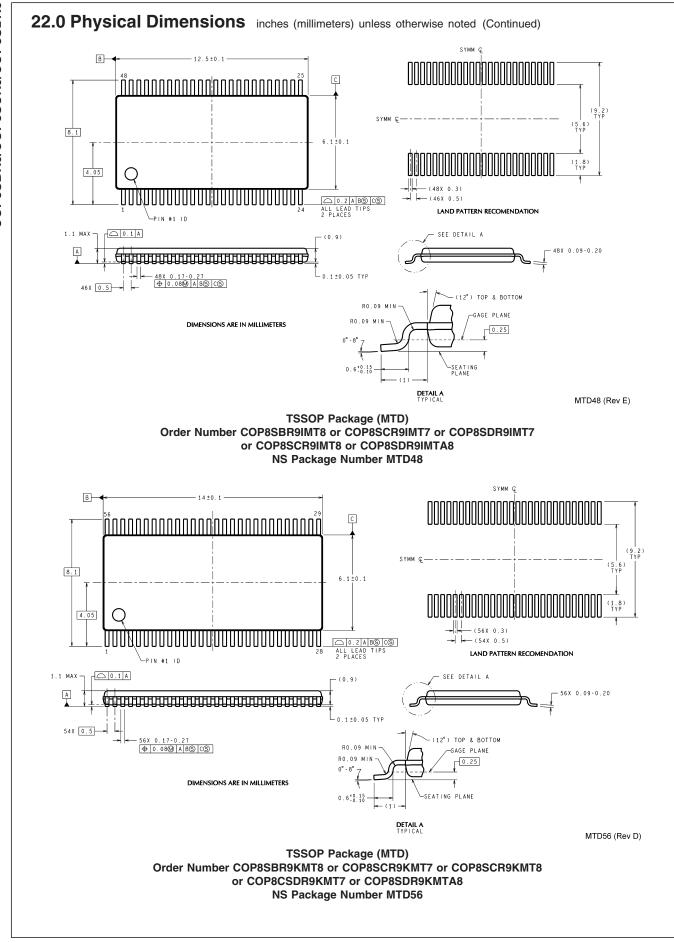

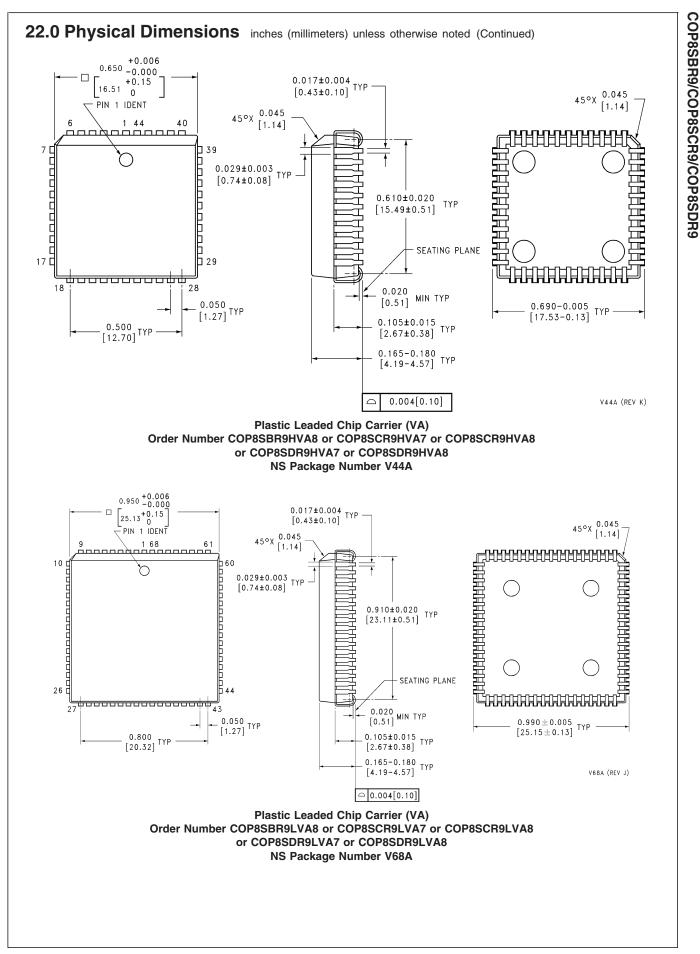

| 22.0 Physical Dimensions                                      |    |

| -                                                             |    |

# COP8SBR9/COP8SCR9/COP8SDR9

# 5.0 Connection Diagrams (Continued)

| RESET - | 1  | $\bigcirc$ | 56 | <b></b> D7        |

|---------|----|------------|----|-------------------|

| G0 🗕    | 2  |            | 55 | D6                |

| G1 🗕    | 3  |            | 54 | <b>—</b> D5       |

| G2 🗕    | 4  |            | 53 | <b>—</b> D4       |

| G3 🗕    | 5  |            | 52 | <b>—</b> D3       |

| G4 🗕    | 6  |            | 51 | <b>—</b> D2       |

| G5 🗕    | 7  |            | 50 | <b>—</b> D1       |

| G6 🗕    | 8  |            | 49 | <b>—</b> D0       |

| G7 🗕    | 9  |            | 48 | — E1              |

| СКІ 🗕   | 10 |            | 47 | — E0              |

| C0 🗕    | 11 |            | 46 | <b>—</b> A7       |

| C1 🗕    | 12 | 56-PIN     | 45 | <b>—</b> A6       |

| C2 🗕    | 13 | TSSOP      | 44 | <b>—</b> A5       |

| Сз 🗕    | 14 |            | 43 | <b>—</b> A4       |

| L0 🗕    | 15 |            | 42 | — АЗ              |

| L1 🗕    | 16 |            | 41 | <b>—</b> A2       |

| L2 🗕    | 17 |            | 40 | — A1              |

| L3 🗕    | 18 |            | 39 | — A0              |

| L4 🗕    | 19 |            | 38 | – v <sub>cc</sub> |

| L5 🗕    | 20 |            | 37 | — N/C             |

| L6 🗕    | 21 |            | 36 | — N/C             |

| L7 🗕    | 22 |            | 35 | - DGND            |

| C4 🗕    | 23 |            | 34 | <b>—</b> B7       |

| C5 🗕    | 24 |            | 33 | <b>—</b> B6       |

| C6 🗕    | 25 |            | 32 | <b>—</b> B5       |

| C7 🗕    | 26 |            | 31 | <b>—</b> B4       |

| В0 🗕    | 27 |            | 30 | <b>—</b> B3       |

| B1 🗕    | 28 |            | 29 | <b>—</b> B2       |

|         |    |            |    | 10138942          |

# COP8SBR9/COP8SCR9/COP8SDR9

Top View TSSOP Package See NS Package Number MTD56

| Port | Туре | Alt. Fun                            | In System<br>Emulation<br>Mode | 44-Pin LLP | 44-Pin<br>PLCC | 48-Pin<br>TSSOP | 56-Pin<br>TSSOP | 68-Pin<br>PLCC |

|------|------|-------------------------------------|--------------------------------|------------|----------------|-----------------|-----------------|----------------|

| L0   | I/O  | MIWU or Low Speed OSC In            |                                | 16         | 11             | 11              | 15              | 22             |

| L1   | I/O  | MIWU or CKX or Low Speed<br>OSC Out |                                | 17         | 12             | 12              | 16              | 23             |

| L2   | I/O  | MIWU or TDX                         |                                | 18         | 13             | 13              | 17              | 24             |

| L3   | I/O  | MIWU or RDX                         |                                | 19         | 14             | 14              | 18              | 25             |

| L4   | I/O  | MIWU or T2A                         |                                | 20         | 15             | 15              | 19              | 26             |

| L5   | I/O  | MIWU or T2B                         |                                | 21         | 16             | 16              | 20              | 27             |

| L6   | I/O  | MIWU or T3A                         |                                | 22         | 17             | 17              | 21              | 28             |

| L7   | I/O  | MIWU or T3B                         |                                | 23         | 18             | 18              | 22              | 29             |

| G0   | I/O  | INT                                 | Input                          | 7          | 2              | 2               | 2               | 3              |

| G1   | I/O  | WDOUT <sup>a</sup>                  | POUT                           | 8          | 3              | 3               | 3               | 4              |

| G2   | I/O  | T1B                                 | Output                         | 9          | 4              | 4               | 4               | 5              |

| G3   | I/O  | T1A                                 | Clock                          | 10         | 5              | 5               | 5               | 6              |

| G4   | I/O  | SO                                  |                                | 11         | 6              | 6               | 6               | 11             |

| G5   | I/O  | SK                                  |                                | 12         | 7              | 7               | 7               | 12             |

| G6   | 1    | SI                                  |                                | 13         | 8              | 8               | 8               | 13             |

| TABLE 1. Pinouts for All Packages (Continued) |      |          |                                |            |                |                 |                 |               |  |  |

|-----------------------------------------------|------|----------|--------------------------------|------------|----------------|-----------------|-----------------|---------------|--|--|

| Port                                          | Туре | Alt. Fun | In System<br>Emulation<br>Mode | 44-Pin LLP | 44-Pin<br>PLCC | 48-Pin<br>TSSOP | 56-Pin<br>TSSOP | 68-Pi<br>PLCC |  |  |

| G7                                            | 1    | СКО      |                                | 14         | 9              | 9               | 9               | 14            |  |  |

| D0                                            | 0    |          |                                | 42         | 37             | 41              | 49              | 58            |  |  |

| D1                                            | 0    |          |                                | 43         | 38             | 42              | 50              | 59            |  |  |

| D2                                            | 0    |          |                                | 44         | 39             | 43              | 51              | 60            |  |  |

| D3                                            | 0    |          |                                | 1          | 40             | 44              | 52              | 61            |  |  |

| D4                                            | 0    |          |                                | 2          | 41             | 45              | 53              | 62            |  |  |

| D5                                            | 0    |          |                                | 3          | 42             | 46              | 54              | 63            |  |  |

| D6                                            | 0    |          |                                | 4          | 43             | 47              | 55              | 64            |  |  |

| D7                                            | 0    |          |                                | 5          | 44             | 48              | 56              | 65            |  |  |

| Ξ0                                            | 1/0  |          |                                |            |                |                 | 47              | 54            |  |  |

| E1                                            | I/O  |          |                                |            |                |                 | 48              | 55            |  |  |

| <b>Ξ</b> 2                                    | I/O  |          |                                |            |                |                 |                 | 56            |  |  |

| E3                                            | I/O  |          |                                |            |                |                 |                 | 57            |  |  |

| <u> </u>                                      | 1/0  |          |                                |            |                |                 |                 | 67            |  |  |

| 5                                             | 1/0  |          |                                |            |                |                 |                 | 68            |  |  |

| Ξ6                                            | 1/0  |          |                                |            |                |                 |                 | 1             |  |  |

| <b>E</b> 7                                    | 1/0  |          |                                |            |                |                 |                 | 2             |  |  |

| 0                                             | 1/0  |          |                                |            |                |                 | 11              | 18            |  |  |

| C1                                            | 1/0  |          |                                |            |                |                 | 12              | 19            |  |  |

| 22                                            | 1/0  |          |                                |            |                |                 | 13              | 20            |  |  |

| <br>C3                                        | 1/0  |          |                                |            |                |                 | 14              | 21            |  |  |

| C4                                            | 1/0  |          |                                |            |                |                 | 23              | 30            |  |  |

| C5                                            | 1/0  |          |                                |            |                |                 | 24              | 31            |  |  |

| 26                                            | I/O  |          |                                |            |                |                 | 25              | 32            |  |  |

| C7                                            | 1/0  |          |                                |            |                |                 | 26              | 33            |  |  |

| 40                                            | 1/0  |          |                                |            |                | 33              | 39              | 46            |  |  |

| A1                                            | I/O  |          |                                |            |                | 34              | 40              | 47            |  |  |

| 42                                            | 1/0  |          |                                | 36         | 31             | 35              | 41              | 48            |  |  |

| 43                                            | 1/0  |          |                                | 37         | 32             | 36              | 42              | 49            |  |  |

| \4                                            | 1/0  |          |                                | 38         | 33             | 37              | 43              | 50            |  |  |

| 45                                            | 1/0  |          |                                | 39         | 34             | 38              | 44              | 51            |  |  |

| 46                                            | 1/0  |          |                                | 40         | 35             | 39              | 45              | 52            |  |  |

| 47                                            | 1/0  |          |                                | 41         | 36             | 40              | 46              | 53            |  |  |

| 30                                            | 1/0  |          |                                | 24         | 19             | 19              | 27              | 34            |  |  |

| 31                                            | 1/0  |          |                                | 25         | 20             | 20              | 28              | 35            |  |  |

| 32                                            | 1/0  |          |                                | 26         | 21             | 21              | 29              | 36            |  |  |

| 33                                            | 1/0  |          |                                | 27         | 22             | 22              | 30              | 37            |  |  |

| 34                                            | 1/0  |          |                                | 28         | 23             | 23              | 31              | 38            |  |  |

| 35                                            | 1/0  |          |                                | 29         | 23             | 24              | 32              | 39            |  |  |

| 36                                            | 1/0  |          |                                | 30         | 25             | 25              | 33              | 40            |  |  |

| 37                                            | 1/0  |          |                                | 31         | 26             | 25              | 34              | 40            |  |  |

| =0                                            | 1/0  |          |                                |            | 20             | 20              |                 | 7             |  |  |

| =1                                            | 1/0  |          |                                |            |                |                 |                 | 8             |  |  |

| =2                                            | 1/0  |          |                                |            |                |                 |                 | 9             |  |  |

| -2<br>-3                                      | 1/O  |          |                                |            |                |                 |                 | 10            |  |  |

| -3<br>DV <sub>cc</sub>                        | 1/0  |          | V <sub>cc</sub>                | 35         | 30             | 32              | 38              | 17, 4         |  |  |

COP8SBR9/COP8SCR9/COP8SDR9

www.national.com

|                                                                                              | IA                           | BLE 1. Pinouts for             | All Packages (C | Continued)     |                 |                 |                |

|----------------------------------------------------------------------------------------------|------------------------------|--------------------------------|-----------------|----------------|-----------------|-----------------|----------------|

| Port Type                                                                                    | Alt. Fun                     | In System<br>Emulation<br>Mode | 44-Pin LLP      | 44-Pin<br>PLCC | 48-Pin<br>TSSOP | 56-Pin<br>TSSOP | 68-Pin<br>PLCC |

| GND                                                                                          |                              | GND                            | 32              | 27             | 27              | 35              | 16, 42         |

| <i i<="" td=""><td></td><td></td><td>15</td><td>10</td><td>10</td><td>10</td><td>15</td></i> |                              |                                | 15              | 10             | 10              | 10              | 15             |

| ESET I                                                                                       | DOUT is controlled by Option | RESET                          | 6               | 1              | 1               | 1               | 66             |

|                                                                                              |                              |                                |                 |                |                 |                 |                |

9

## 6.0 Architectural Overview

#### 6.1 EMI REDUCTION

The COP8SBR9/SCR9/SDR9 devices incorporate circuitry that guards against electromagnetic interference - an increasing problem in today's microcontroller board designs. National's patented EMI reduction technology offers low EMI clock circuitry, gradual turn-on output drivers (GTOs) and internal Icc smoothing filters, to help circumvent many of the EMI issues influencing embedded control designs. National has achieved 15 dB–20 dB reduction in EMI transmissions when designs have incorporated its patented EMI reducing circuitry.

# 6.2 IN-SYSTEM PROGRAMMING AND VIRTUAL EEPROM

The device includes a program in a boot ROM that provides the capability, through the MICROWIRE/PLUS serial interface, to erase, program and read the contents of the Flash memory.

Additional routines are included in the boot ROM, which can be called by the user program, to enable the user to customize in system software update capability if MICROWIRE/ PLUS is not desired.

Additional functions will copy blocks of data between the RAM and the Flash Memory. These functions provide a virtual EEPROM capability by allowing the user to emulate a variable amount of EEPROM by initializing nonvolatile variables from the Flash Memory and occasionally restoring these variables to the Flash Memory.

The contents of the boot ROM have been defined by National. Execution of code from the boot ROM is dependent on the state of the FLEX bit in the Option Register on exit from RESET. If the FLEX bit is a zero, the Flash Memory is assumed to be empty and execution from the boot ROM begins. For further information on the FLEX bit, refer to Section 4.5, Option Register.

#### 6.3 DUAL CLOCK AND CLOCK DOUBLER

The device includes a versatile clocking system and two oscillator circuits designed to drive a crystal or ceramic resonator. The primary oscillator operates at high speed up to 10 MHz. The secondary oscillator is optimized for operation at 32.768 kHz.

The user can, through specified transition sequences (please refer to *13.0 Power Saving Features*), switch execution between the high speed and low speed oscillators. The unused oscillator can then be turned off to minimize power dissipation. If the low speed oscillator is not used, the pins are available as general purpose bidirectional ports.

The operation of the CPU will use a clock at twice the frequency of the selected oscillator (up to 20 MHz for high speed operation and 65.536 kHz for low speed operation). This doubled clock will be referred to in this document as 'MCLK'. The frequency of the selected oscillator will be referred to as CKI. Instruction execution occurs at one tenth the selected MCLK rate.

#### 6.4 TRUE IN-SYSTEM EMULATION

On-chip emulation capability has been added which allows the user to perform true in-system emulation using final production boards and devices. This simplifies testing and evaluation of software in real environmental conditions. The user, merely by providing for a standard connector which can be bypassed by jumpers on the final application board, can provide for software and hardware debugging using actual production units.

#### **6.5 ARCHITECTURE**

The COP8 family is based on a modified Harvard architecture, which allows data tables to be accessed directly from program memory. This is very important with modern microcontroller-based applications, since program memory is usually ROM or EPROM, while data memory is usually RAM. Consequently constant data tables need to be contained in non-volatile memory, so they are not lost when the microcontroller is powered down. In a modified Harvard architecture, instruction fetch and memory data transfers can be overlapped with a two stage pipeline, which allows the next instruction to be fetched from program memory while the current instruction is being executed using data memory. This is not possible with a Von Neumann single-address bus architecture.

The COP8 family supports a software stack scheme that allows the user to incorporate many subroutine calls. This capability is important when using High Level Languages. With a hardware stack, the user is limited to a small fixed number of stack levels.

#### 6.6 INSTRUCTION SET

In today's 8-bit microcontroller application arena cost/ performance, flexibility and time to market are several of the key issues that system designers face in attempting to build well-engineered products that compete in the marketplace. Many of these issues can be addressed through the manner in which a microcontroller's instruction set handles processing tasks. And that's why the COP8 family offers a unique and code-efficient instruction set - one that provides the flexibility, functionality, reduced costs and faster time to market that today's microcontroller based products require.

Code efficiency is important because it enables designers to pack more on-chip functionality into less program memory space (ROM, OTP or Flash). Selecting a microcontroller with less program memory size translates into lower system costs, and the added security of knowing that more code can be packed into the available program memory space.

#### 6.6.1 Key Instruction Set Features

The COP8 family incorporates a unique combination of instruction set features, which provide designers with optimum code efficiency and program memory utilization.

#### 6.6.2 Single Byte/Single Cycle Code Execution

The efficiency is due to the fact that the majority of instructions are of the single byte variety, resulting in minimum program space. Because compact code does not occupy a substantial amount of program memory space, designers can integrate additional features and functionality into the microcontroller program memory space. Also, the majority instructions executed by the device are single cycle, resulting in minimum program execution time. In fact, 77% of the instructions are single byte single cycle, providing greater code and I/O efficiency, and faster code execution.

#### 6.6.3 Many Single-Byte, Multi-Function Instructions

The COP8 instruction set utilizes many single-byte, multifunction instructions. This enables a single instruction to accomplish multiple functions, such as DRSZ, DCOR, JID, LD (Load) and X (Exchange) instructions with postincrementing and post-decrementing, to name just a few

### 6.0 Architectural Overview (Continued)

examples. In many cases, the instruction set can simultaneously execute as many as three functions with the same single-byte instruction.

JID: (Jump Indirect); Single byte instruction decodes external events and jumps to corresponding service routines (analogous to "DO CASE" statements in higher level languages).

LAID: (Load Accumulator-Indirect); Single byte look up table instruction provides efficient data path from the program memory to the CPU. This instruction can be used for table lookup and to read the entire program memory for checksum calculations.

RETSK: (Return Skip); Single byte instruction allows return from subroutine and skips next instruction. Decision to branch can be made in the subroutine itself, saving code.

AUTOINC/DEC: (Auto-Increment/Auto-Decrement); These instructions use the two memory pointers B and X to efficiently process a block of data (simplifying "FOR NEXT" or other loop structures in higher level languages).

#### 6.6.4 Bit-Level Control

Bit-level control over many of the microcontroller's I/O ports provides a flexible means to ease layout concerns and save board space. All members of the COP8 family provide the ability to set, reset and test any individual bit in the data memory address space, including memory-mapped I/O ports and associated registers.

#### 6.6.5 Register Set

Three memory-mapped pointers handle register indirect addressing and software stack pointer functions. The memory data pointers allow the option of post-incrementing or postdecrementing with the data movement instructions (LOAD/ EXCHANGE). And 15 memory-mapped registers allow designers to optimize the precise implementation of certain specific instructions.

#### 6.7 PACKAGING/PIN EFFICIENCY

Real estate and board configuration considerations demand maximum space and pin efficiency, particularly given today's high integration and small product form factors. Microcontroller users try to avoid using large packages to get the I/O needed. Large packages take valuable board space and increase device cost, two trade-offs that microcontroller designs can ill afford.

The COP8 family offers a wide range of packages and does not waste pins.

## 7.0 Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )               | 7V                           |

|-------------------------------------------------|------------------------------|

| Voltage at Any Pin                              | –0.3V to V $_{\rm CC}$ +0.3V |

| Total Current into V <sub>CC</sub> Pin (Source) | 200 mA                       |

## **8.0 Electrical Characteristics**

Total Current out of GND Pin (Sink) Storage Temperature Range

200 mA -65°C to +140°C

ESD Protection Level

2 kV (Human Body Model)

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

# DC Electrical Characteristics (-40°C $\leq$ T<sub>A</sub> $\leq$ +85°C) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                                         | Conditions                                    | Min                  | Тур      | Max                  | Units |

|---------------------------------------------------|-----------------------------------------------|----------------------|----------|----------------------|-------|

| Operating Voltage                                 |                                               | 2.7                  |          | 5.5                  | V     |

| Power Supply Rise Time                            |                                               | 10                   |          | 50 x 10 <sup>6</sup> | ns    |

| Power Supply Ripple (Note 2)                      | Peak-to-Peak                                  |                      |          | $0.1 V_{\rm CC}$     | V     |

| Supply Current (Note 3)                           |                                               |                      |          |                      |       |

| High Speed Mode                                   |                                               |                      |          |                      |       |

| CKI = 10 MHz                                      | $V_{\rm CC} = 5.5 V, t_{\rm C} = 0.5 \ \mu s$ |                      |          | 14.7                 | mA    |

| CKI = 3.33 MHz                                    | $V_{\rm CC} = 4.5 V, t_{\rm C} = 1.5 \ \mu s$ |                      |          | 7                    | mA    |

| Dual Clock Mode                                   |                                               |                      |          |                      |       |

| CKI = 10 MHz, Low Speed OSC = 32 kHz              | $V_{\rm CC} = 5.5 V, t_{\rm C} = 0.5 \ \mu s$ |                      |          | 14.7                 | mA    |

| CKI = 3.33 MHz, Low Speed OSC = 32 kHz            | $V_{\rm CC} = 4.5 V, t_{\rm C} = 1.5 \ \mu s$ |                      |          | 7                    | mA    |

| Low Speed Mode                                    |                                               |                      |          |                      |       |

| Low Speed OSC = 32 kHz                            | $V_{CC} = 5.5V$                               |                      | 60       | 103                  | μA    |

| HALT Current with BOR Disabled (Note 4)           |                                               |                      |          |                      |       |

| High Speed Mode                                   | $V_{CC} = 5.5V, CKI = 0 MHz$                  |                      | <2       | 10                   | μA    |

| Dual Clock Mode                                   | $V_{CC} = 5.5V, CKI = 0 MHz, Low$             |                      | <u> </u> | 17                   |       |

|                                                   | Speed OSC = 32 kHz                            |                      | <5       | 17                   | μA    |

| Low Speed Mode                                    | $V_{CC} = 5.5V$ , CKI = 0 MHz, Low            |                      | <5       | 17                   | μA    |

|                                                   | Speed OSC = 32 kHz                            |                      | ~5       | 17                   | μΑ    |

| Idle Current (Note 3)                             |                                               |                      |          |                      |       |

| High Speed Mode                                   |                                               |                      |          |                      |       |

| CKI = 10 MHz                                      | $V_{\rm CC} = 5.5 V, t_{\rm C} = 0.5 \ \mu s$ |                      |          | 2.5                  | mA    |

| CKI = 3.33 MHz                                    | $V_{\rm CC}$ = 4.5V, t <sub>C</sub> = 1.5 µs  |                      |          | 1.2                  | mA    |

| Dual Clock Mode                                   |                                               |                      |          |                      |       |

| CKI = 10 MHz, Low Speed OSC = 32 kHz              | $V_{\rm CC}$ = 5.5V, $t_{\rm C}$ = 0.5 µs     |                      |          | 2.5                  | mA    |

| CKI = 3.33 MHz, Low Speed OSC = 32 kHz            | $V_{\rm CC}$ = 4.5V, t <sub>C</sub> = 1.5 µs  |                      |          | 1.2                  | mA    |

| Low Speed Mode                                    |                                               |                      |          |                      |       |

| Low Speed OSC = 32 kHz                            | $V_{\rm CC} = 5.5 V$                          |                      | 15       | 30                   | μA    |

| Supply Current for BOR Feature                    | $V_{\rm CC} = 5.5 V$                          |                      |          | 45                   | μA    |

| High Brownout Trip Level (BOR Enabled)            |                                               | 4.17                 | 4.28     | 4.5                  | V     |

| Low Brownout Trip Level (BOR Enabled)             |                                               | 2.7                  | 2.78     | 2.9                  | V     |

| Input Levels (V <sub>IH</sub> , V <sub>IL</sub> ) |                                               |                      |          |                      |       |

| Logic High                                        |                                               | 0.8 V <sub>CC</sub>  |          |                      | V     |

| Logic Low                                         |                                               |                      |          | $0.16 V_{CC}$        | V     |

| Internal Bias Resistor for the CKI                |                                               | 0.3                  | 1.0      | 2.5                  | MΩ    |

| Crystal/Resonator Oscillator                      |                                               | 0.3                  | 1.0      | 2.0                  |       |

| Hi-Z Input Leakage                                | $V_{\rm CC} = 5.5 V$                          | -0.5                 |          | +0.5                 | μA    |

| Input Pullup Current                              | $V_{\rm CC} = 5.5 V, V_{\rm IN} = 0 V$        | -50                  |          | -210                 | μA    |

| Port Input Hysteresis                             |                                               | 0.25 V <sub>CC</sub> |          |                      | V     |

www.national.com

# DC Electrical Characteristics $(-40^{\circ}C \le T_A \le +85^{\circ}C)$ (Continued) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                                            | Conditions                                      | Min                 | Тур             | Max                 | Units  |

|------------------------------------------------------|-------------------------------------------------|---------------------|-----------------|---------------------|--------|

| Output Current Levels                                |                                                 |                     |                 |                     |        |

| D Outputs                                            |                                                 |                     |                 |                     |        |

| Source                                               | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -7                  |                 |                     | mA     |

|                                                      | $V_{CC} = 2.7V, V_{OH} = 1.8V$                  | -4                  |                 |                     | mA     |

| Sink (Note 7)                                        | $V_{CC} = 4.5V, V_{OL} = 1.0V$                  | 10                  |                 |                     | mA     |

|                                                      | $V_{\rm CC} = 2.7 V, V_{\rm OL} = 0.4 V$        | 3.5                 |                 |                     | mA     |

| All Others                                           |                                                 |                     |                 |                     |        |

| Source (Weak Pull-Up Mode)                           | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -10                 |                 |                     | μA     |

|                                                      | $V_{CC} = 2.7V, V_{OH} = 1.8V$                  | -5                  |                 |                     | μA     |

| Source (Push-Pull Mode)                              | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -7                  |                 |                     | mA     |

|                                                      | $V_{CC} = 2.7V, V_{OH} = 1.8V$                  | -4                  |                 |                     | mA     |

| Sink (Push-Pull Mode) (Note 7)                       | $V_{CC} = 4.5V, V_{OL} = 1.0V$                  | 10                  |                 |                     | mA     |

|                                                      | $V_{CC} = 2.7V, V_{OL} = 0.4V$                  | 3.5                 |                 |                     | mA     |

| TRI-STATE Leakage                                    | $V_{\rm CC} = 5.5 V$                            | -0.5                |                 | +0.5                | μA     |

| Allowable Sink Current per Pin                       |                                                 |                     |                 | 15                  | mA     |

| Maximum Input Current without Latchup (Note          |                                                 |                     |                 | ±200                | mA     |

| 5)                                                   |                                                 |                     |                 | ±200                | mA     |

| RAM Retention Voltage, V <sub>R</sub> (in HALT Mode) |                                                 | 2.0                 |                 |                     | V      |

| Input Capacitance                                    |                                                 |                     |                 | 7                   | pF     |

| Load Capacitance on D2                               |                                                 |                     |                 | 1000                | pF     |

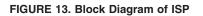

| Voltage on G6 to Force Execution from Boot           | G6 rise time must be slower                     | 2 x V <sub>CC</sub> |                 | V <sub>CC</sub> + 7 | v      |

| ROM (Note 8)                                         | than 100 nS                                     | 2 X V <sub>CC</sub> |                 | V <sub>CC</sub> + 7 | v      |

| G6 Rise Time to Force Execution from Boot            |                                                 | 100                 |                 |                     | nS     |

| ROM                                                  |                                                 | 100                 |                 |                     | 110    |

| Input Current on G6 when Input > $V_{CC}$            | $V_{IN} = 11V, V_{CC} = 5.5V$                   |                     | 500             |                     | μΑ     |

| Flash Memory Data Retention                          | 25°C                                            |                     | 100             |                     | yrs    |

| Flash Memory Number of Erase/Write Cycles            | See Table 13, Typical Flash<br>Memory Endurance |                     | 10 <sup>5</sup> |                     | cycles |

# AC Electrical Characteristics (-40°C $\leq$ T<sub>A</sub> $\leq$ +85°C) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                                     | Conditions                 | Min | Тур | Max | Units          |

|-----------------------------------------------|----------------------------|-----|-----|-----|----------------|

| Instruction Cycle Time (t <sub>c</sub> )      |                            |     |     |     |                |

| Crystal/Resonator                             | $4.5V \le V_{CC} \le 5.5V$ | 0.5 |     | DC  | μs             |

|                                               | $2.7V \le V_{CC} \le 4.5V$ | 1.5 |     | DC  | μs             |

| Flash Memory Page Erase Time                  | See Table 13, Typical      |     |     |     |                |

|                                               | Flash Memory               |     | 1   |     | ms             |

|                                               | Endurance                  |     |     |     |                |

| Flash Memory Mass Erase Time                  |                            |     | 8   |     | ms             |

| Frequency of MICROWIRE/PLUS in                |                            |     |     | 2   | MHz            |

| Slave Mode                                    |                            |     |     | 2   | IVILITZ        |

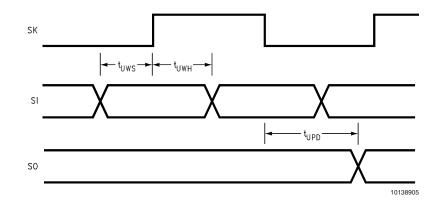

| MICROWIRE/PLUS Setup Time (t <sub>UWS</sub> ) |                            | 20  |     |     | ns             |

| MICROWIRE/PLUS Hold Time (t <sub>UWH</sub> )  |                            | 20  |     |     | ns             |

| MICROWIRE/PLUS Output Propagation             |                            |     |     | 150 |                |

| Delay (t <sub>UPD</sub> )                     |                            |     |     | 150 | ns             |

| Input Pulse Width                             |                            |     |     |     |                |

| Interrupt Input High Time                     |                            | 1   |     |     | t <sub>c</sub> |

| Interrupt Input Low Time                      |                            | 1   |     |     | t <sub>c</sub> |

AC Electrical Characteristics  $(-40^{\circ}C \le T_A \le +85^{\circ}C)$  (Continued) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                              | Conditions | Min     | Тур | Max | Units                  |

|----------------------------------------|------------|---------|-----|-----|------------------------|

| Timer 1 Input High Time                |            | 1       |     |     | t <sub>c</sub>         |

| Timer 1 Input Low Time                 |            | 1       |     |     | t <sub>c</sub>         |

| Timer 2, 3 Input High Time (Note 6)    |            | 1       |     |     | MCLK or t <sub>C</sub> |

| Timer 2, 3 Input Low Time (Note 6)     |            | 1       |     |     | MCLK or t <sub>C</sub> |

| Output Pulse Width                     |            |         |     |     |                        |

| Timer 2, 3 Output High Time            |            | 150     |     |     | ns                     |

| Timer 2, 3 Output Low Time             |            | 150     |     |     | ns                     |

| USART Bit Time when using External     |            | 6 CKI   |     |     |                        |

| СКХ                                    |            | periods |     |     | μs                     |

| USART CKX Frequency when being         |            |         |     | 2   | MHz                    |

| Driven by Internal Baud Rate Generator |            |         |     | 2   |                        |

| Reset Pulse Width                      |            | 1       |     |     | t <sub>c</sub>         |

|                                        |            |         |     | -   |                        |

t<sub>C</sub> = instruction cycle time.

Note 2: Maximum rate of voltage change must be < 0.5 V/ms.

Note 3: Supply and IDLE currents are measured with CKI driven with a square wave Oscillator, CKO driven 180° out of phase with CKI, inputs connected to V<sub>CC</sub> and outputs driven low but not connected to a load.

Note 4: The HALT mode will stop CKI from oscillating. Measurement of IDD HALT is done with device neither sourcing nor sinking current; with L. A. B, C, E, F, G0, and G2-G5 programmed as low outputs and not driving a load; all D outputs programmed low and not driving a load; all inputs tied to V<sub>CC</sub>; A/D converter and clock monitor and BOR disabled. Parameter refers to HALT mode entered via setting bit 7 of the G Port data register.

Note 5: Pins G6 and RESET are designed with a high voltage input network. These pins allow input voltages > V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages > V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). These two pins will not latch up. The voltage at the pins must be limited to < 14V. WARNING: Voltages in excess of 14V will cause damage to the pins. This warning excludes ESD transients.

Note 6: If timer is in high speed mode, the minimum time is 1 MCLK. If timer is not in high speed mode, the minimum time is 1 t<sub>C</sub>.

Note 7: Absolute Maximum Ratings should not be exceeded.

Note 8: V<sub>CC</sub> must be valid and stable before G6 is raised to a high voltage.

# DC Electrical Characteristics ( $-40^{\circ}C \le T_A \le +125^{\circ}C$ ) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                               | Conditions                                              | Min | Тур | Max                  | Units |

|-----------------------------------------|---------------------------------------------------------|-----|-----|----------------------|-------|

| Operating Voltage                       |                                                         | 4.5 |     | 5.5                  | V     |

| Power Supply Rise Time                  |                                                         | 10  |     | 50 x 10 <sup>6</sup> | ns    |

| Power Supply Ripple (Note 2)            | Peak-to-Peak                                            |     |     | 0.1 V <sub>CC</sub>  | V     |

| Supply Current (Note 3)                 |                                                         |     |     |                      |       |

| High Speed Mode                         |                                                         |     |     |                      |       |

| CKI = 10 MHz                            | $V_{\rm CC}$ = 5.5V, $t_{\rm C}$ = 0.5 µs               |     |     | 14.5                 | mA    |

| CKI = 3.33 MHz                          | $V_{CC}$ = 4.5V, $t_{C}$ = 1.5 µs                       |     |     | 7                    | mA    |

| Dual Clock Mode                         |                                                         |     |     |                      |       |

| CKI = 10 MHz, Low Speed OSC = 32 kHz    | $V_{\rm CC}$ = 5.5V, $t_{\rm C}$ = 0.5 µs               |     |     | 14.5                 | mA    |

| CKI = 3.33 MHz, Low Speed OSC = 32 kHz  | $V_{\rm CC}$ = 4.5V, $t_{\rm C}$ = 1.5 µs               |     |     | 7                    | mA    |

| Low Speed Mode                          |                                                         |     |     |                      |       |

| Low Speed OSC = 32 kHz                  | $V_{CC} = 5.5V$                                         |     | 65  | 110                  | μA    |

| HALT Current with BOR Disabled (Note 4) |                                                         |     |     |                      |       |

| High Speed Mode                         | $V_{CC}$ = 5.5V, CKI = 0 MHz                            |     | <4  | 40                   | μA    |

| Dual Clock Mode                         | $V_{CC}$ = 5.5V, CKI = 0 MHz, Low<br>Speed OSC = 32 kHz |     | <9  | 50                   | μA    |

| Low Speed Mode                          | $V_{CC}$ = 5.5V, CKI = 0 MHz, Low<br>Speed OSC = 32 kHz |     | <9  | 50                   | μA    |

| Idle Current (Note 3)                   |                                                         |     |     |                      |       |

| High Speed Mode                         |                                                         |     |     |                      |       |

| CKI = 10 MHz                            | $V_{\rm CC} = 5.5 V, t_{\rm C} = 0.5 \ \mu s$           |     |     | 2.7                  | mA    |

www.national.com

| Parameter                                                                              | Conditions                                      | Min                 | Тур  | Max                  | Units |

|----------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|------|----------------------|-------|

| Dual Clock Mode                                                                        |                                                 |                     |      |                      |       |

| CKI = 10 MHz, Low Speed OSC = 32 kHz                                                   | V <sub>CC</sub> = 5.5V, t <sub>C</sub> = 0.5 μs |                     |      | 2.7                  | mA    |

| Low Speed Mode                                                                         |                                                 |                     |      |                      |       |

| Low Speed OSC = 32 kHz                                                                 | $V_{\rm CC} = 5.5 V$                            |                     | 30   | 70                   | μA    |

| Supply Current for BOR Feature                                                         | V <sub>CC</sub> = 5.5V                          |                     |      | 45                   | μA    |

| High Brownout Trip Level (BOR Enabled)                                                 |                                                 | 4.17                | 4.28 | 4.5                  | V     |

| Input Levels (V <sub>IH</sub> , V <sub>IL</sub> )                                      |                                                 |                     |      |                      |       |

| Logic High                                                                             |                                                 | $0.8 V_{CC}$        |      |                      | V     |

| Logic Low                                                                              |                                                 |                     |      | 0.16 V <sub>CC</sub> | V     |

| Internal Bias Resistor for the CKI                                                     |                                                 | 0.0                 | 1.0  |                      | Mo    |

| Crystal/Resonator Oscillator                                                           |                                                 | 0.3                 | 1.0  | 2.5                  | MΩ    |

| Hi-Z Input Leakage                                                                     | $V_{\rm CC} = 5.5 V$                            | -3                  |      | +3                   | μA    |

| Input Pullup Current                                                                   | $V_{\rm CC} = 5.5 V, V_{\rm IN} = 0 V$          | -40                 |      | -250                 | μA    |

| Port Input Hysteresis                                                                  |                                                 | $0.25 V_{CC}$       |      |                      | V     |

| Output Current Levels                                                                  |                                                 |                     |      |                      |       |

| D Outputs                                                                              |                                                 |                     |      |                      |       |

| Source                                                                                 | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -6.3                |      |                      | mA    |

| Sink (Note 7)                                                                          | $V_{CC} = 4.5V, V_{OL} = 1.0V$                  | 9                   |      |                      | mA    |

| All Others                                                                             |                                                 |                     |      |                      |       |

| Source (Weak Pull-Up Mode)                                                             | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -9                  |      |                      | μA    |

| Source (Push-Pull Mode)                                                                | $V_{CC} = 4.5V, V_{OH} = 3.8V$                  | -6.3                |      |                      | mA    |

| Sink (Push-Pull Mode) (Note 7)                                                         | $V_{CC} = 4.5V, V_{OL} = 1.0V$                  | 9                   |      |                      | mA    |

| TRI-STATE Leakage                                                                      | $V_{CC} = 5.5V$                                 | -3                  |      | +3                   | μA    |

| Allowable Sink Current per Pin                                                         |                                                 |                     |      | 1                    | mA    |

| Maximum Input Current without Latchup (Note 5)                                         |                                                 |                     |      | ±200                 | mA    |

| RAM Retention Voltage, $V_R$ (in HALT Mode)                                            |                                                 | 2.0                 |      |                      | V     |

| Input Capacitance                                                                      |                                                 |                     |      | 7                    | pF    |

| Load Capacitance on D2                                                                 |                                                 |                     |      | 1000                 | pF    |

| Voltage on G6 to Force Execution from Boot<br>ROM(Note *NO TARGET FOR FNXref NS20196*) | G6 rise time must be slower than 100 ns         | 2 x V <sub>cc</sub> |      | V <sub>CC</sub> + 7  | V     |

| G6 Rise Time to Force Execution from Boot ROM                                          |                                                 | 100                 |      |                      | nS    |

| Input Current on G6 when Input > $V_{CC}$                                              | V <sub>IN</sub> = 11V, V <sub>CC</sub> = 5.5V   |                     | 500  |                      | μA    |

# AC Electrical Characteristics ( $-40^{\circ}C \le T_A \le +125^{\circ}C$ ) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                                                   | Conditions                             | Min | Тур | Max | Units          |

|-------------------------------------------------------------|----------------------------------------|-----|-----|-----|----------------|

| Instruction Cycle Time (t <sub>C</sub> )                    |                                        |     |     |     |                |

| Crystal/Resonator                                           | $4.5V \le V_{CC} \le 5.5V$             | 0.5 |     | DC  | μs             |

| Output Propagation Delay                                    | $R_{L} = 2.2k, C_{L} = 100 \text{ pF}$ |     |     |     |                |

| Frequency of MICROWIRE/PLUS in<br>Slave Mode                |                                        |     |     | 2   | MHz            |

| MICROWIRE/PLUS Setup Time (t <sub>UWS</sub> )               |                                        | 20  |     |     | ns             |

| MICROWIRE/PLUS Hold Time (t <sub>UWH</sub> )                |                                        | 20  |     |     | ns             |

| MICROWIRE/PLUS Output Propagation Delay (t <sub>UPD</sub> ) |                                        |     |     | 150 | ns             |

| Input Pulse Width                                           |                                        |     |     |     |                |

| Interrupt Input High Time                                   |                                        | 1   |     |     | t <sub>c</sub> |

AC Electrical Characteristics  $(-40^{\circ}C \le T_A \le +125^{\circ}C)$  (Continued) Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

| Parameter                              | Conditions | Min     | Тур | Max | Units                  |

|----------------------------------------|------------|---------|-----|-----|------------------------|

| Interrupt Input Low Time               |            | 1       |     |     | t <sub>c</sub>         |

| Timer 1 Input High Time                |            | 1       |     |     | t <sub>C</sub>         |

| Timer 1 Input Low Time                 |            | 1       |     |     | t <sub>C</sub>         |

| Timer 2, 3 Input High Time (Note 6)    |            | 1       |     |     | MCLK or t <sub>c</sub> |

| Timer 2, 3 Input Low Time (Note 6)     |            | 1       |     |     | MCLK or t <sub>c</sub> |

| Output Pulse Width                     |            |         |     |     |                        |

| Timer 2, 3 Output High Time            |            | 150     |     |     | ns                     |

| Timer 2, 3 Output Low Time             |            | 150     |     |     | ns                     |

| USART Bit Time when using External     |            | 6 CKI   |     |     |                        |

| СКХ                                    |            | periods |     |     |                        |

| USART CKX Frequency when being         |            |         |     | 2   | MHz                    |

| Driven by Internal Baud Rate Generator |            |         |     | 2   |                        |

| Reset Pulse Width                      |            | 0.5     |     |     | t <sub>c</sub>         |

|                                        |            |         |     |     |                        |

t<sub>C</sub> = instruction cycle time.

Note 9: Maximum rate of voltage change must be < 0.5 V/ms.

Note 10: Supply and IDLE currents are measured with CKI driven with a square wave Oscillator, CKO driven 180° out of phase with CKI, inputs connected to V<sub>CC</sub> and outputs driven low but not connected to a load.

Note 11: The HALT mode will stop CKI from oscillating. Measurement of I<sub>DD</sub> HALT is done with device neither sourcing nor sinking current; with L. A. B, C, E, F, G0, and G2–G5 programmed as low outputs and not driving a load; all D outputs programmed low and not driving a load; all inputs tied to V<sub>CC</sub>; A/D converter and clock monitor and BOR disabled. Parameter refers to HALT mode entered via setting bit 7 of the G Port data register.

Note 12: Pins G6 and  $\overrightarrow{\text{RESET}}$  are designed with a high voltage input network. These pins allow input voltages > V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages > V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). These two pins will not latch up. The voltage at the pins must be limited to < (V<sub>CC</sub> + 7V. WARNING: Voltages in excess of 14V will cause damage to the pins. This warning excludes ESD transients.

Note 13: If timer is in high speed mode, the minimum time is 1 MCLK. If timer is not in high speed mode, the minimum time is 1 t<sub>C</sub>.

Note 14: Absolute Maximum Ratings should not be exceeded.

Note 15:  $V_{cc}$  must be valid and stable before G6 is raised to a high voltage.

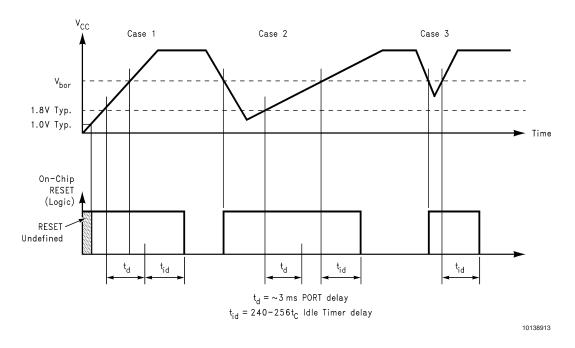

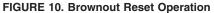

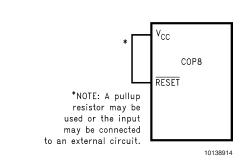

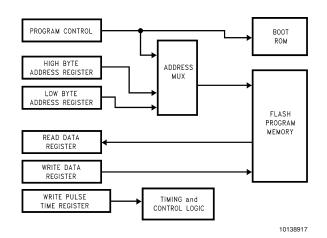

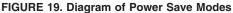

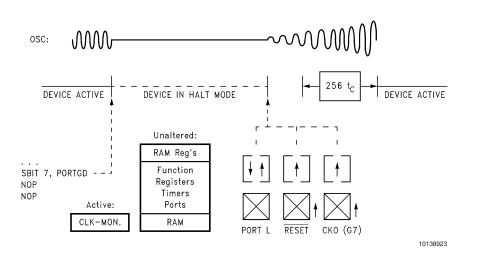

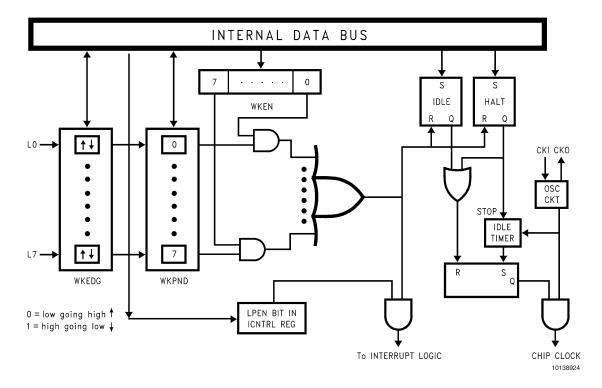

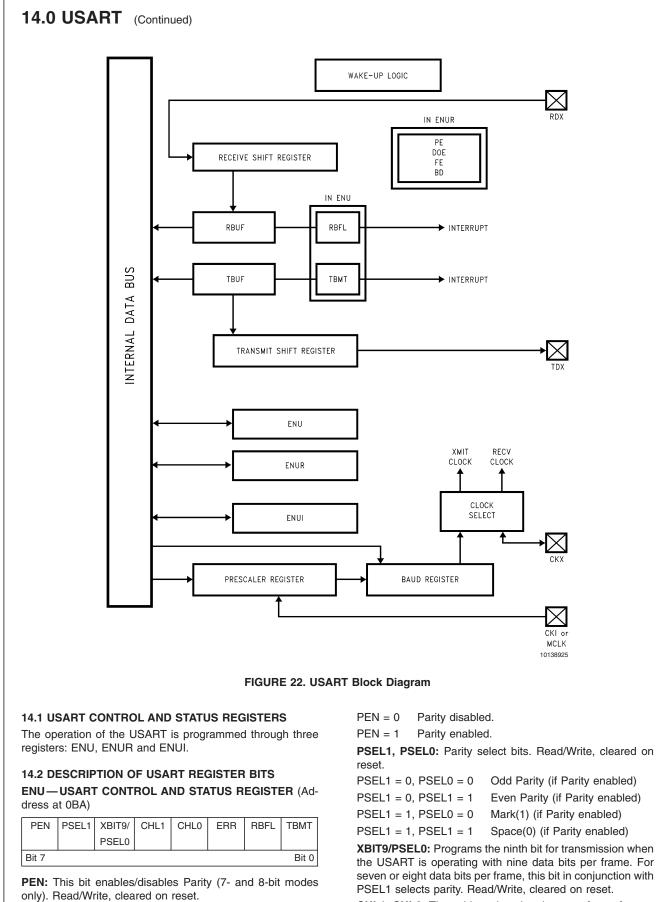

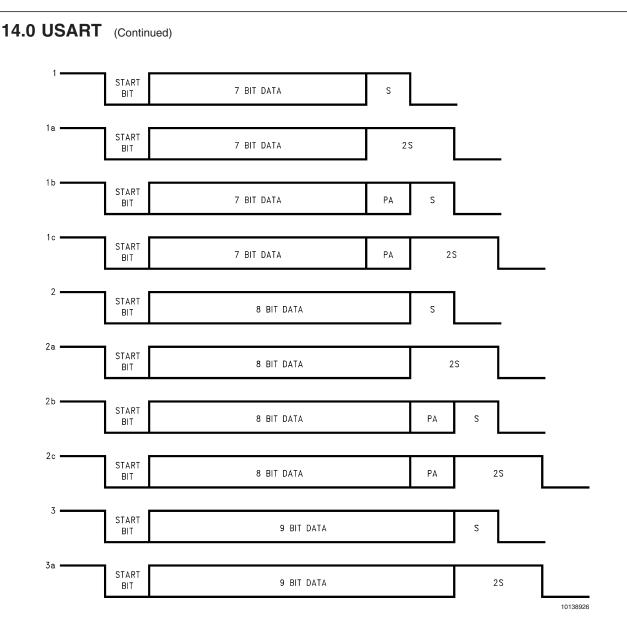

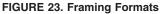

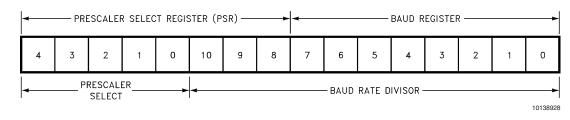

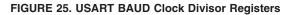

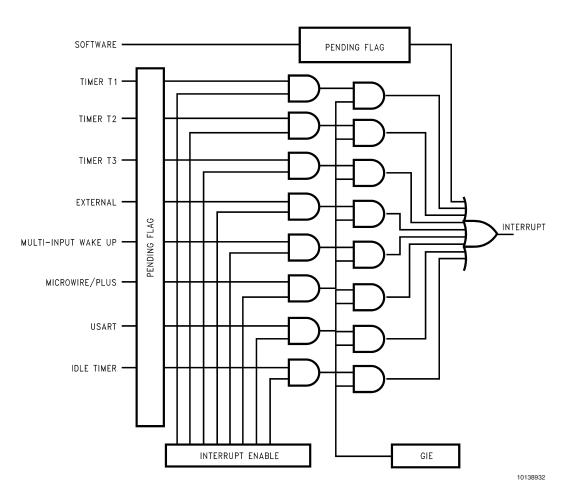

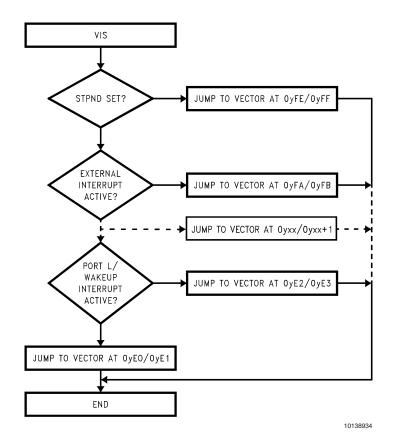

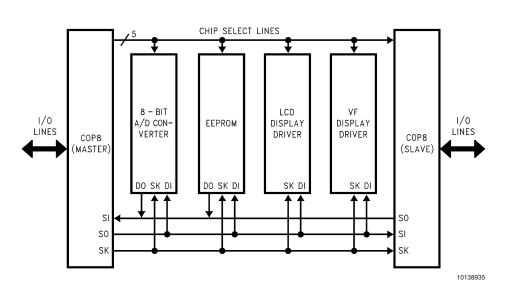

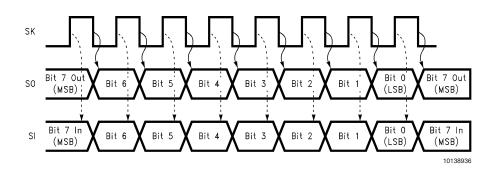

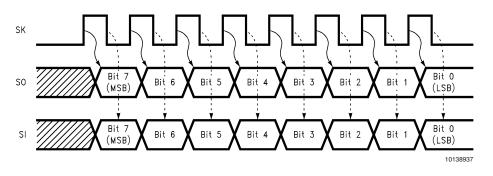

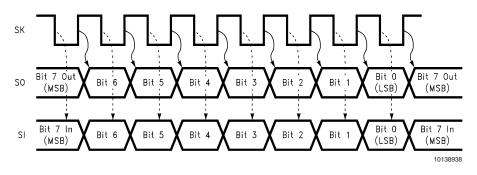

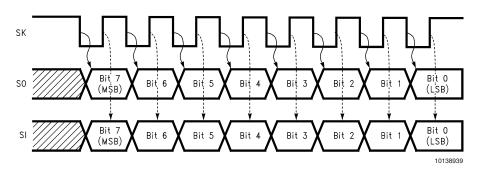

# 9.0 Pin Descriptions