# ±15 kV ESD Protected **Dual RS-422 Transceiver**

**ADM4168E Data Sheet**

#### **FEATURES**

**Dual transceivers for RS-422** ESD protection on bus input/output pins

±15 kV human body model (HBM)

±8 kV IEC 61000-4-2, contact discharge ±8 kV IEC 61000-4-2, air discharge

Complies with TIA/EIA-422-B and ITU-T recommendation V.11

Open-circuit fail-safe

Suitable for 5 V power supply applications Low supply current operation: 9 mA maximum

Low driver output skew

Receiver input impedance: 30 k $\Omega$

Receiver common-mode range: -7 V to +7 V

Power-up/power-down without glitches

16-pin TSSOP package

Operating temperature range: -40°C to +85°C

#### **APPLICATIONS**

**RS-422 interfaces** High data rate motor control Single-ended-to-differential signal conversion Point-to-point and multidrop transmission systems

#### **GENERAL DESCRIPTION**

The ADM4168E has dual RS-422 transceivers suitable for high speed communication on point-to-point and multidrop transmission lines. The ADM4168E is designed for balanced transmission lines and complies with TIA/EIA-422-B.

The differential driver outputs and receiver inputs feature electrostatic discharge circuitry that provides protection up to ±15 kV HBM and ±8 kV IEC 61000-4-2 (contact and air discharge).

The ADM4168E operates from a single 5 V power supply. Excessive power dissipation caused by bus contention or output shorting is prevented by short-circuit protection circuitry. Shortcircuit protection circuits limit the maximum output current to 150 mA during fault conditions.

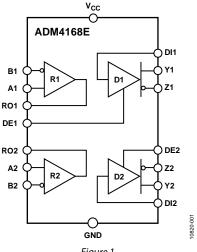

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The receivers of the ADM4168E contain a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

The ADM4168E is fully specified over the commercial and industrial temperature ranges and is available in a 16-pin TSSOP package.

# **TABLE OF CONTENTS**

| Features                 | 1 |

|--------------------------|---|

| Applications             | 1 |

| Functional Block Diagram | 1 |

| General Description      | 1 |

| Revision History         | 2 |

| Specifications           | 3 |

| Timing Specifications    | 4 |

| Absolute Maximum Ratings | 5 |

| Thermal Resistance       |   |

| ESD Caution              | 5 |

| Pin Configuration and Function Descriptions | 6    |

|---------------------------------------------|------|

| Typical Performance Characteristics         | 7    |

| Test Circuits and Switching Characteristics | 9    |

| Driver Measurements                         | 9    |

| Receiver Measurements                       | 9    |

| Theory of Operation                         | . 10 |

| Truth Tables                                | . 10 |

| Outline Dimensions                          | . 11 |

| Ordering Guide                              | . 11 |

## **REVISION HISTORY**

9/12—Revision 0: Initial Version

## **SPECIFICATIONS**

$4.5~{\rm V} \le {\rm V}_{\rm CC} \le 5.5~{\rm V}$ ; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted. All typical specifications are at  ${\rm T_A} = 25 {\rm ^oC}$ ,  ${\rm V}_{\rm CC} = 5.0~{\rm V}$ , unless otherwise noted.

Table 1.

| Parameter                                         | Symbol            | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                          |

|---------------------------------------------------|-------------------|------|-----|------|------|-----------------------------------------------------------------------------------|

| SUPPLY CURRENT                                    |                   |      |     |      |      | No load, drivers enabled                                                          |

| Total Package                                     | I <sub>cc</sub>   |      | 4   | 6    | mA   | $V_1 = V_{CC}$ or GND                                                             |

| -                                                 |                   |      | 5   | 9    | mA   | $V_1 = 2.4  \text{V or } 0.5  \text{V}^1$                                         |

| DRIVER                                            |                   |      |     |      |      |                                                                                   |

| Differential Outputs (Y1, Z1, Y2, Z2 Pins)        |                   |      |     |      |      |                                                                                   |

| Input Clamp Voltage                               | $V_{IK}$          |      |     | -1.5 | V    | $I_1 = -18 \text{ mA}$                                                            |

| Output Voltage High                               | $V_{OH}$          | 2.4  | 3.5 |      | V    | $V_{IH} = 2 \text{ V}, V_{IL} = 0.8 \text{ V}, I_{OH} = -20 \text{ mA}$           |

| Output Voltage Low                                | $V_{OL}$          |      | 0.2 | 0.4  | V    | $V_{IH} = 2 \text{ V}, V_{IL} = 0.8 \text{ V}, I_{OL} = 20 \text{ mA}$            |

| Differential Output Voltage                       |                   |      |     |      |      |                                                                                   |

| No Load                                           | $ V_{OD1} $       | 2.0  |     | 6.0  | V    | $I_0 = 0 \text{ mA}$                                                              |

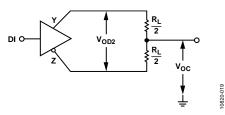

| Outputs Loaded <sup>2</sup>                       | $ V_{OD2} $       | 2.0  | 3.7 |      | V    | $R_L = 100 \Omega$ (see Figure 11)                                                |

| $\Delta  V_{OD} $ for Complementary Output States | $\Delta  V_{OD} $ |      |     | ±0.4 | V    | $R_L = 100 \Omega$ (see Figure 11)                                                |

| Common-Mode Output Voltage                        | V <sub>oc</sub>   |      |     | ±3.0 | V    | $R_L = 100 \Omega$ (see Figure 11)                                                |

| $\Delta  V_{OC} $ for Complementary Output States | $\Delta  V_{OC} $ |      |     | ±0.4 | V    | $R_L = 100 \Omega$ (see Figure 11)                                                |

| Output Leakage Current                            | Io                |      |     | 100  | μΑ   | $DE = 0 \text{ V}, V_{CC} = 0 \text{ V or } 5 \text{ V}, V_{O} = 6 \text{ V}$     |

|                                                   |                   | -100 |     |      | μΑ   | $DE = 0 \text{ V}, V_{CC} = 0 \text{ V or } 5 \text{ V}, V_{O} = -0.25 \text{ V}$ |

| Output Current (Short Circuit) <sup>3</sup>       | I <sub>os</sub>   | -30  |     | -150 | mA   | $V_0 = V_{CC}$ or GND                                                             |

| Input Capacitance                                 | Cı                |      | 6   |      | рF   |                                                                                   |

| Logic Inputs (DI, DE Pins)                        |                   |      |     |      |      |                                                                                   |

| Input Voltage High                                | $V_{IH}$          | 2.0  |     |      | V    |                                                                                   |

| Input Voltage Low                                 | $V_{IL}$          |      |     | 0.8  | V    |                                                                                   |

| Input Current High                                | I <sub>IH</sub>   |      |     | 1    | μΑ   | $V_{I} = V_{CC}$ or $V_{IH}$                                                      |

| Input Current Low                                 | I <sub>IL</sub>   |      |     | -1   | μΑ   | $V_I = GND \text{ or } V_{IL}$                                                    |

| RECEIVER                                          |                   |      |     |      |      |                                                                                   |

| Differential Inputs (A1, B1, A2, B2 Pins)         |                   |      |     |      |      |                                                                                   |

| Differential Input Threshold Voltage <sup>2</sup> | $V_{TH}$          | -200 |     | +200 | mV   |                                                                                   |

| Input Voltage Hysteresis                          | $V_{HYS}$         |      | 60  |      | mV   |                                                                                   |

| Input Current                                     | I <sub>1</sub>    |      |     | 1.5  | mA   | $V_1 = 7 V$ , other input at $0 V$                                                |

|                                                   |                   |      |     | -2.5 | mA   | $V_1 = -7 V$ , other input at $0 V$                                               |

| Line Input Resistance                             | R <sub>IN</sub>   | 12   | 30  |      | kΩ   | $V_{IC} = -7 \text{ V to } +7 \text{ V, other input at } 0 \text{ V}$             |

| Logic Outputs (RO1, RO2 Pins)                     |                   |      |     |      |      |                                                                                   |

| Output Voltage High                               | $V_{OH}$          | 3.8  | 4.2 |      | V    | $V_{ID} = 200 \text{ mV}, I_{OH} = -6 \text{ mA}$                                 |

| Output Voltage Low                                | V <sub>OL</sub>   |      | 0.1 | 0.3  | V    | $V_{ID} = -200 \text{ mV}, I_{OL} = 6 \text{ mA}$                                 |

$<sup>^1</sup>$  Measured per input with other inputs at V<sub>cc</sub> or GND.  $^2$  For exact conditions, see TIA/EIA-422-B.  $^3$  No more than one output shorted at any time, with the duration of the short not to exceed 1 second.

## **TIMING SPECIFICATIONS**

$4.5~{\rm V} \le {\rm V}_{\rm CC} \le 5.5~{\rm V}$ ; all minimum/maximum specifications apply over the entire recommended operation range, unless otherwise noted. All typical specifications are at  ${\rm T_A} = 25 {\rm ^{o}C}$ ,  ${\rm V}_{\rm CC} = 5.0~{\rm V}$ , unless otherwise noted.

Table 2.

| Parameter                 | Symbol                                | Min | Тур | Max | Unit | Test Conditions/Comments                                                       |

|---------------------------|---------------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------|

| DRIVER                    |                                       |     |     |     |      | $R_1$ , $R_2 = 50 \Omega$ ; $R_3 = 500 \Omega$ ; $C_1$ , $C_2$ , $C_3 = 40 pF$ |

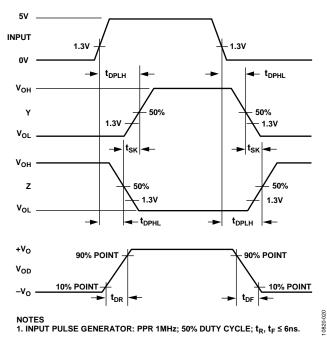

| Propagation Delay         | t <sub>DPLH</sub> , t <sub>DPHL</sub> |     | 8   | 16  | ns   | S1 open (see Figure 12 and Figure 13)                                          |

| <b>Driver Output Skew</b> | t <sub>sk</sub>                       |     | 1.5 | 4   | ns   | S1 open (see Figure 12 and Figure 13)                                          |

| Rise Time/Fall Time       | t <sub>DR</sub> , t <sub>DF</sub>     |     | 5   | 10  | ns   | S1 open (see Figure 12 and Figure 13)                                          |

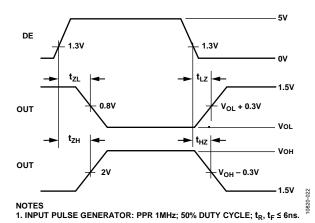

| Enable Time               | t <sub>zH</sub> , t <sub>zL</sub>     |     | 10  | 19  | ns   | S1 closed (see Figure 13 and Figure 14)                                        |

| Disable Time              | t <sub>HZ</sub> , t <sub>LZ</sub>     |     | 7   | 16  | ns   | S1 closed (see Figure 13 and Figure 14)                                        |

| RECEIVER <sup>1</sup>     |                                       |     |     |     |      |                                                                                |

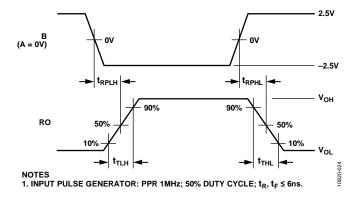

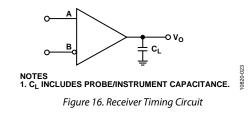

| <b>Propagation Delay</b>  | t <sub>RPLH</sub> , t <sub>RPHL</sub> | 9   | 15  | 27  | ns   | $C_L = 50 \text{ pF}$ (see Figure 15 and Figure 16)                            |

| Transition Time           | t <sub>TLH</sub> , t <sub>THL</sub>   |     | 4   | 9   | ns   | $V_{IC} = 0 \text{ V}, C_L = 50 \text{ pF (see Figure 15 and Figure 16)}$      |

$<sup>^{\</sup>rm 1}$  Measured per input with other inputs at  $\rm V_{\rm CC}$  or GND.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                               | Rating                                     |

|-----------------------------------------|--------------------------------------------|

| V <sub>cc</sub>                         | -0.3 V to +7 V                             |

| Digital Input Voltage (DE1, DE2)        | −0.3 V to +7 V                             |

| Driver Input Voltage (DI1, DI2)         | −0.3 V to +7 V                             |

| Receiver Output Voltage (RO1, RO2)      | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$ |

| Driver Output Voltage (Y1, Z1, Y2, Z2)  | −0.3 V to +7 V                             |

| Receiver Input Voltage (A1, B1, A2, B2) | -14 V to +14 V                             |

| Operating Temperature Range             | -40°C to +85°C                             |

| Storage Temperature Range               | −65°C to +150°C                            |

| ESD Protection on Ax, Bx, Yx, and Zx    |                                            |

| Human Body Model (HBM)                  | ±15 kV                                     |

| IEC 61000-4-2, Contact Discharge        | ±8 kV                                      |

| IEC 61000-4-2, Air Discharge            | ±8 kV                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 4. Thermal Resistance**

| Package Type  | $\theta_{JA}$ | Unit |

|---------------|---------------|------|

| 16-Lead TSSOP | 113           | °C/W |

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

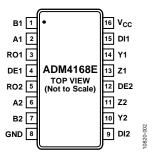

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                         |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | B1              | Inverting Receiver Input B, Transceiver 1.                                                                                                                                          |

| 2       | A1              | Noninverting Receiver Input A, Transceiver 1.                                                                                                                                       |

| 3       | RO1             | Receiver Output, Transceiver 1.                                                                                                                                                     |

| 4       | DE1             | Driver Output Enable, Transceiver 1. A logic high enables the differential driver outputs, Y1 and Z1; a logic low places the differential driver outputs in a high impedance state. |

| 5       | RO2             | Receiver Output, Transceiver 2.                                                                                                                                                     |

| 6       | A2              | Noninverting Receiver Input A, Transceiver 2.                                                                                                                                       |

| 7       | B2              | Inverting Receiver Input B, Transceiver 2.                                                                                                                                          |

| 8       | GND             | Ground.                                                                                                                                                                             |

| 9       | DI2             | Driver Input, Transceiver 2. When the driver is enabled, a logic low on DI2 forces Y2 low and Z2 high, whereas a logic high on DI2 forces Y2 high and Z2 low.                       |

| 10      | Y2              | Noninverting Driver Output Y, Transceiver 2.                                                                                                                                        |

| 11      | Z2              | Inverting Driver Output Z, Transceiver 2.                                                                                                                                           |

| 12      | DE2             | Driver Output Enable, Transceiver 2. A logic high enables the differential driver outputs, Y2 and Z2; a logic low places the differential driver outputs in a high impedance state. |

| 13      | Z1              | Inverting Driver Output Z, Transceiver 1.                                                                                                                                           |

| 14      | Y1              | Noninverting Driver Output Y, Transceiver 1.                                                                                                                                        |

| 15      | DI1             | Driver Input, Transceiver 1. When the driver is enabled, a logic low on DI1 forces Y1 low and Z1 high, whereas a logic high on DI1 forces Y1 high and Z1 low.                       |

| 16      | V <sub>cc</sub> | Power Supply (5 V $\pm$ 10%).                                                                                                                                                       |

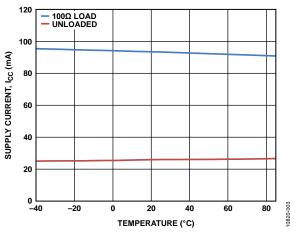

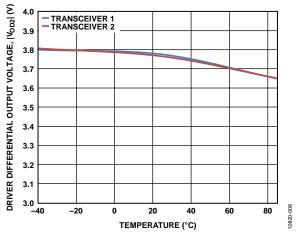

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Supply Current vs. Temperature, Data Rate = 10 Mbps

Figure 4. Driver Differential Output Voltage vs. Temperature

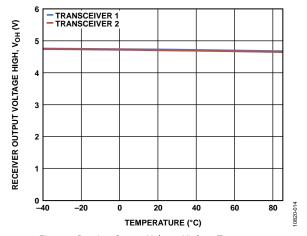

Figure 5. Receiver Output Voltage High vs. Temperature

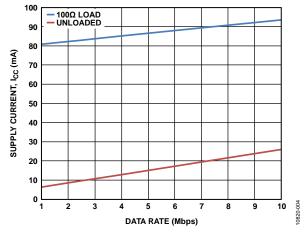

Figure 6. Supply Current vs. Data Rate

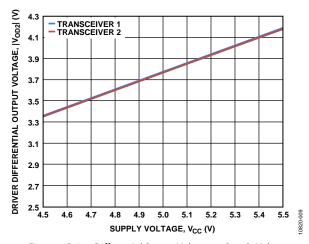

Figure 7. Driver Differential Output Voltage vs. Supply Voltage

Figure 8. Receiver Output Voltage Low vs. Temperature

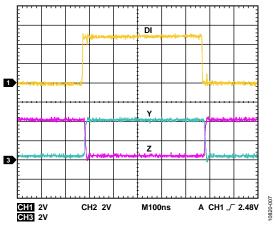

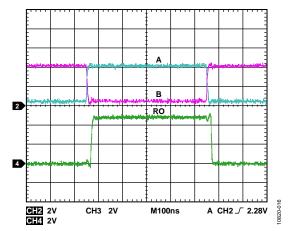

Figure 9. Driver Output

Figure 10. Receiver Output

## TEST CIRCUITS AND SWITCHING CHARACTERISTICS

## **DRIVER MEASUREMENTS**

Figure 11. Driver Voltage Measurements

Figure 12. Driver Propagation Delay and Rise/Fall Timing

# DIO $C_1$ $C_2$ $C_3$ $C_4$ $C_5$ $C_6$ $C_7$ $C_8$ $C_8$

NOTES 1.  $C_1$ ,  $C_2$ ,  $C_3$  INCLUDE PROBE/INSTRUMENT CAPACITANCE.

Figure 13. Driver Timing Circuit

Figure 14. Driver Enable/Disable Timing

## **RECEIVER MEASUREMENTS**

Figure 15. Receiver Propagation Delay and Transition Timing

## THEORY OF OPERATION

The ADM4168E is a dual RS-422 transceiver that operates from a single 5 V  $\pm$  10% power supply. The ADM4168E is intended for balanced data transmission and complies with TIA/EIA-422-B and ITU-T recommendation V.11. Each device contains two differential line drivers and two differential line receivers and is suitable for full-duplex data transmission.

The receivers contain a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

The ADM4168E features a low propagation delay, ensuring maximum baud rate operation. The balanced driver ensures distortion-free transmission.

Another important specification is a measure of the skew between the complementary outputs. Low skew enhances the noise immunity of the system and decreases the amount of electromagnetic interference (EMI).

## **TRUTH TABLES**

**Table 6. Abbreviations in Truth Tables**

| Letter | Description          |  |

|--------|----------------------|--|

| Н      | High level           |  |

| I      | Indeterminate        |  |

| L      | Low level            |  |

| Χ      | Irrelevant           |  |

| Z      | High impedance (off) |  |

Table 7. Transmitting (Each Driver)

| Inp | uts | Out | puts |

|-----|-----|-----|------|

| DE  | DI  | Z   | Υ    |

| Н   | Н   | L   | Н    |

| Н   | L   | Н   | L    |

| L   | Х   | Z   | Z    |

Table 8. Receiving (Each Receiver)

| Inputs                    | Output |

|---------------------------|--------|

| A – B                     | RO     |

| ≥ +0.2 V                  | Н      |

| ≤ −0.2 V                  | L      |

| -0.2  V < A - B < +0.2  V | 1      |

| Inputs open               | н      |

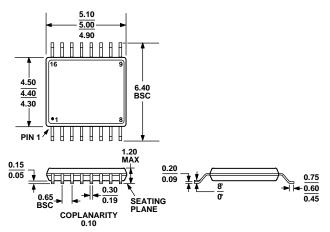

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153-AB

Figure 17. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADM4168EBRUZ       | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADM4168EBRUZ-RL7   | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| EVAL-ADM4168EEBZ   |                   | Evaluation Board                                  |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**