# Triple Output Step-Down Switching Regulator

### **Features and Benefits**

- Three buck converters

- 4.5 to 34 V input voltage range

- 550 kHz fixed frequency

- Multiphase switching

- Independent control of each converter

- Power-on-reset flag

- Internal compensation

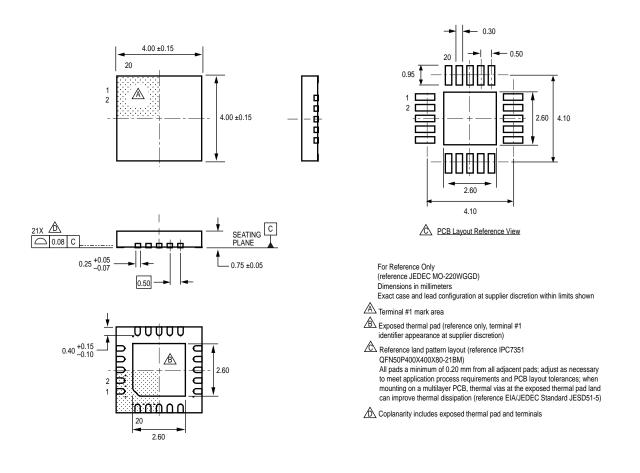

- 4 × 4 mm QFN Package, small PCB footprint

# Package: 20-contact QFN (suffix ES)

## Description

Designed to provide the power supply requirements of printers, office automation, industrial, and portable equipment, the A4490 provides three high current, high performance, switching regulator outputs with independent soft start.

High frequency switching allows selection of inexpensive inductors and small ceramic output capacitors. The turn-on cycles of the regulators are interleaved to minimize stresses on the input capacitors and to reduce EMI. A charge pump is used to provide the supply for driving the power switches, ensuring operation at very wide operating duty cycles and avoiding the need for power-draining clamp circuits.

A power-on-reset circuit with user configurable delay indicates when enabled regulators are in specification. The power-onreset flag also indicates when the input voltage drops below specification, giving the system controller advance warning while the switchers continue to operate down to the shutdown level.

Internal diagnostics provide comprehensive protection against overloads, input undervoltages, and overtemperatures.

Continued on the next page...

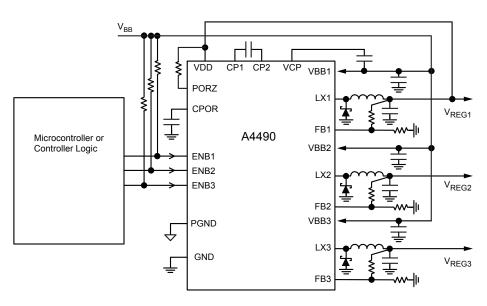

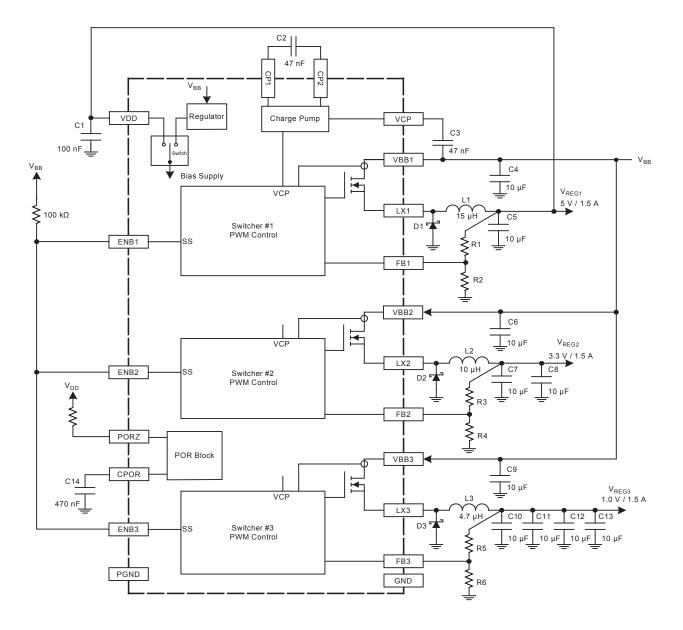

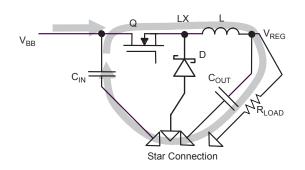

# **Typical Application**

#### **Description (continued)**

The A4490 is provided in a 20-contact, 4 mm  $\times$  4 mm, 0.75 mm nominal overall height QFN, with exposed pad for enhanced thermal dissipation. It is lead (Pb) free, with 100% matte tin leadframe plating.

Applications include the following:

- Photo, inkjet, and portable printers

- Industrial

- Hand-held devices

- Portable applications

#### **Selection Guide**

| Part Number  | Packing                    | Operating Temperature Range<br>(°C) |

|--------------|----------------------------|-------------------------------------|

| A4490EESTR-T | 1500 pieces per 7-in. reel | -40 to 85                           |

#### Absolute Maximum Ratings (reference to GND)

| Characteristic                | Symbol               | Notes                                      | Rating     | Units |

|-------------------------------|----------------------|--------------------------------------------|------------|-------|

| Load Supply Voltage           | V <sub>BB</sub>      |                                            | 36         | V     |

| LX1, LX2, and LX3 Pins        | V <sub>LXn</sub>     |                                            | -1 to 36   | V     |

| PORZ and VDD Pins             | V <sub>IN</sub>      |                                            | -0.3 to 7  | V     |

| ENBx Pin Input Current        | I <sub>ENBx</sub>    | Driven by a current-limited voltage source | 1          | mA    |

| Operating Ambient Temperature | T <sub>A</sub>       | Range E                                    | -40 to 85  | °C    |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                                            | 150        | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                            | -55 to 150 | °C    |

#### **Recommended Operating Conditions**

| Characteristic                | Symbol           | Conditions                                                                                                               | Min. | Тур. | Max. | Units |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Load Supply Voltage           | V <sub>BB</sub>  | To operate at $V_{BB}$ < 6 V, connect $V_{DD}$<br>supply to the $V_{BB}$ supply. See Powering<br>Configurations section. | 4.5  | _    | 34   | V     |

| LX1, LX2, and LX3 Pins        | V <sub>LXn</sub> |                                                                                                                          | -0.7 | -    | 34   | V     |

| Operating Ambient Temperature | T <sub>A</sub>   |                                                                                                                          | -40  | -    | 85   | °C    |

| Junction Temperature          | TJ               |                                                                                                                          | -40  | _    | 125  | °C    |

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol          | Test Conditions*                       | Value | Units |

|----------------------------|-----------------|----------------------------------------|-------|-------|

| Package Thermal Resistance | $R_{\theta JA}$ | On 4-layer PCB based on JEDEC standard | 37    | °C/W  |

\*Additional thermal information available on the Allegro website.

# **Functional Block Diagram**

Note: All capacitors ceramic X5R.

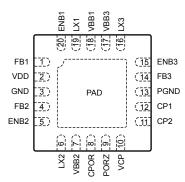

## **Pin-out Diagram**

#### **Terminal List**

| Number | Name              | Function                                     |

|--------|-------------------|----------------------------------------------|

| 1      | FB1               | Feedback REG1                                |

| 2      | VDD               | Bias supply                                  |

| 3      | GND <sup>1</sup>  | Ground                                       |

| 4      | FB2               | Feedback REG2                                |

| 5      | ENB2              | Enable REG2, logic input, active high        |

| 6      | LX2               | Switch node REG2                             |

| 7      | VBB2 <sup>2</sup> | Input supply for REG2                        |

| 8      | CPOR              | POR delay adjustment                         |

| 9      | PORZ              | Power on reset output, active low            |

| 10     | VCP               | Charge pump reservoir                        |

| 11     | CP2               | Charge pump capacitor terminal               |

| 12     | CP1               | Charge pump capacitor terminal               |

| 13     | PGND <sup>1</sup> | Ground for charge pump circuitry             |

| 14     | FB3               | Feedback REG3                                |

| 15     | ENB3              | Enable REG3, logic input, active high        |

| 16     | LX3               | Switch node REG3                             |

| 17     | VBB3 <sup>2</sup> | Input supply for REG3                        |

| 18     | VBB1 <sup>2</sup> | Input supply for REG1                        |

| 19     | LX1               | Switch node REG1                             |

| 20     | ENB1              | Enable REG1, logic input, active high        |

| -      | PAD <sup>3</sup>  | Exposed pad for enhanced thermal dissipation |

<sup>1</sup>GND and PGND should be connected externally.

<sup>2</sup>The three VBBx pins should be connected together externally.

<sup>3</sup>Thermal pad should be connected to the ground (0 V) plane using thermal vias.

### ELECTRICAL CHARACTERISTICS<sup>1,2</sup> at $T_A = 25^{\circ}$ C, $V_{BB} = 6.0$ to 34 V, $V_{DD}$ supplied externally, unless noted otherwise

| Characteristics                        | Symbol              | Test Conditions                                                                                                                                                  | Min.  | Тур. | Max.  | Unit |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| General                                |                     |                                                                                                                                                                  |       |      |       |      |

| VBB Quiescent Current                  | I <sub>BBON</sub>   | ENBx = high, $I_{LOAD}$ = 0 mA, $V_{BB}$ = 12 V, current drawn by feedback resistors ignored                                                                     | _     | 1    | 2     | mA   |

|                                        | I <sub>BBOFF</sub>  | ENBx = 0 V                                                                                                                                                       | -     | 1    | -     | μA   |

| VDD Supply Range                       | V <sub>DD</sub>     |                                                                                                                                                                  | 3.3   | -    | 5.5   | V    |

| VDD Quiescent Current                  |                     | ENBx = high                                                                                                                                                      | -     | -    | 5     | mA   |

| VDD Quescent Current                   | I <sub>DD</sub>     | ENBx = 0 V                                                                                                                                                       | -     | 1    | -     | μA   |

| REG1, REG2, and REG3                   | ·                   |                                                                                                                                                                  |       |      |       |      |

| Feedback Input Bias Current            | I <sub>BIAS</sub>   |                                                                                                                                                                  | -400  | -100 | 100   | nA   |

| Feedback Voltage                       | V <sub>FB</sub>     | With respect to 0.8 V target voltage                                                                                                                             | -     | ±1.5 | -     | %    |

| Output Voltage Degulation3             | N                   | $V_{\text{REGx}} = 5 \text{ V}, \text{ I}_{\text{OUT}} = 0 \text{ to } 1.5 \text{ A}, \text{ T}_{\text{A}} = -20^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$ | -2.5  | -    | 2.5   | %    |

| Output Voltage Regulation <sup>3</sup> | V <sub>OUT</sub>    | $V_{\text{REGx}}$ = 5 V, $I_{\text{OUT}}$ = 0 to 1.5 A, $T_{\text{A}}$ = -40°C to 85°C                                                                           | -3.5  | -    | 3.5   | %    |

| PWM Frequency                          | f <sub>SW</sub>     |                                                                                                                                                                  | 470   | 550  | 630   | kHz  |

| Maximum Duty Cycle                     | D <sub>max</sub>    |                                                                                                                                                                  | 90    | -    | -     | %    |

| Minimum Duty Cycle                     | D <sub>min</sub>    |                                                                                                                                                                  | -     | 5    | -     | %    |

|                                        |                     | T <sub>J</sub> = 25°C, I <sub>LOAD</sub> = 1.5 A, V <sub>BB</sub> = 6.0 V                                                                                        | -     | 450  | -     | mΩ   |

| Buck Switch On-Resistance              |                     | $T_{J}$ = 125°C, I <sub>LOAD</sub> = 1.5 A, V <sub>BB</sub> = 6.0 V                                                                                              | -     | 700  | -     | mΩ   |

| Buck Switch On-Resistance              | R <sub>DS(on)</sub> | $T_J$ = 25°C, I <sub>LOAD</sub> = 1.5 A, V <sub>BB</sub> = 4.5 V                                                                                                 | -     | 560  | -     | mΩ   |

|                                        |                     | $T_{J}$ = 125°C, I <sub>LOAD</sub> = 1.5 A, V <sub>BB</sub> = 4.5 V                                                                                              | -     | 870  | -     | mΩ   |

| Current Limit Threshold                | I <sub>LIM</sub>    | Peak current through switch with D = 0.9                                                                                                                         | 2.0   |      |       | Α    |

| Soft Start Duration                    | t <sub>ss</sub>     |                                                                                                                                                                  | 0.625 | 1.25 | 1.875 | ms   |

| Logic Inputs and Outputs               |                     |                                                                                                                                                                  |       |      |       |      |

| ENBx Input Voltage                     | V <sub>IL</sub>     |                                                                                                                                                                  | -     | -    | 0.8   | V    |

| LINDX Input Voltage                    | V <sub>IH</sub>     |                                                                                                                                                                  | 2.0   | -    | -     | V    |

| ENBx Input Hysteresis                  | V <sub>I(hys)</sub> |                                                                                                                                                                  | 300   | 500  | -     | mV   |

| ENBx Input Current                     | I <sub>IL</sub>     | $V_{IH} \leq 5 V$                                                                                                                                                | -1    | -    | 1     | μA   |

| PORZ Output (Open Drain)               | V <sub>PORZL</sub>  | I <sub>PORZL</sub> = 1 mA, fault asserted                                                                                                                        | -     | -    | 0.4   | V    |

| PORZ Output Leakage Current            | I <sub>PORZH</sub>  | V <sub>PORZ</sub> = 5 V, fault not asserted                                                                                                                      | -1    | -    | 1     | μA   |

| Power-On Reset Duration                | t <sub>POR</sub>    | C <sub>POR</sub> = 470 nF                                                                                                                                        | 75    | 115  | 155   | ms   |

Continued on the next page...

#### ELECTRICAL CHARACTERISTICS<sup>1,2</sup> (continued) at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 6.0 to 34 V, V<sub>DD</sub> supplied externally, unless noted otherwise

| Characteristics                                  | Symbol                     | Test Conditions                                                   | Min. | Тур. | Max. | Unit             |  |

|--------------------------------------------------|----------------------------|-------------------------------------------------------------------|------|------|------|------------------|--|

| Protection                                       | Protection                 |                                                                   |      |      |      |                  |  |

| VREGx Undervoltage Lockout Startup               | V <sub>REGUV(su)</sub>     | FB1, FB2, and FB3 rising                                          | -    | 85   | -    | %V <sub>FB</sub> |  |

| VREGx Undervoltage Lockout Shutdown              | V <sub>REGUV(sd)</sub>     | FB1, FB2, and FB3 falling                                         | -    | 80   | _    | %V <sub>FB</sub> |  |

| VREGx Undervoltage Lockout<br>Startup Hysteresis | V <sub>REGUV(suhys)</sub>  |                                                                   | -    | 5    | _    | %                |  |

| VPP Lindervoltage Leekout Startup                | V <sub>BBUV(su)</sub>      | No external VDD supply, $V_{BB}$ rising                           | 3.9  | 4.3  | 4.6  | V                |  |

| VBB Undervoltage Lockout Startup                 | V <sub>BBCPUV(su)</sub>    | External VDD supply, V <sub>BB</sub> rising                       | 3.9  | 4.2  | 4.4  | V                |  |

| VBB Undervoltage Lockout Shutdown                | V <sub>BBUV(sd)</sub>      | No external VDD supply, V <sub>BB</sub> falling                   | 3.7  | 4.1  | 4.5  | V                |  |

|                                                  | V <sub>BBCPUV(sd)</sub>    | External VDD supply, V <sub>BB</sub> falling                      | 3.0  | 3.5  | 4.1  | V                |  |

| VBB Undervoltage Lockout<br>Shutdown Hysteresis  | V <sub>BBUV(sdhys)</sub>   | No external VDD supply                                            | -    | 500  | -    | mV               |  |

|                                                  | V <sub>BBCPUV(sdhys)</sub> | External VDD supply                                               | -    | 600  | -    | mV               |  |

| VBB Undervoltage Warning Threshold               | V <sub>BBUV(por)</sub>     | $V_{BB}$ falling (forces PORZ low); switchers continue to operate | _    | 3.6  | _    | V                |  |

| Junction Overtemperature Shutdown                | T <sub>JTSD</sub>          | Temperature rising                                                | -    | 165  | -    | °C               |  |

| Junction Overtemperature Shutdown<br>Hysteresis  | T <sub>JTSD(hys)</sub>     | Recovery = T <sub>JTSD</sub> –T <sub>JTSD(hys)</sub>              | -    | 15   | _    | °C               |  |

<sup>1</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified pin.

<sup>2</sup>Specifications over the junction temperature range of –40°C to 125°C are assured by design and characterization.

<sup>3</sup>Average value of V<sub>OUT</sub> relative to target voltage. The effects of the feedback resistors are not taken into account.

# **Functional Description**

#### **Basic Operation**

The A4490 contains three fixed frequency, buck switching converters with peak current-mode control, including slope compensation. Each converter can be independently turned on and off via the enable inputs (EN1, EN2, and EN3), which are active high. When enabled, the corresponding output is brought-up under the control of a soft start routine, which avoids output voltage overshoot and minimizes input inrush current.

The output voltage is typically divided down by an external potential divider, and is compared against an internal reference voltage to produce an error signal, also known as the *current demand signal*. The current signal through the buck switch is converted into a voltage. This signal is then compared against the current demand signal to create the required duty cycle.

At the beginning of each switching cycle, the buck switch is turned on. When the current signal through the switch reaches the level of the current demand signal, the on-time of the switch is terminated. On the next switching cycle, the switch is turned on again and the cycle is repeated.

One shared clock is used to define the switching frequency for each regulator. Each of the three switching cycles (REG1, REG2, and REG3) are phase shifted with respect to one another by 120° in an attempt to minimize the pulsed current drawn from the input filter capacitors. Under certain conditions, for example at low  $V_{BB}$  conditions and relatively high user-set output voltages, switching overlap between channels is inevitable.

Under conditions, such as light loads or high  $V_{BB}$  voltages, that cause duty cycles (DC) of less than the minimum value, the converter enters a pulse-skipping mode to ensure regulation is maintained.

A charge pump regulator is provided to ensure a sufficient gate drive is available for all three power switches across the full input voltage range. This regulator allows operation even at very wide operating duty cycles. On initial power-up, an internal regulator is used to provide the bias supply for on-chip control functions.

Each regulator channel utilizes pulse-by-pulse current limiting in the event of either a short circuit or an overload. If the overload is applied long enough, the IC temperature may rise sufficiently to cause the thermal shutdown circuit to operate. The part will auto-restart under control of the soft start circuit after the thermal disable condition is removed, and assuming all other conditions are met. See the Shutdown section for more information.

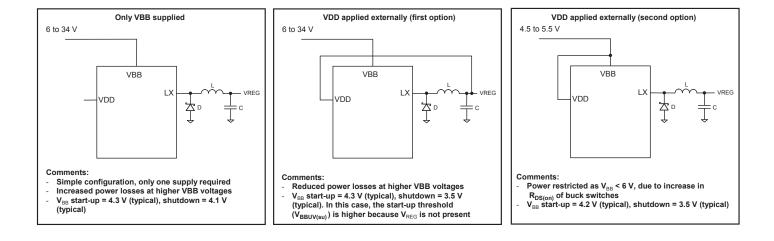

#### **Power Configuration**

The A4490 supports alternative schemes for providing logic supply voltage on the VDD pin. In addition, the IC can be powered up and down using either the VBB or ENB pins.

**Powering VDD** To minimize power dissipation, especially at high input voltages, it is recommended that an external supply be applied to the VDD input pin. Typically, this voltage is derived from one of the three regulated outputs that are set-up for between 3.3 and 5 V ( $V_{REGx}$ ).

Another advantage of powering the VDD externally is that the VBB undervoltage lockout level is lowered. To maximize the run time of the switchers during a VBB power-down condition, two alternative undervoltage shutdown conditions are supported, depending on which VDD-powering configuration has been implemented. When no external VDD is applied, the minimum  $V_{BB}$ ,  $V_{BBUV(sd)}$ , is 4.1 V typical. When an external VDD is applied, the minimum  $V_{BB}$ ,  $V_{BBUV(sd)}$ , is 4.1 V typical. When an external VDD is applied, the minimum  $V_{BB}$ ,  $V_{BBCPUV(sd)}$ , is 3.5 V typical.

One note of caution when deriving VDD from a VREG output: during initial application of  $V_{BB}$ , the internal bias supply automatically starts from the internal regulator because VREG has not yet reached regulation. This means the startup threshold is determined by  $V_{BBUV(su)}$  (4.3 V typical) because there is no external VDD. When VREG has begun to supply VDD externally, the shutdown threshold reduces to  $V_{BBCPUV(sd)}$  (3.5 V typical). This assumes that  $V_{REG}$  is present.

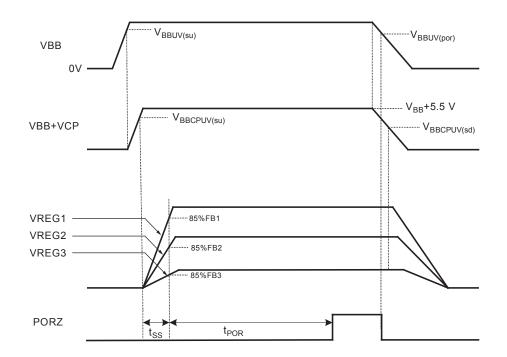

**Powering Up and Down with VBB** Referring to figure 1, each of the enable inputs (ENBx) are held high by being tied to the  $V_{BB}$  rail via a 100 k $\Omega$  resistor and the VDD is supplied from one of the regulator outputs. When the  $V_{BB}$  voltage reaches the minimum threshold,  $V_{BBUV(su)}$ , the charge pump supply (VCP) ramps up. When  $V_{BB} + V_{CP}$  has reached the minimum threshold  $V_{BBCPUV(su)}$ , the soft start routines are initiated (t<sub>SS</sub>) for all three regulator channels (VREGx). When all three regulators have reached the 85% FBx threshold, the power-on-reset timer is initiated. After the power-on-reset period, t<sub>POR</sub>, has elapsed, PORZ goes high, indicating that all the regulators and  $V_{BB}$  are in specification.

Figure 1. Timing diagram for powering up and down using the VBB pin

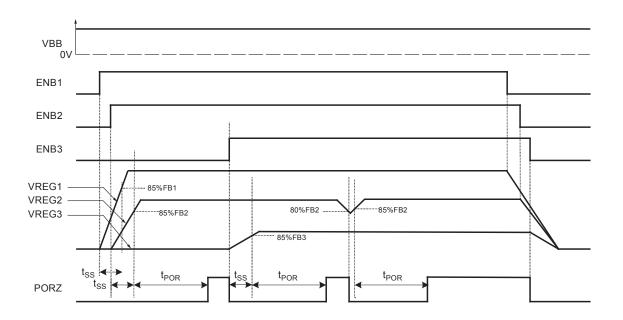

Figure 2. Timing diagram for powering up and down using the ENB pin

When the  $V_{BB}$  voltage starts to fall below the undervoltage warning level,  $V_{BBUV(por)}$ , of 3.6 V typical, the PORZ flag resets. This gives advance warning to the system controller that the  $V_{BB}$  voltage is falling. Note that this feature is only guaranteed when VDD is supplied externally. During this interval, the three switchers continue to operate.

While  $V_{BB}$  falls further, the VCP supply also tends to fall, which degrades the drive voltage to the series switches. In addition, the higher voltage rails start to fall out of regulation first, as the corresponding maximum duty cycle ( $D_{max}$ ) for these particular converters is reached.

The regulators that have the lower output voltages achieve some level of steady state, before the A4490 powers down when all of the corresponding  $V_{BB}$  undervoltage thresholds have been reached. For example, it may be possible for a 1 V output to continue to operate down to a  $V_{BB}$  of 3.4 V typical, if the VDD supply is derived externally. The extent of this effect depends on a myriad of factors, including input and output filter capacitance, output loads, gate drive amplitude, MOSFET  $R_{DS(on)}$ , and so forth.

**Powering Up and Down with Enable** Referring to figure 2,  $V_{BB}$  is present and the UVLO start-up thresholds,  $V_{BBUV(su)}$  and  $V_{BBCPUV(su)}$  have been reached. Each of the regulators are enabled in turn. Initially, VREG1 is enabled and is brought-up under the control of the soft start circuit ( $t_{SS}$ ). Before VREG1 reaches 85% FB1, VREG2 is enabled and is brought-up under a separate soft start control.

When both regulators have reached their respective 85% FB thresholds, the power-on-reset (POR) timer is initiated. Note that the POR timer is only enabled after all of the enabled regulators reach their corresponding 85% FB levels. After the power-on-reset time,  $t_{POR}$ , has elapsed, if the FB levels of VREG1 and VREG2 are not below their respective 80% FB levels, then the PORZ signal will go high.

At some point later, if VREG3 is enabled, then the PORZ is reset and VREG3 is brought-up under the control of the soft start circuit. When the 85% FB3 threshold is reached, the POR timer is initiated. After  $t_{POR}$  has elapsed, if all the FB levels are above their respective 80% FB levels, then the PORZ signal will go high.

Note that if any regulator channel is not enabled, the channel will not influence PORZ. To avoid multiple signal changes of the

PORZ signal, it is recommended that the system be designed such that all three regulator channels are within specification before  $t_{POR}$  has elapsed.

If any regulator channel drops below 80% FB, the PORZ signal will be reset. If the voltage then recovers to within 85% FB, the POR timer is initiated again. Note that a soft start is not initiated when the feedback voltage drops below the 80% FB level. This is to allow a rapid auto-restart in the event of an overload or similar fault. If a soft start is required, it is recommended that on receipt of the PORZ reset signal, the system controller disables and then re-enables the relevant regulator channels again. As soon as the last regulator is disabled the PORZ signal is reset.

**Power on Reset** The power-on-reset duration,  $t_{POR}$ , is determined by selecting an appropriate capacitor connected to the CPOR pin. The value of  $t_{POR}$  can be determined by the following formula:

$$t_{\rm POR} = 2.131 \times 10^5 \times C_{\rm POR}$$

. (1)

The PORZ output goes high when both  $V_{\rm BB}$  is above the undervoltage warning levels, and the FB pins of the regulators that are enabled are > 85% of the  $V_{\rm REG}$  voltage.

Because the external capacitor is charged via a 5  $\mu$ A current source, care must be taken in the layout to avoid additional leakage paths. The capacitor should be positioned adjacent to the CPOR pin, and the ground connection to the A4490 GND pin should be as short as possible.

It is recommended that the  $t_{POR}$  period be set to exceed the start-up phases of all three regulators, to avoid the possibility of multiple triggerings of the PORZ output.

**Output Voltage Selection** The output voltage on each of the three regulators is set by the following relationship, shown here for the VREG1 channel:

$$R_1 = R_2 \left( \frac{V_{\text{REG1}}}{V_{\text{FB}}} - 1 \right) \quad , \tag{2}$$

where R2 (connected between GND and the FB1 pin) should be a value between 4.7 and 12 k $\Omega$ . R1 is connected between the output rail and the FB1 pin. V<sub>REG1</sub> is the set output regulator voltage. V<sub>FB</sub> is the reference voltage.

The tolerances of the feedback resistors influence the voltage setpoint. It is therefore important to consider the tolerance selection when targeting an overall regulation figure.

The bias current,  $I_{BIAS}$ , flowing out of the FB1 node into R2, will introduce a small voltage offset to the output.

**Enable** Each regulator channel can be individually enabled via the corresponding ENBx pin. If any channel is required to startup automatically after the VBB voltage is applied, that particular channel should have the ENB pin tied to the VBB rail via a pullup resistor.

This resistor should be selected to limit the current to less than the maximum specified value, 1 mA. This prevents the internal protection clamps from turning on. It is recommended that a 100 k $\Omega$  pull-up resistor be used. This would ensure the current remains below the maximum value when V<sub>BB</sub> = 36 V.

**Soft Start** Each regulator channel contains a soft start circuit. A soft start cycle is initiated when the appropriate regulator enable input is set to high; the  $V_{BB}$ , charge pump, and bias supply voltages are above the minimum values; and no thermal shutdown condition exists. Note that an overload or short circuit will not cause a soft start cycle, unless a thermal shutdown event occurs.

During a soft start cycle, the reference voltage is ramped from 0 to 0.8 V typical, which in turn forces the current demand signal to increase in a linear fashion.

**Shutdown** All converter channels are disabled in the event of either a thermal shutdown event or an undervoltage on VBB  $(V_{BBUV(sd)} \text{ or } V_{BBCPUV(sd)}).$

As soon as the above fault conditions have been removed, and assuming the ENB inputs are enabled, the appropriate channels will auto-restart under control of the soft start.

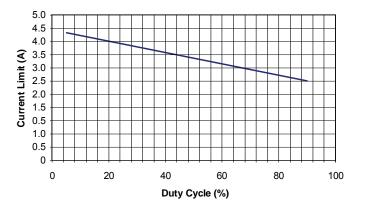

**Current Limit** The typical peak current limit for each channel is specified as 2.5 A minimum, with a duty cycle of 0.9. The minimum current limit occurs at maximum duty cycle (0.9), because the slope compensation has a maximum effect under this condition. As the duty cycle reduces, the current limit increases. This means for applications that operate with a narrow duty cycle, it is possible to operate with a load current greater than 2.0 A.

Figure 3 illustrates the typical peak current limit versus duty cycle. For example, it is possible to operate with a peak current limit of 3.75 A with a duty cycle of 0.3.

As well as ensuring the peak current limit is not exceeded, under worst case load and input voltage conditions, it is also important to check the implications on the thermal performance. See the Thermal Considerations section.

#### **Component Selection**

**Inductor** The inductance value, L, determines the ripple current. It is important to ensure that the minimum current limit is not exceeded under worst-case conditions:  $V_{BB}(min)$ ,  $I_{LOAD}(max)$ ,  $f_{SW}(min)$ , and L(min).

It is recommended that gapped ferrite solutions be used as opposed to powdered iron solutions, the latter of which exhibit relatively high core losses that can have a large impact on long term reliability.

Inductors are typically specified at two current levels, rms current and saturation current. With regard to the rms current, it is important to understand how the rms current level is specified, in terms of ambient temperature. Some manufacturers quote an ambient only, whilst others quote a temperature that includes a self-induced temperature rise. For example, if an inductor is rated for 85°C and includes a self-induced temperature rise of 25°C at maximum load, then the inductor cannot be safely operated beyond an ambient temperature of 60°C at full load. The rms current can be assumed to be simply the maximum load current, with perhaps some margin to allow for overloads, and so forth.

The first stage of determining the inductor value is to specify a peak-to-peak ripple current of typically about 20% to 25% of the maximum load.

Figure 3. Current limit versus duty cycle

The maximum peak-to-peak ripple current,  $I_{RIPPLE}$ , occurs at the maximum input voltage. Therefore the duty cycle, D, should be found under these conditions (for the VREG1 channel):

$$D(\min) = \frac{V_{\text{REG1}} + V_{\text{f}}}{V_{\text{BB}}(\max) + V_{\text{f}}}$$

(3)

where V<sub>f</sub> is the forward voltage drop of the recirculation diode.

The required inductance can be found:

$$L(\min) = \frac{V_{BB}(\max) - V_{REG1}}{I_{RIPPLE}} \times D(\min) \times \frac{1}{f_{SW}(\min)} \quad (4)$$

Note that the manufacturers inductance tolerance should also be taken into account. This value may be as high as  $\pm 20\%$ . The peak-to-peak current should not exceed 1 A, to avoid instability in the innermost circuit loops due to insufficient slope compensation.

The maximum peak current can be found from to ensure that the saturation current level of the chosen inductor is not exceeded:

$$I_{\text{sat}} = I_{\text{LOAD}} + \frac{I_{\text{RIPPLE}}}{2} \quad . \tag{5}$$

Recommended inductor manufacturers and ranges are:

- Taiyo Yuden: NR6045 series for 1.5 A outputs

- Taiyo Yuden: NRG4026 series for 1.0 A outputs

- Sumida: CDH74 series for 1.5 A outputs

**Output Capacitor** In the interests of size, cost and performance, it is highly recommended that ceramic X5R or X7R capacitor types be used. When using ceramic capacitors another important consideration is the E-field effects on the actual value of the capacitor. To minimize the effects of the capacitance reducing with output voltage, it is recommended that the working voltage of the capacitor be considerably more than the set output voltage. As a suggestion, it is recommended that 6.3 V-rated capacitors should be used for output voltages of 3.3 V and below. For output voltages of 5 V, a 10 V-rated capacitor should be used.

The output capacitor determines the output voltage ripple and is used to close the control loop. To guarantee stability, the capacitance has to increase as the output voltage is reduced. This is actually reasonable from a ripple voltage point of view, as the ripple voltage is typically specified as a percentage of output voltage.

The following table outlines what the minimum output capacitance should be for a given output voltage:

| Output Voltage<br>(V) | Minimum Output Capacitance<br>(μF) |

|-----------------------|------------------------------------|

| 15                    | 3.3                                |

| 12                    | 4.7                                |

| 5                     | 10                                 |

| 3.3                   | 20                                 |

| 1.8 to 2.5            | 30                                 |

| <1.8                  | 40                                 |

Capacitance values with greater than the above values can be used with the effect of reducing the bandwidth. This may be necessary in systems that have extremely low ripple/noise requirements.

The output ripple is largely determined by the output capacitance and the effects of ESR and ESL can largely be ignored assuming good layout practice is observed.

The output voltage ripple can be approximated to:

$$V_{\text{RIPPLE}} \approx \frac{I_{\text{RIPPLE}}}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}$$

, (6)

When using ceramic capacitors, there is generally no need to consider the current carrying capability due to the negligible heating effects of the ESR. Also, the rms current flowing into the output capacitor is extremely low.

**Input Capacitor** Again it is highly recommended that ceramic, X5R or X7R capacitors be used.

The value of the input capacitance determines the amount of current ripple (EMI) that appears at the source ( $V_{BB}$  supply) terminals. The amounts of current flowing in and out of the input capacitor depend on the relative impedances between the input capacitor impedance and the source impedance. To achieve a low impedance filter solution it is recommended to place at least two capacitors in parallel.

Again, there is generally no need to consider the heating effects of the rms current flowing through the ESR. Also, the phaseshifting of the input current drawn by each of the regulators helps to reduce the overall rms current.

**Flyback Diode** This diode conducts during the switch off-time. A Schottky diode is recommended to minimize both the forward drop and switching losses.

The worst case dissipation occurs at maximum  $V_{BB}$ , when the duty cycle, D, is a minimum. The average current through the diode can be found:

$$I_{\text{DIODE(av)}} = I_{\text{LOAD}} \times (1 - D(\min)) \quad . \tag{7}$$

The forward voltage drop,  $V_f$ , can be found from the diode characteristics by using the actual load current (not the average current).

The static power dissipation can be found:

$$P_{\text{STAT}} = I_{\text{LOAD(av)}} \times V_{\text{f}} \quad . \tag{8}$$

It is also important to take into account the thermal rating of the package,  $R_{\theta JA}$ , and the ambient temperature, to ensure that enough heatsinking is provided to maintain the diode junction temperature within the safe operating area for the device.

To minimize the heating effects from the A4490 on the diode and vice-versa, it is recommended that the diode be mounted on the reverse side of the printed circuit board.

**Support Components** POR capacitor (C11), charge pump capacitor (C1), reservoir capacitor (C2) and VDD filter capacitor (C12) should be ceramic X5R or X7R.

#### **Thermal Considerations**

To ensure the A4490 operates in the safe operating area, which effectively means restricting the junction temperature to less than 150°C, several checks should be made. The general approach is to work out what thermal impedance ( $R_{\theta JA}$ ) is required to maintain the junction temperature at a given level, for a particular power dissipation.

Another factor worth considering is that other power dissipating components on the system PCB may influence the thermal performance of the A4490. For example, the power loss contribution from the recirculation diode and the sense resistor may cause the junction temperature of the A4490 to be higher than expected.

The following steps can be used as a guideline for determining a suitable thermal solution. It should be noted that this process is usually an iterative one to achieve the optimum solution. These factors can be considered as follows:

Step 1. Estimate the maximum ambient temperature,  $T_A(max)$ , of the application.

Step 2. Define the maximum junction temperature,  $T_J(max)$ . Note that the absolute maximum is 150°C.

Step 3. Determine the worst case power dissipation,  $P_D(max)$ .

The evaluation should consider these at maximum load and minimum  $V_{BB}$ . Contributors are switch static and dynamic losses, and control losses. These are described in the following sections

**Switch Static Losses** The following steps can be used to determine switch static losses:

Estimate the maximum duty cycle:

$$D(\max) = \frac{V_{REG} + V_f}{V_{BB}(\min) + V_f} , \qquad (9)$$

where  $V_{\rm f}$  is the forward voltage drop of the Schottky diode under the given load current.

Estimate the  $R_{DS(on)}$  of the each regulator switch at the given junction temperature:

$$R_{\rm DS(on)TJ} = R_{\rm DS(on)25C} \left( 1 + \frac{T_{\rm J} - 25}{200} \right) \qquad . \tag{10}$$

Note that if the V<sub>BB</sub> range is restricted to between 4.5 and 5.5 V, the R<sub>DS(on)</sub> increases. For example, the R<sub>DS(on)</sub> at 25°C with a V<sub>BB</sub> greater than 6 V is 450 m $\Omega$  typical, as stated in the Electrical Characteristics table. Under the same temperature conditions, with the V<sub>BB</sub> = 4.5 V, the R<sub>DS(on)</sub> is 560 m $\Omega$  typical. For VBB voltages between 4.5 and 6 V, the R<sub>DS(on)</sub> can be found by linear approximation. For more information on operating the A4490 between a V<sub>BB</sub> voltage of 4.5 and 5.5 V, see the Power Configurations section.

The static loss for each switch can be determined:

$$P_{\text{STAT}} = I_{\text{LOAD}}^2 \times D(\text{max}) \times R_{\text{DS(on)TJ}} \quad , \tag{11}$$

where  $I_{LOAD}$  is the load for that particular regulator channel.

**Switch Dynamic Losses** The following can be used to determine switch dynamic losses:

Both turn on and turn off losses can be estimated:

$$P_{\rm DYN} = V_{\rm BB}(\rm min) \times \frac{I_{\rm LOAD}}{2} \times 30 \times 10^{-9} \times f_{\rm SW} \quad , \qquad (12)$$

where  $\boldsymbol{f}_{SW}$  is the switching frequency.

**Control Losses** The following steps can be used to determine control losses:

$$P_{\rm VBB} = I_{\rm BBON} \times V_{\rm BB} \quad , \tag{13}$$

where  $I_{\rm BBON}$  is the quiescent current assuming all three regulators are on.

$$P_{\rm VDD} = I_{\rm VDD} \times V_{\rm DD} \quad , \tag{14}$$

where  $I_{\text{VDD}}$  and is the quiescent current on VDD.

Total Losses The total losses can now be estimated:

$$P_{\text{TOTAL}} = P_{\text{STAT1}} + P_{\text{STAT2}} + P_{\text{STAT2}}$$

$$+ P_{\text{DYN1}} + P_{\text{DYN2}} + P_{\text{DYN3}}$$

$$+ P_{\text{VBB}} + P_{\text{VDD}} \quad . \tag{15}$$

Thermal Impedance The thermal impedance required for the

solution can now be determined:

$$R_{\theta JA} = \frac{T_J - T_A}{P_{\text{TOTAL}}} \qquad (16)$$

#### Example

Selected parameters:  $V_{BB}(min) = 6 V$   $V_{REG1} = 5 V \text{ at } 1 A$   $V_{REG2} = 3.3 V \text{ at } 1 A$   $V_{REG3} = 1.8 V \text{ at } 800 \text{ mA}$   $T_A = 70^{\circ}C$   $T_J = 115^{\circ}C$  $V_f = 0.4 V$  (a) Switch static losses

$V_{\text{REG1}} \text{ duty cycle, } D_1 = \frac{5+0.4}{6+0.4} = 0.84$  $V_{\text{REG2}} \text{ duty cycle, } D_2 = \frac{3.3+0.4}{6+0.4} = 0.58$  $V_{\text{REG3}} \text{ duty cycle, } D_3 = \frac{1.8+0.4}{6+0.4} = 0.34$

The R<sub>DS(on)</sub> of each switch can be found:

$$R_{\text{DS(on)TJ}} = 450 \times 10^{-3} \left( 1 + \frac{115 - 25}{200} \right) = 0.653 \,\Omega$$

The static loss of each switch can be found:  $P_{\text{STAT1}} = 1^2 \times 0.84 \times 0.653 = 0.55 \text{ W}$   $P_{\text{STAT2}} = 1^2 \times 0.58 \times 0.653 = 0.379 \text{ W}$  $P_{\text{STAT3}} = 0.8^2 \times 0.34 \times 0.653 = 0.14 \text{ W}$

(b) Switch dynamic losses

$$P_{\text{DYN1}} = 6 \times \frac{1}{2} \times 30 \times 10^{-9} \times 500 \times 10^{3} = 0.045 \text{ W}$$

$$P_{\text{DYN2}} = 6 \times \frac{1}{2} \times 30 \times 10^{-9} \times 500 \times 10^{3} = 0.045 \text{ W}$$

$$P_{\text{DYN3}} = 6 \times \frac{0.8}{2} \times 30 \times 10^{-9} \times 500 \times 10^{3} = 0.036 \text{ W}$$

(c) Control losses  $P_{VBB} = 0.005 \times 6 = 0.03 \text{ W}$  $P_{VDD} = 0.001 \times 3.3 = 0.003 \text{ W}$

- (d) The total power dissipation can now be found:  $P_{TOTAL} = 0.55 + 0.379 + 0.14 + 0.045$ + 0.045 + 0.036 + 0.03 + 0.003 = 1.228 W

- (e) The thermal impedance required for the solution can be found:

$$R_{\theta \text{JA}} = \frac{115 - 70}{1.228} = 36.6 \text{ °C/W}$$

For this particular solution a high thermal efficiency board is required to ensure the junction temperature is kept below 115°C. For maximum effectiveness, the PCB pad area underneath the thermal pad of the A4490 should be exposed copper. Several thermal vias (say between 4 and 8) should be used to connect the thermal pad to the internal ground plane. If possible, an additional thermal copper plane should be applied to the bottom side of the PCB and connected to the thermal pad of the A4490 through the vias.

# A4490

This calculation assumes no thermal influence from other components. If possible, it is advisable to mount the flyback diodes on the reverse side of the printed circuit board. Ensure low impedance electrical connections are implemented between board layers.

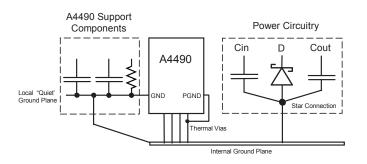

**PCB Layout Guidelines** The ground plane is largely dictated by the thermal requirements described in the previous section. The ground referenced power components should be referenced to a star ground, located away from the A4490 to minimize ground bounce issues.

A small, local, relatively quiet ground plane near the A4490 should be used for the ground referenced support components, to minimize interference effects of ground noise from the power circuitry. Figure 4 illustrates the recommended grounding architecture.

Figure 4. Ground plane configurations

To avoid ground bounce and offset issues, it is highly recommended that the ground referenced feedback resistors (R2, R4, and R6) should be connected as close to the GND connection of the A4490 as possible.

A local quiet ground plane around these components can be implemented, however, this ground plane should have a high impedance connection to the star connection of the power stages.

If a ground plane is used, it is recommended that it does not overlap the switching nodes (LX1, LX2, and LX3) to avoid the possibility of noise pick-up. To minimize the possibility of noise injection issues, it is recommended to isolate the ground plane around high impedance nodes such as: FBx, ENBx and CPOR.

In terms of grounding the power components, a star connection should be made to minimize the ground loop impedances. Note that although a ground plane may be required to meet the thermal characteristics of the solution it is still imperative to implement a ground star connection for the power components. The ground for the charge pump (PGND) should be connected to the thermal vias.

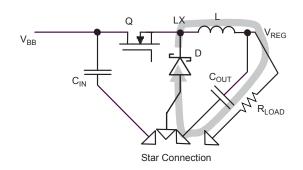

Figures 5 and 6 below illustrates the importance of keeping the ground connections as short as possible and forming good star connections.

Figure 5 also illustrates the current conduction paths during the on-cycle of the switching FET. The following points should be noted:

• The capacitor  $C_{\rm IN}$  should be placed as close as possible to the VBB terminals. The capacitance should be split between the VBB terminals for  $V_{\rm REG1}$  and  $V_{\rm REG3}$  and the VBB terminal for  $V_{\rm REG2}$ .

Figure 5. FET on-cycle current conduction paths

Figure 6. FET off-cycle current conduction paths

The VBB terminals for  $V_{REG1}$  and  $V_{REG2}$  should be connected via short and wide traces to the VBB terminal for  $V_{REG3}$ .

• Each inductor should be connected as close as possible to the respective switching FET (LX1, LX2, and LX3) and output capacitors.

Figure 6 shows the current conduction path during the off-cycle of the switching FET. The following points should be noted:

- The diode D should be placed as close as possible to both the switching FET and the inductor.

- Support components: POR capacitor (C11), charge pump capacitor (C1), reservoir capacitor (C2), and VDD filter capacitor (C12) should be located as close as possible to their respective terminal connections. The ground referenced capacitors should be connected as close to the GND terminal as possible.

**Powering Configurations** The following three diagrams show typical configurations for providing power to the application. The middle diagram corresponds to the typical application shown on the front page.

Copyright ©2008-2010, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com