## SINGLE 2 INPUT POSITIVE NAND GATE

#### Description

The 74LVCE1G00 is a single 2-input positive NAND gate with a standard totem pole output. The device is designed for operation with a power supply range of 1.4V to 5.5V. The inputs are tolerant to 5.5V allowing this device to be used in a mixed voltage environment. The device is fully specified for partial power down applications using  $I_{OFF}$ . The  $I_{OFF}$  circuitry disables the output preventing damaging current backflow when the device is powered down.

The gate performs the positive Boolean function:

### $Y = \overline{A \bullet B} \text{ or } Y = \overline{A} + \overline{B}$

#### Features

- Extended Supply Voltage Range from 1.4 to 5.5V

- Switching speed characterized for operation at 1.5V

- Offers 30% speed improvement over LVC at 1.8V.

- ± 24mA Output Drive at 3.3V

- CMOS low power consumption

- IOFF Supports Partial-Power-Down Mode Operation

- Inputs accept up to 5.5V

- ESD Protection Tested per JESD 22

Exceeds 200-V Machine Model (A115-A)

Exceeds 2000-V Human Body Model (A114-A)

- Latch-Up Exceeds 100mA per JESD 78, Class II

- Range of Package Options

- Direct Interface with TTL Levels

- SOT25, SOT353, and DFN1410: Assembled with "Green" Molding Compound (no Br, Sb)

- Lead Free Finish/ RoHS Compliant (Note 1)

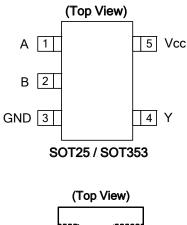

### Pin Assignments

#### Applications

- Voltage Level Shifting

- General Purpose Logic

- Wide array of products such as.

- PCs, networking, notebooks, netbooks, PDAs

- o Computer peripherals, hard drives, CD/DVD ROM

- o TV, DVD, DVR, set top box

- o Cell Phones, Personal Navigation / GPS

- o MP3 players ,Cameras, Video Recorders

- Notes: 1. EU Directive 2002/95/EC (RoHS). All applicable RoHS exemptions applied. Please visit our website at http://www.diodes.com/products/lead\_free.html.

- 2. Pin 2 and pin 5 of the DFN1410 package are internally connected.

## SINGLE 2 INPUT POSITIVE NAND GATE

## **Pin Descriptions**

| Pin Name | Description    |  |  |  |

|----------|----------------|--|--|--|

| А        | Data Input     |  |  |  |

| В        | Data Input     |  |  |  |

| GND      | Ground         |  |  |  |

| Y        | Data Output    |  |  |  |

| Vcc      | Supply Voltage |  |  |  |

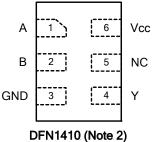

# Logic Diagram

## **Function Table**

| Inp | Output |   |

|-----|--------|---|

| Α   | В      | Y |

| Н   | Н      | L |

| L   | Х      | Н |

| Х   | L      | Н |

## SINGLE 2 INPUT POSITIVE NAND GATE

### Absolute Maximum Ratings (Note 3)

| Symbol           | Description                                                           | Rating                       | Unit |

|------------------|-----------------------------------------------------------------------|------------------------------|------|

| ESD HBM          | Human Body Model ESD Protection                                       | 2                            | KV   |

| ESD MM           | Machine Model ESD Protection                                          | 200                          | V    |

| V <sub>CC</sub>  | Supply Voltage Range                                                  | -0.5 to 6.5                  | V    |

| VI               | Input Voltage Range                                                   | -0.5 to 6.5                  | V    |

| Vo               | Voltage applied to output in high impedance or I <sub>OFF</sub> state | -0.5 to 6.5                  | V    |

| Vo               | Voltage applied to output in high or low state                        | -0.3 to V <sub>CC</sub> +0.5 | V    |

| I <sub>IK</sub>  | Input Clamp Current V <sub>I</sub> <0                                 | -50                          | mA   |

| Ι <sub>ΟΚ</sub>  | Output Clamp Current                                                  | -50                          | mA   |

| Ι <sub>ο</sub>   | Continuous output current                                             | ±50                          | mA   |

|                  | Continuous current through Vdd or GND                                 | ±100                         | mA   |

| TJ               | Operating Junction Temperature                                        | -40 to 150                   | C    |

| T <sub>STG</sub> | Storage Temperature                                                   | -65 to 150                   | °C   |

Note: 3. Stresses beyond the absolute maximum may result in immediate failure or reduced reliability. These are stress values and device operation should be within recommend values.

## SINGLE 2 INPUT POSITIVE NAND GATE

## **Recommended Operating Conditions (Note 4)**

| Symbol                                  |                                | Parameter                                      | Min                    | Max                     | Unit |

|-----------------------------------------|--------------------------------|------------------------------------------------|------------------------|-------------------------|------|

|                                         |                                | Operating                                      | 1.4                    | 5.5                     | V    |

| V <sub>cc</sub>                         | Operating Voltage              | Data retention only                            | 1.2                    |                         | V    |

|                                         |                                | $V_{\rm CC} = 1.4$ V to 1.95 V                 | 0.65 X V <sub>CC</sub> |                         |      |

|                                         |                                | $V_{\rm CC}$ = 2.3 V to 2.7 V                  | 1.7                    |                         | Ň    |

| V <sub>IH</sub> Hig                     | High-level Input Voltage       | $V_{\rm CC} = 3  \text{V}$ to 3.6 V            | 2                      |                         | V    |

|                                         |                                | $V_{\rm CC} = 4.5 \text{ V to } 5.5 \text{ V}$ | 0.7 X V <sub>CC</sub>  |                         |      |

|                                         |                                | $V_{\rm CC} = 1.4$ V to 1.95 V                 |                        | $0.35 \text{ X V}_{CC}$ |      |

| N                                       |                                | $V_{\rm CC}$ = 2.3 V to 2.7 V                  |                        | 0.7                     |      |

| V <sub>IL</sub> Low-level input voltage | Low-level input voltage        | $V_{\rm CC}$ = 3 V to 3.6 V                    |                        | 0.8                     | V    |

|                                         |                                | $V_{\rm CC} = 4.5 \text{ V to } 5.5 \text{ V}$ |                        | 0.3 X V <sub>CC</sub>   |      |

| VI                                      | Input Voltage                  |                                                | 0                      | 5.5                     | V    |

| Vo                                      | Output Voltage                 |                                                | 0                      | V <sub>cc</sub>         | V    |

|                                         | High-level output current      | Vcc=1.4 V                                      |                        | -3                      |      |

|                                         |                                | V <sub>CC</sub> = 1.65 V                       |                        | -4                      | 0    |

|                                         |                                | V <sub>CC</sub> = 2.3 V                        |                        | -8                      |      |

| I <sub>OH</sub>                         |                                |                                                |                        | -16                     | mA   |

|                                         |                                | $V_{CC} = 3 V$                                 |                        | -24                     |      |

|                                         |                                | $V_{CC} = 4.5 V$                               |                        | -32                     |      |

|                                         |                                | Vcc=1.4 V                                      |                        | 3                       |      |

|                                         |                                | V <sub>CC</sub> = 1.65 V                       |                        | 4                       |      |

|                                         |                                | $V_{CC} = 2.3 V$                               |                        | 8                       | mA   |

| I <sub>OL</sub>                         | Low-level output current       |                                                |                        | 16                      |      |

|                                         |                                | $V_{CC} = 3 V$                                 |                        | 24                      |      |

|                                         |                                | V <sub>CC</sub> = 4.5 V                        |                        | 32                      |      |

|                                         |                                | $V_{CC} = 1.4 \text{ to } 3V$                  |                        | 20                      |      |

| Δt/ΔV                                   | Input transition rise or fall  | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$     |                        | 10                      | ns/\ |

|                                         | rate                           | $V_{CC} = 5 V \pm 0.5 V$                       |                        | 5                       |      |

| T <sub>A</sub>                          | Operating free-air temperature |                                                | -40                    | 85                      | ٥C   |

Note: 4. Unused inputs should be held at Vcc or Ground.

## SINGLE 2 INPUT POSITIVE NAND GATE

### Electrical Characteristics (All typical values are at Vcc = 3.3V, T<sub>A</sub> = 25°C)

| Symbol            | Parameter                                 | Test Conditions                                                     | Vcc           | Min            | Тур. | Max  | Unit |  |

|-------------------|-------------------------------------------|---------------------------------------------------------------------|---------------|----------------|------|------|------|--|

|                   |                                           | I <sub>OH</sub> = -100µА                                            | 1.4 V to 5.5V | $V_{CC} - 0.1$ |      |      |      |  |

|                   |                                           | I <sub>OH</sub> = -3mA                                              | 1.4 V         | 1.05           |      |      |      |  |

|                   |                                           | I <sub>ОН</sub> = -4mA                                              | 1.65 V        | 1.2            |      |      |      |  |

| V <sub>OH</sub>   | High Level Output<br>Voltage              | I <sub>OH</sub> = -8mA                                              | 2.3V          | 1.9            |      |      | V    |  |

|                   | vollage                                   | I <sub>OH</sub> = -16mA                                             | 2.14          | 2.4            |      |      |      |  |

|                   |                                           | I <sub>OH</sub> = -24mA                                             | 3 V           | 2.3            |      |      |      |  |

|                   |                                           | I <sub>OH</sub> = -32mA                                             | 4.5 V         | 3.8            |      |      |      |  |

|                   |                                           | I <sub>OL</sub> = 100μA                                             | 1.4 V to 5.5V |                |      | 0.1  |      |  |

|                   |                                           | I <sub>OL</sub> = 3mA                                               | 1.4 V         |                |      | .4   |      |  |

|                   |                                           | I <sub>OL</sub> = 4mA                                               | 1.65 V        |                |      | 0.45 |      |  |

| V <sub>OL</sub>   | High-level Input Voltage                  | I <sub>OL</sub> = 8mA                                               | 2.3V          |                |      | 0.3  | V    |  |

|                   |                                           | I <sub>OL</sub> = 16mA                                              | 0.14          |                |      | 0.4  | -    |  |

|                   |                                           | I <sub>OL</sub> = 24mA                                              | 3 V           |                |      | 0.55 |      |  |

|                   |                                           | I <sub>OL</sub> = 32mA                                              | 4.5           |                |      | 0.55 |      |  |

| I <sub>I</sub>    | Input Current                             | $V_1 = 5.5 \text{ V or GND}$                                        | 0 to 5.5 V    |                |      | ± 5  | μA   |  |

| I <sub>OFF</sub>  | Power Down Leakage<br>Current             | $V_1 \text{ or } V_0 = 5.5 V$                                       | 0             |                |      | ± 10 | μA   |  |

| I <sub>cc</sub>   | Supply Current                            | $V_1 = 5.5V \text{ of GND}$<br>$I_0=0$                              | 1.4 V to 5.5V |                |      | 10   | μA   |  |

| ΔI <sub>CC</sub>  | Additional Supply<br>Current              | One input at $V_{CC}$ –<br>0.6 V Other inputs<br>at $V_{CC}$ or GND | 3 V to 5.5V   |                |      | 500  | μA   |  |

| Ci                | Input Capacitance                         | $V_i = V_{CC} - or GND$                                             | 3.3           |                | 3.5  |      | pF   |  |

|                   |                                           | SOT25                                                               | (Note 5)      |                | 204  |      |      |  |

| $\theta_{JA}$     | Thermal Resistance<br>Junction-to-Ambient | SOT353                                                              | (Note 5)      |                | 371  |      | °C/W |  |

|                   |                                           | DFN1410                                                             | (Note 5)      |                | 430  |      | 1    |  |

|                   |                                           | SOT25                                                               | (Note 5)      |                | 52   |      |      |  |

| $\theta_{\rm JC}$ | Thermal Resistance                        | SOT353                                                              | (Note 5)      |                | 143  |      | °C/W |  |

|                   | Junction-to-Case                          | DFN1410                                                             | (Note 5)      |                | 190  |      |      |  |

Over recommended free-air temperature range (unless otherwise noted)

Note: 5. Test condition for SOT25, SOT353, and DFN1410: Device mounted on FR-4 substrate PC board, 2oz copper, with minimum recommended pad layout.

## SINGLE 2 INPUT POSITIVE NAND GATE

## **Switching Characteristics**

| Parameter       | From    | то          | ± 0.1V |     | V Vcc = 1.8 V Vcc = 2.5 V<br>± 0.15V ± 0.2V |     | Vcc = 3.3 V<br>± 0.3V |     | Vcc = 5 V<br>± 0.5V |     | Unit |     |    |

|-----------------|---------|-------------|--------|-----|---------------------------------------------|-----|-----------------------|-----|---------------------|-----|------|-----|----|

| i urumeter      | (Input) | t) (OUTPUT) | Min    | Max | Min                                         | Max | Min                   | Max | Min                 | Мах | Min  | Мах | •  |

| t <sub>pd</sub> | A or B  | Y           | 2.2    | 7.2 | 1.5                                         | 5   | 0.6                   | 3.5 | 0.6                 | 3.1 | 0.7  | 3   | ns |

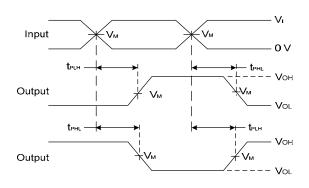

Over recommended free-air temperature range, CL = 15pF (see Figure 1)

Over recommended free-air temperature range, CL = 30 or 50pF as noted (see Figure 2)

| Parameter       | rameter From TO |            |     |     |     | Vcc = 2.5 V<br>± 0.2V |     | Vcc = 3.3 V<br>± 0.3V |     | Vcc = 5 V<br>± 0.5V |     | Unit |    |

|-----------------|-----------------|------------|-----|-----|-----|-----------------------|-----|-----------------------|-----|---------------------|-----|------|----|

| randicier       | (Input)         | ) (OUTPUT) | Min | Max | Min | Max                   | Min | Max                   | Min | Max                 | Min | Max  | •  |

| t <sub>pd</sub> | A or B          | Y          | 3.1 | 9   | 2.1 | 6.3                   | 1   | 4.4                   | 0.8 | 3.8                 | 0.9 | 3.6  | ns |

### **Operating Characteristics**

#### $T_A = 25 \ ^{o}C$

| Р               | Parameter Test<br>Conditions        |            | Vcc = 1.5 V | Vcc = 1.8 V | Vcc = 2.5 V | Vcc = 3.3 V | Vcc = 5 V | Unit |

|-----------------|-------------------------------------|------------|-------------|-------------|-------------|-------------|-----------|------|

|                 |                                     | Conditions | TYP         | ТҮР         | ТҮР         | ТҮР         | ТҮР       | •    |

| C <sub>pd</sub> | Power<br>dissipation<br>capacitance | f = 10 MHz | 22          | 22          | 22          | 23          | 25        | pF   |

## SINGLE 2 INPUT POSITIVE NAND GATE

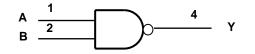

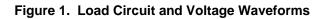

#### **Parameter Measurement Information**

| Vcc        | Inputs          |                                | Ver                | C    | Р.  |  |

|------------|-----------------|--------------------------------|--------------------|------|-----|--|

| VCC        | VI              | t <sub>r</sub> /t <sub>f</sub> | V <sub>M</sub>     | CL   | RL  |  |

| 1.5V±0.10V | V <sub>cc</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 15pF | 1MΩ |  |

| 1.8V±0.15V | V <sub>cc</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 15pF | 1MΩ |  |

| 2.5V±0.2V  | V <sub>cc</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 15pF | 1MΩ |  |

| 3.3V±0.3V  | 3V              | ≤2.5ns                         | 1.5V               | 15pF | 1MΩ |  |

| 5V±0.5V    | V <sub>CC</sub> | ≤2.5ns                         | V <sub>CC</sub> /2 | 15pF | 1MΩ |  |

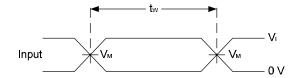

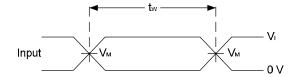

Voltage Waveform Pulse Duration

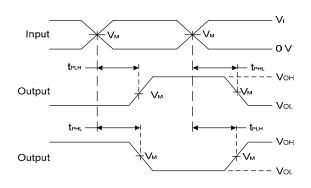

#### Voltage Waveform Propagation Delay Times Inverting and Non Inverting Outputs

Notes: A. Includes test lead and test apparatus capacitance.

- B. All pulses are supplied at pulse repetition rate  $\leq$  10 MHz.

- C. Inputs are measured separately one transition per measurement.

- D.  $t_{\mathsf{PLH}}$  and  $t_{\mathsf{PHL}}$  are the same as  $t_{\mathsf{PD}}$

## SINGLE 2 INPUT POSITIVE NAND GATE

#### Parameter Measurement Information (Continued)

| Vcc        | Inp             | outs                           | V <sub>M</sub>     | CL   | RL   |  |

|------------|-----------------|--------------------------------|--------------------|------|------|--|

|            | Vı              | t <sub>r</sub> /t <sub>f</sub> | - 141              | υĽ   |      |  |

| 1.5V±0.10V | V <sub>cc</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 30pF | 1KΩ  |  |

| 1.8V±0.15V | V <sub>CC</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 30pF | 1KΩ  |  |

| 2.5V±0.2V  | V <sub>cc</sub> | ≤2ns                           | V <sub>CC</sub> /2 | 30pF | 500Ω |  |

| 3.3V±0.3V  | 3V              | ≤2.5ns                         | 1.5V               | 50pF | 500Ω |  |

| 5V±0.5V    | V <sub>CC</sub> | ≤2.5ns                         | V <sub>CC</sub> /2 | 50pF | 500Ω |  |

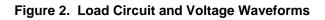

Voltage Waveform Pulse Duration

#### Voltage Waveform Propagation Delay Times Inverting and Non Inverting Outputs

Notes: A. Includes test lead and test apparatus capacitance.

- B. All pulses are supplied at pulse repetition rate ≤ 10 MHz.

- C. Inputs are measured separately one transition per measurement.

- D.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{PD}$ .

## SINGLE 2 INPUT POSITIVE NAND GATE

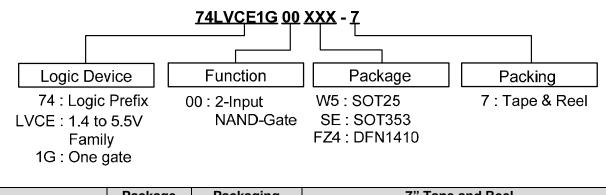

### **Ordering Information**

|             | Device          | Package | Packaging | 7" Tape and Reel |                    |  |

|-------------|-----------------|---------|-----------|------------------|--------------------|--|

|             | Device          | Code    | (Note 5)  | Quantity         | Part Number Suffix |  |

| РЪ,         | 74LVCE1G00W5-7  | W6      | SOT25     | 3000/Tape & Reel | -7                 |  |

| <b>Pb</b> , | 74LVCE1G00SE-7  | SE      | SOT353    | 3000/Tape & Reel | -7                 |  |

| РЪ,         | 74LVCE1G00FZ4-7 | FZ4     | DFN1410   | 5000/Tape & Reel | -7                 |  |

Note: 6. Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at http://www.diodes.com/datasheets/ap02001.pdf.

## SINGLE 2 INPUT POSITIVE NAND GATE

### **Marking Information**

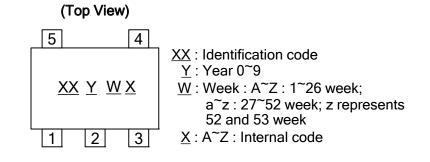

#### (1) SOT25 and SOT353

| Part Number  | Package | Identification Code |

|--------------|---------|---------------------|

| 74LVCE1G00W5 | SOT25   | PS                  |

| 74LVCE1G00SE | SOT353  | PS                  |

(3) DFN1410

## (Top View)

| Part Number   | Package | Identification Code |

|---------------|---------|---------------------|

| 74LVCE1G00FZ4 | DFN1410 | PS                  |

## SINGLE 2 INPUT POSITIVE NAND GATE

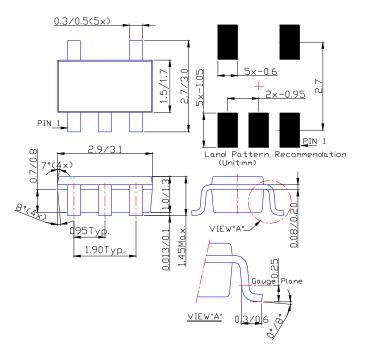

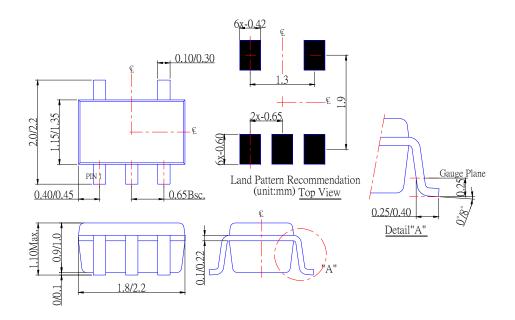

### Package Outline Dimensions (All Dimensions in mm)

#### (1) Package Type: SOT25

### (2) Package Type: SOT353

NEW PRODUCT

## SINGLE 2 INPUT POSITIVE NAND GATE

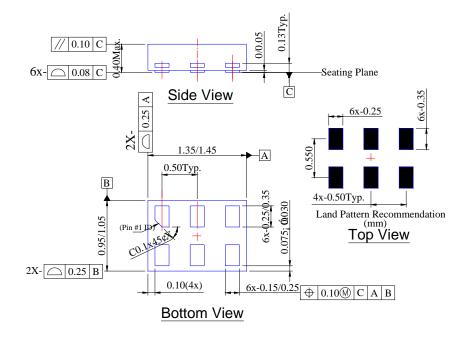

## Package Outline Dimensions (Continued)

#### (3) Package Type: DFN1410

## SINGLE 2 INPUT POSITIVE NAND GATE

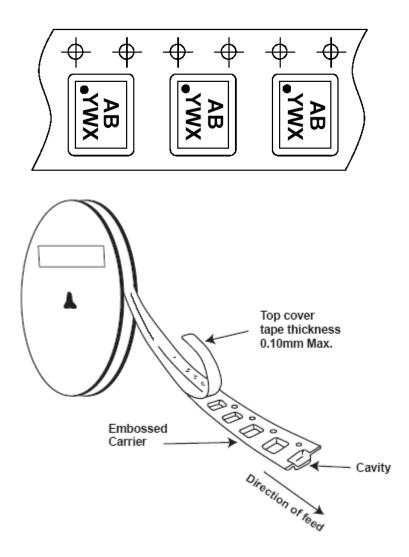

### **Taping Orientation (Note 7)**

#### For DFN1410

### SINGLE 2 INPUT POSITIVE NAND GATE

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products or systems.

Copyright © 2010, Diodes Incorporated

www.diodes.com